1

Предлагаемое изобретение относится к области автоматики и вычислите льной техники, а именно: к множительно-делительным устройствам.

Известно множительно-делительное устройство, содержащее интеграторы, компаратор; вход которого соединен с выходом интегратора, переключатели 1.

Недостатком этого устройства является сложность.

Наиболее близким к предлагаемому изобретению является . множительно-делительное устройство, содержащее интегратор, вход которого соединен с щиной первого аналогового сигнала, а выход - с одним из входов компаратора, выход koMuapaTopa соединен с управляющими входами двух переключателей, входы которых соединены соответственно с шинами других входов, а выход одного из них - с другим входом интегратора, а также времязадающее устройство и управляемый источник тока 2.

В этом устройстве формируется и подается на вход интегратора импульс обратной связи заданной длительности и амплитуды.

Недостатком известного устройства является его сложность, обусловленная необходимостью применения сложных прецизионHbix устройств, формирующих импульсы заданной формы, амплитуды и длительности.

Целью изобретения является упрощение , устройства.

Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее интегратор, первый вход которого соединен с источником первого сомножителя, а выход - с первым входом компаратора, выход которого соединен с управляющими входами первого и второго переключателей, информационные входы которых соединены соответственно с источником второго сомножителями источником делителя, выход второго ключа соединен со вторым

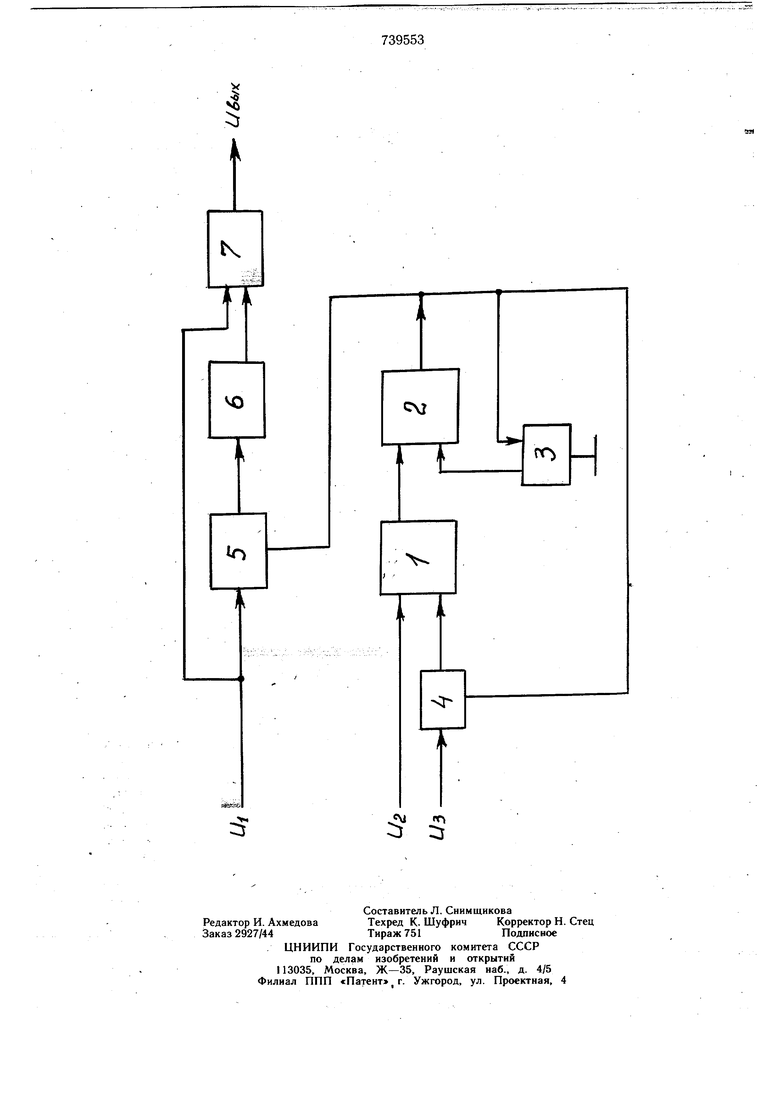

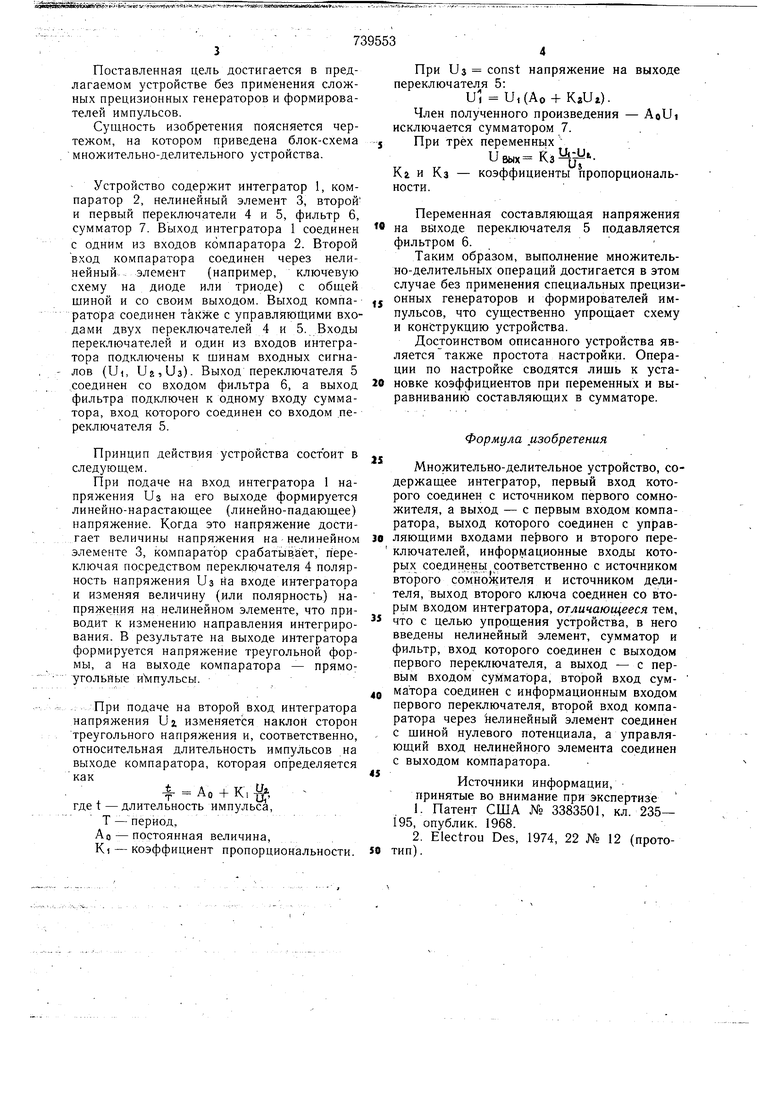

15 входом интегратора, введены нелинейный элемент, сумматор и фильтр, вход которого соединен с выходом первого переключателя, а выход - с первым входом сумматора, второй вход сумматора соединен с информационным входом первого переключателя, второй вход компаратора через нелинейный элемент соединен с шиной нулевого потенциала, а управляющий вход нелинейного элемента соединен с выходом компаратора. Поставленная цель достигается в предлагаемом устройстве без применения сложных прецизионных генераторов и формирователей импульсов. Сущность изобретения поясняется чертежом, на котором приведена блок-схема множительно-делительного устройства. Устройство содержит интегратор 1, компаратор 2, нелинейный элемент 3, второй и первый переключатели 4 и 5, фильтр 6, сумматор 7. Выход интегратора 1 соединен с одним из входов компаратора 2. Второй вход компаратора соединен через нелинейный, элемент (например, ключевую схему на диоде или триоде) с общей щиной и со своим выходом. Выход компаратора соединен тйкже с управляющими входами двух переключателей 4 и 5. Входы переключателей и один из входов интегратора подключены к щинам входных сигна- лов (IJi, UjiUa). Выход переключателя 5 соединен со входом фильтра 6, а выход фильтра подключен к одному входу сумматора, вход которого соединен со входом переключателя 5. Принцип действия устройства состоит в следующем. При подаче на вход интегратора 1 напряжения Us на его выходе формируется линейно-нарастающее (линейно-падающее) напряжение. Когда это напряжение достигает величины напряжения на нелинейном элементе 3, компаратор срабатывает. Переключая посредством переключателя 4 полярность напряжения Us на входе интегратора и изменяя величину (или полярность) напряжения на нелинейном элементе, что приводит к изменению направления интегрирования. В результате на выходе интегратора формируется напряжение треугольной формы, а на выходе компаратора - прямоугольные пульсы. -При подаче на второй вход интегратора напряжения Uj, изменяется наклон сторон треугольного напряжения и, соответственно, относительная длительность импульсов на выходе компаратора, которая определяется как 4- АО + К, , где t - длительность импульса, Т - период, АО - постоянная величина, Ki - коэффициент пропорциональности.

739553 При Us const напряжение на выходе переключателя 5: Ul U,(Ao-f KaUi). Член полученного произведения - AoUi исключается сумматором 7. При трёх переменных V ивых КзЦ}У Кг и Кз - коэффициенты пропорциональности. Переменная составляющая напряжения на выходе переключателя 5 подавляется фильтром 6. Таким образом, выполнение множительно-делительных операций достигается в этом случае без применения специальных прецизионных генераторов и формирователей импульсов, что существенно упрощает схему и конструкцию устройства. Достоинством описанного устройства является также простота настройки. Операции по настройке сводятся лищь к установке коэффициентов при переменных и выравниванию составляющих в сумматоре. Формула изобретения Множительно-делительное устройство, содержащее интегратор, первый вход которого соединен с источником первого сомножителя, а выход - с первым входом компаратора, выход которого соединен с управляющими входами и второго переключателей, информационные входы которых соединень соответственно с источником второго сомножителя и источником делителя, выход второго ключа соединен со вторым входом интегратора, отличающееся тем, что с целью упрощения устройства, в него введены нелинейный элемент, сумматор и фильтр, вход которого соединен с выходом первого переключателя, а выход - с первым входом сумматора, второй вход сумматора соединен с информационным входом первого переключателя, второй вход компаратора через нелинейный элемент соединен с щиной нулевого потенциала, а управляющий вход нелинейного элемента соединен с выходом компаратора. Источники информации, принятые во внимание при экспертизе . 1. Патент США № 3383501, кл. 235- 195, опублик. 1968. 2. Electron Des, 1974, 22 № 12 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Множительное устройство | 1979 |

|

SU860086A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2110091C1 |

| Множительно-делительное устройство | 1975 |

|

SU568056A1 |

| Множительно-делительное устройство | 1978 |

|

SU723596A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

Л

VO

to

«М

I

Vv

Авторы

Даты

1980-06-05—Публикация

1978-01-09—Подача