(54) УПРАВЛЯЕМЫЙ РАСПРЕДЕЛИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

| Устройство для контроля регистров сдвига | 1980 |

|

SU924759A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Устройство для передачи цифровой информации | 1981 |

|

SU1021010A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

1

Изобретение относится к автомати-i ке и вычислительной технике, в частности к устройствам распределения импульсных сигналов и может быть использовано в управляющих устройствах ЦВМ, а также в устройствах управления.

Наиболее целесообразно его использование в устройствах, требующих многократного распределений сигнапбв с . исключением каналов, запрещенных для использования.

Известны распределители импульсов, основанные на использовании сдвигающих регистров и содержащие в каждом разряде триггеры и логические эле- 15 менты 1 и 2, Они обеспечивают распределение импульсных сигналов и установленной временной последовательности по всем выходным каналам. Эта же временная последовательностьсо- 20 храняется я в том случае, когда с помощью внешнего пpoгpaммиps oиeгo устройства ;осуществляется запрет на йспольэов ание, некоторых каналов, а следовательно, неэффективно использу-25 ется цикл распределения.

Наиболее близким техническим решением к данному изобретению является управляемый распределитель, в кгикдом разряде которого содержатся триг-3.0

геры и элементы И, причем прямой и инверсный выходы дополнительного триггера подключены к первым входам соответственно первого и второго элементов и, втоЕме входы которых под- ключены ко входу оазряда распределителя, выход первого элемента И подключен к информационному входу основноготриггера, прямой выход которого является выходом разряда 3,

Недостатком такого распределителя, ухудшающим его эксплуатационные характеристики, является невозможность многократного (циклического) распределения без использования внешних элементов памяти,восстанавливающих программу после каждого цикла распределения .

Кроме того, необходимоть восстановления программы снижает бьжзтродействие устройства.

: Цель изобретения - улучшение эксплуатационных характеристик и повышение быстродействия распределителя.

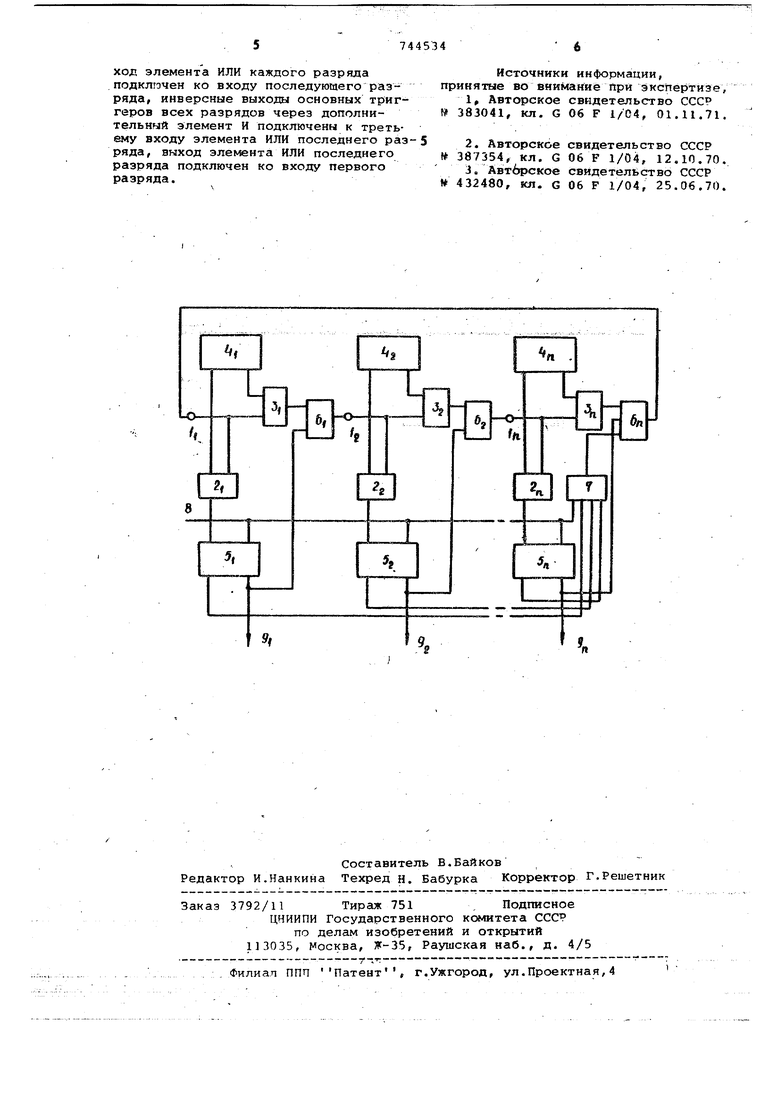

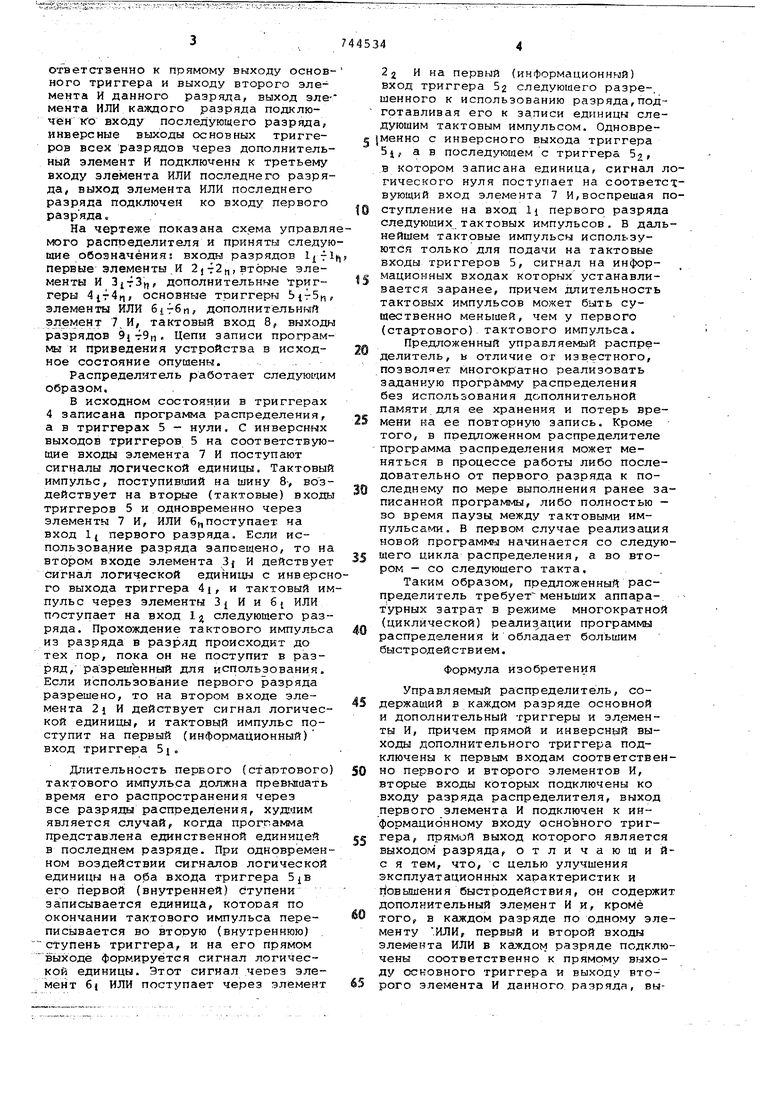

Поставленная цель достигается тем, что распределитель .содержит дополнительный элемент Ни, кроме того, в каждом разряде по одному элементу ИЛИ, первый и второй входы элемента ИЛИ в каждом разряде полключг;ны соответстэенно к прямому выходу основ ного триггера и выходу второго элемента И данного разряда, выход эле мента ИЛИ каждого разряда подключён КО входу последующего разряда, инверсные выходы основных триггеров всех разрядов через дополнительный элемент И подключены к третьему входу элемента ИЛИ последнего разряда, выход элемента ИЛИ последнего разряда подключен ко входу первого разряда с На чертеже показана схема управля мого распределителя и приняты следую щие обозначения; входы разрядов первые элементы И 2j-:2n, вторые элементы И 3|тЗ,, дополнительные триггеры , основные триггеры элементы ИЛИ 6if6n; дополнительный элемент 7.И, тактовый вход 8, выходы разрядов 91т9п. Цепи записи программы и приведения устройства в исходное состояние опущены. Распределитель работает следуюЕчим образом, В исходном состоянии в триггерах 4 записана программа распределения, а в триггерах 5 - нули. С инверсных выходов триггеров 5 на соответствующие входы элемента 7 И поступают сигналы логической единицы. Тактовый импульс, поступивтш1й на шину 8 воздействует на вторые (тактовые) входы триггеров 5 и одновременно через элементы 7 И, ИЛИ 6,поступает на вход 1| первого разряда. Если использование разряда эапсешено, то на втором входе элемента 3j И действует Сигнал логической единицы с инверсн го выхода триггера 4j, и тактовый им пульс через элементы 3j И и 6( ИЛИ поступает на вход 1 следующего разряда. Прохождение тактового импульса из разряда в разряд происходит до тех пор, пока он не поступит в разряд, разрешенный для использования. Если использование первого разряда разрешено, то на втором входе элемента 2i И действует сигнал логической единицы, и тактовый импульс поступит на первый (информационный) вход триггера St. Длительность первого (стартового тактового импульса должна превышать время его распространения через все разряды распределения, худгчим является случай, когда прогпамма представлена единственной единицей в последнем разряде. При одновремен ном воздействии сигналов логической единицы на оба входа триггера его первой (внутренней) ступени записывается единица, которая по окончании тактового импульса переписывается во вторую (внутреннюю) ступень триггера, и на его прямом выходе формируется сигнал логической единицы. Этот сигнал через эле;мент 6i ИЛИ поступает через элемент 22 И на первый (информационный) вход триггера 52 следующего разре-, шенного к использованию разряда,подготавливая его к за.писи единицы следующим тактовым импульсом. ОдновреMeHHo с инверсного выхода триггера 5i, а в последующемс триггера 52, в котором записана единица, сигнал логического нуля поступает на соответствующий вход элемента 7 И,воспрещая поступление на вход li первого разряда следующих тактовых импульсов, в дальнейшем тактовые импульсы используются только для подачи на тактовые входы триггеров 5, сигнал на информационных входах которых устанавливается заранее, причем длительность тактовых импульсов может быть существенно меньшей, чем у первого (стартового) тактового импульса. Предложенный управляемый распределитель, ь отличие от известного, позволяет многократно реализовать заданную программу распределения без использования дополнительной памяти для ее хранения и потерь времени на ее повторную запись. Кроме того, в предложенном распределителе программа распределения может меняться в процессе работы либо последовательно от первого разряда к последнему по мере выполнения ранее записанной программы, либо полностью - 30 время паузы, между тактовыми импульсами. В первом случае реализация новой программы начинается со следующего цикла распределения, а во втором - со следующего такта. Таким образом, предложенный распределитель требует меньших аппаратурных затрат в режиме многократной (циклической) реализации программы распределения иобладает большим быстродействием. Формула изобретения Управляемый распределитель, содержащий в каждом разряде основной и дополнительный триггеры и эл.ементы И, причем прямой и инверсный выходы дополнительного триггера подключены к первым входам соответственно первого и второго элементов И, вторые входы которых подключены ко входу разряда распределителя, выход первого элемента И подключен к информационному входу основного триггера, прямой выход которого является выходом разряда, отличающийс я тем, что, с целью улучшения эксплуатационных характеристик и повышения быстродействия, он содержит дополнительный элемент И и, кроме того, в каждом разряде по одному элементу .ИЛИ, первый и второй входы элемента ИЛИ в каждо и разряде подключены соответственно к прямому выходу основного триггера и выходу второго элемента И данного разряда, выход элемента ИЛИ каждого разряда подключен ко входу последующего разряда, инверсные выходы основных триггеров всех разрядов через дополнительный элемент И подключены к третьему входу элемента ИЛИ последнего разряда, выход элемента ИЛИ последнего разряда подключен ко входу первого разряда.

Источники информации, принятые во внимание при экспертизе,

383041, кл. G 06 F 1/04, 01.11.71.

№ 387354, кл. G 06 F 1/04, 12.10.70.

W 432480, кя. G 06 F 1/04, 25.06.70.

9(

Авторы

Даты

1980-06-30—Публикация

1976-04-05—Подача