(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУПРОВОДНИКОВОЙ ПАМЯТЬЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления для запоминающего устройства | 1977 |

|

SU723679A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Динамическое оперативное запоминающее устройство | 1981 |

|

SU1003142A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Устройство для управления полупровод-НиКОВыМ НАКОпиТЕлЕМ | 1979 |

|

SU842811A1 |

| Устройство для регенерации динамической памяти | 1987 |

|

SU1434497A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| МОЛЕКУЛЯРНО-ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2068586C1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

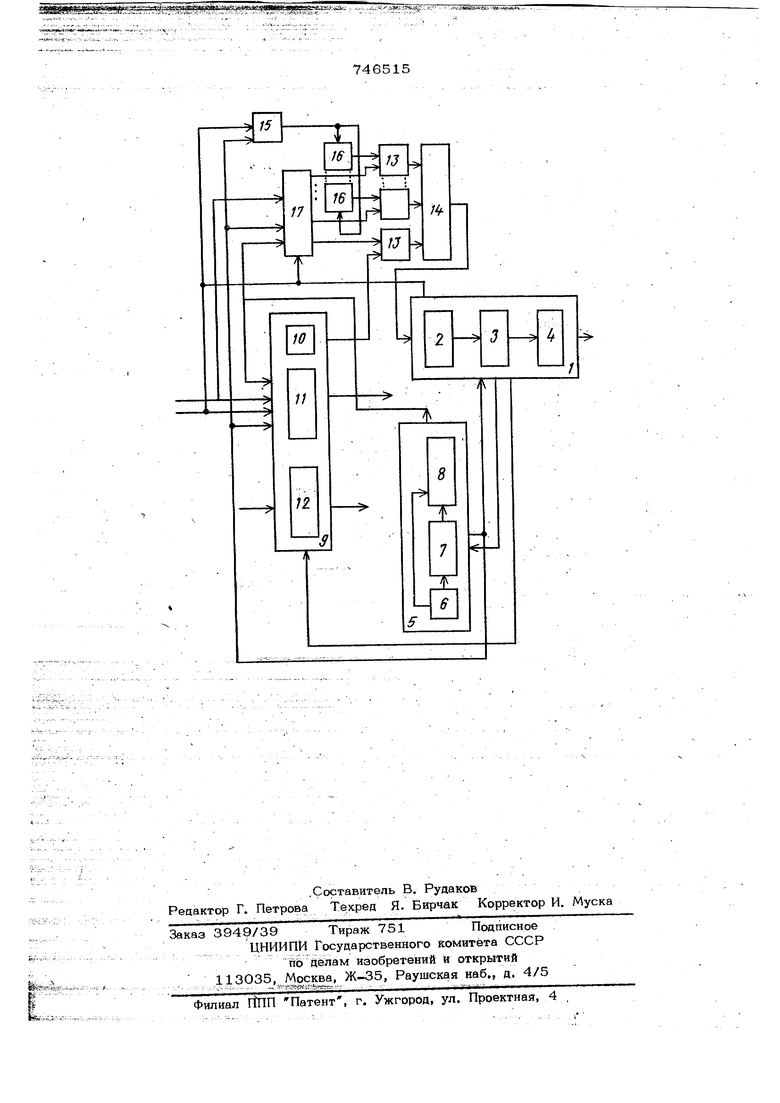

Изобретение относится к области циф ровых вычислительных машин, может быть использовансэ в полупроводниковых запоминающих устройствах (ЗУ) на МДП транзисторах. Известно устройство, которое предназначено для формирования определен- ной последовательности выходных управляющих сигналов, необходимых для ра- боты запоминающих элементов на МДП- транзисторах ij, При этом оно может быть применено в ЗУ, содержащем ячейки памяти на МДП - транзисторах только одного типа, обладающих одинаковой предельной частотой работы и требующих одинаковую последовательность и длительность управляющих сигналов. Известно также устройство для управ ления полупроводниковой памятью, содержащее блок ввода - вывода информации и блок регенерации информации, подключенные к блоку управления 2|. В этом устройстве задается жесткая последовательность и фиксированные па.раметры выходных управляющих сигналов, настроенные на один рпреде.ленный тип ячейки памяти. При этом изменить па эаметры, также как и изменить последовательность управляющих сигналов невозможно без технологического вмешательства в устройство для управления памятью. При выполнении устройства в виде больщих интегральных схем (БИС) такое вмещательство практически невозможно, а поэтому любая разработка накопителя на ячейках памяти, выполненных на МДП - транзисторах с новой временной диаграммой их работы, требует разработки нового типа ЕИС устройства управления, что серьезно сказывается на сроках и стоимости разработки. Недостатками известного устройства являются отсутствие автоматической настройки параметров выходных управляющих сигналов и невозможность унификации устройства для накопителей с различными временными диаграммами рабо ты ячеек памяти, что существенно снижает область применения устройства. Целью изобретения является расширение области применения устройства за счет обеспечения возможности автоматической перестройки параметров управляю щих импульсов. Поставленная цель достигается тем, что устройство содержит элементы И и ИЛИ, генераторы импульсов и блок мест ного управления, первый и второй входы которого подключены к соответствующим входам блока ввода - вывода информации, третий и четвертый входы - к выхо дам блока регенерации информации, выходы блока местного управления соедйне Hbi с одними из входов элементов И, дру гие входы которых подключены к выхода генераторов импульсов, а выходы через первый элемент ИЛИ - к входу блока управления, входы feHepafopoBTiKJnyJrb- сов соединены с выходом второго элемен та ИЛИ, входы которого подключены к одному из входов блока ввода - вывода информации и четвертому входу блока : местного управления. На чертеже изображена блок-схема предложенного устройства. Устройство содержит блок 1 управления, в состав которого входят счетчик 2 тактовых импульсов, дешифратор 3 тактовых импульсов, Узел 4 формирования и выдачи управляющих сигналов; блок 5 регенерации информации, в состав которого включаются генератор 6 регенерации, узел 7 управления регенерации, счетчик 8 адресов регенерации; блок 9 ввода - вывода, состоящий из генератора 10 тактовых импульсов, регистра 11 адреса и регистра 12 слова, элементы И 13, первый 14 и второй 15 элементы ИЛИ, генераторы 16 импульсов и блок 17 местного утфавления. Первый и второй входы блока 17 под ключены к соответствующим входам блока 9, выходы соединены с одними из входов элементов И 13, другие входы которых подключены к выходам генерато ров 16 импульсов, а выходь череё элемент ИЛИ 14 - к входу блока 1. Входы генераторов 16 импульсов соединены с выходом элемента ИЛИ 15, входы котор го подключены к одному из входов блока 9 и четвертому входу блока 17. В устройстве вместо генераторов 16 могут быть применены соответствующие схемы деления или умножения частоты генератора, я в качестве блока 17 воз

16515 можно использование дешифратора кода адреса.. Работу устройства рассмотрим на примере формирования выходных управляющих сигналов в режиме записи для двух типов накопителей, кристаллы которых отличаются по частотным свойствам. При обращении к устройству по. сигналу обращение запускаются генераторы 16 и 1О. При этом код адреса запоминается на регистре 11 адреса. В соответствии с определенными разрядами кода адреса , на одном из выходов блока 17 появляется управляющий сигнал, который подключает соответствующий генератор 16 через элемент ИЛИ 14, на вход блока 1 управления. Для выполнения одного из режимов, например, записи,на другой вход блока 1 и второй вход блока 17 поступает сигнал запись. Тактовые импульсы,, поступающие на вход блока It запускают счетчик 2 тактовых импульсов, выгодные сигналы счетчика дешифрируются дешифратором 3, при этом на каждом из выходов дешифратора формируетсй последовательность тактовых импульсов, сдвинутая во времени относительно последовательности на любом другом выходе дешифратора. Узел 4 воспринимает определённые импульсы ни выходах дешифратора 3 и формирует управляющие сигналы, поступающие на выход устройства, а также синхронизирующие сигналы, поступающие на входы блоков 5 и 9, Код слова поступает на входы блока 9, запоминается на регистре 12 слова и выдается на выходы устройства при наличии соответствующего сигнала на одном из управляющих входов. При обращении по адресу другого накопителя, ячейки памяти которого требуют для своей работы Другой диаграммы, блок 17 в соответствии с кодом адреса вырабатывает управляющий сигнал на соответствующем выходе и подключает соответствующий генератор 16 на вход блока 1, Так как частота тактовых импульсов на входе блока 1 изменилась по сравнению с предыдущим обращением, то естественно изменяются и параметры выходных управляющих сигналов, В режиме регенерации информации генератор 6 блока 5 выдает управл яющие сигналы, указывающие на необходимость регенерации информации, так как в ячей ках памяти динамического типа, выполненных на МДП-транзисторах, информа|ция сохраняется ограниченное время (например, 2 млс) и ее необходимо восстанавливать каждые 2 млс. Этот сигнал, запускает узел 7 управления регенерацией и счетчик,8 адресов регенерации, кбторый изменяет свое состояние на единицу после каждого цикла регенерации, а также запускает генератор 10 и через элемент ИЛИ 15 генераторы 16. В соот ветствии с кодом.адреса регенерации, поступающим на третий вход блока -17, на его соответствующем выходе вырабатывается сигнал, который через элементы И 13 и ИЛИ. 14 подключает соответствую щий генератор 16 на вход блока 1 для формирования временной диаграммы работы устройства в режиме регенераций. Код адреса регенерации поступает также ша входы блока 9, где заносится на регистр адреса 11 при наличии управляющего сигнала на одном из его входов, который одновременно запрещает прием кода адреса на регистр 11 по другим входам в течение цикла регенерации. Так как управляющи:й сигнал регенерации по«. ступает на вход блока 1, то блок 1 выдает на его выход управляющие сигналы, параметры, последовательность поступрення которых соответствует режиму регенерации информации в ячейках памяти выб ранного накопителя. Таким образом, предложенное устройство обладает возможностью автоматической перестройки временной диаграммы,, то позволяет унифицировать его для полупроводниковых оперативных запоминающих устройств, накопители которых выполнены на ячейках памяти, требующих для своей работы различных временных диаграмм. Формула изобретения Устройство для управления полупроводников:ой памятью, содержащее блок ввода - вьгаода информации и блок регенерации информации, подключенные к блоку управления, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности автоматической перестройки параметров управляющих импульсов, оно содержит элементы И и ИЛИ, генераторы импульсов и блок местного управления, первый и второй входы которого подключены к соответствующим входам блока ввода - вьюода информации, третий и Четвертый ёходы - к выходам блока регенераций информации, выходы блока местного управления соединены с одним на входом элементов И, другие входы которых подключены; к выходам гёнераторой импульсов, а выходы через первый, элемент ИЛИ - к входу блока зтравления, входы генераторов импульсов соединены с с выходом второго элемента ИЛИ, входы которого подключены к однвму из входот (блокаввода - вывода информации и четвертому входу блока местного управления. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании 1311997, кл. G 11 С 7/00, 1973. 2.Старое Ф. Г., Крайзмер Л. П. По- упроводниковые запоминающие устройст- а. Л., Энергия, 1973, с. 64-76 (проотнп).17

t

1

Авторы

Даты

1980-07-05—Публикация

1977-07-15—Подача