Изобретение относится к вычислительной технике и может быть использовано автономно или в составе многопроцессорных вычислительных систем для увеличения производительности вычислений .

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения деления чисел, п вставленных в дополнительном коде.

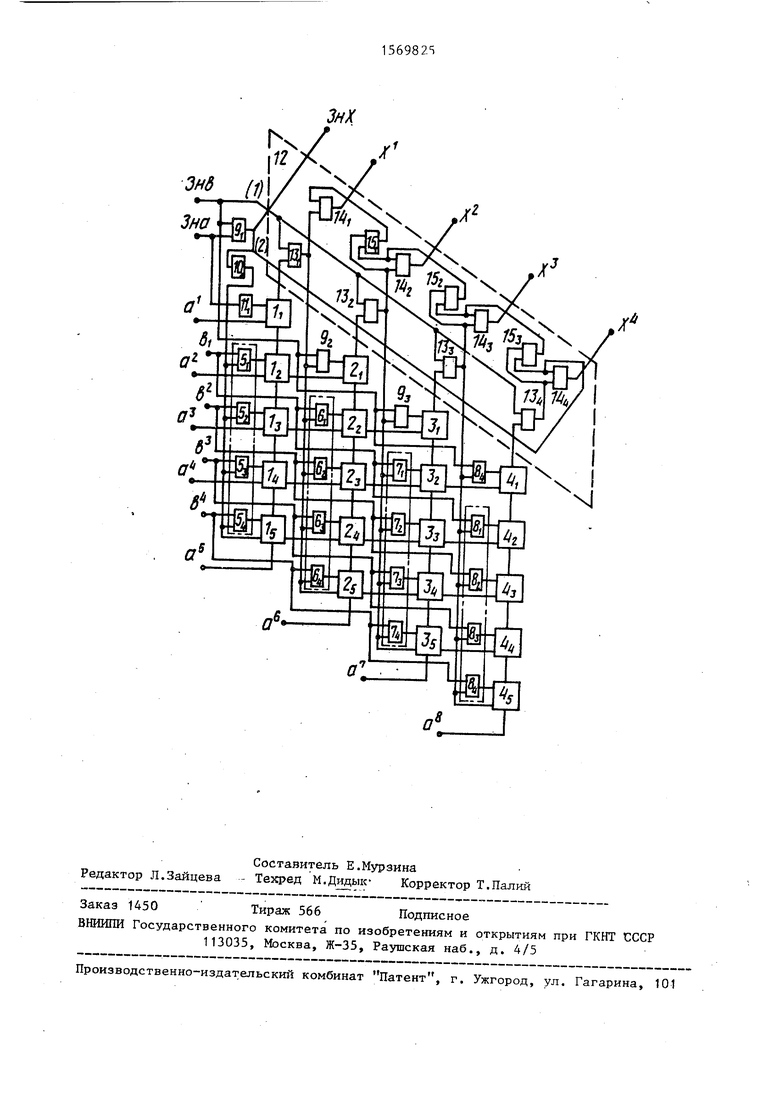

На чертеже представлена схема устройства для случая .

Устройство содержит четыре пятиразрядных параллельных сумматора 1., - 15- 4,-4, четыре пятиразрядных сумматора 5,,-S j. - 8, -8. по модулю два, группу из четырех элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 9,-9, два элемента НЕ 10

и 11 и блок 12 формирования цифр частного, который состоит из двух групп по четыре сумматора , . по модулю два в каждой, и группу из трех элементов И 15,-153.

Устройство работает следующим образом.

На вход устройства поступает делимое а, представленное знаковым разрядом Зна и разрядами а%а2 , . .. ,ае, и делитель Ь, представленный знаковым разрядом ЗнЬ и разрядами ,Ь3 и Ь. На выходе устройства частное

а.

представлено знаковым разрядом

D

Знх и разрядами х ,х2 ,х3 ,х. Вычислеание частного , где делимое а и деСд

К5

Q7

литель Ь представлены в дополнительном коде, выполняется следующим образом.

I

На первом параллельном сумматоре вычисляется невязка 6, в соответствии с выражением

{а-2 Ъ, если , .( а+2 Ь, если ,

где ® ЗнЬ.

I Значение первого (старшего) разряда частного х1 вычисляется как

х р ( © ЗнЪ © г

i

I

р - значение переноса из старшего разряда первого параллельного сумматора; г - двоичная переменная, величина которой вычисляется по рекуррентному выражению

г.(р2 Ј)ЗнЬ)г,.

| f W - ™-T/J.Ј.

На i-м параллельном сумматоре (i 2,3,...,п) вычисляется невязка Ј; в соответствии с выражением

На выходе элемента 10., и соответственно на вторых входах сумматора 5 1 логический О и, следовательно, зна 20 чения разрядов делителя поступают без инверсии на вторые входы од норазрядных сумматоров . На вто рой вход разряда поступает величи на Зна. На первые входы разрядов 1,- 1S поступает код 10000. На вход пере носа разряда 1 поступает значение

3. сг

Сумматор 14-15 производит суммирование

)

10000 - код на первых входах разрядов 1,-15

С: t

2Ј- , если р -1 © ЗнЬ 1;

-

2Ј.и , если р1М©ЗнЬ 0. Значение 1-го разряда частного- вычисляется как

© ЗнЬ ©г; ; (,3,...,п),

где г;(рн ©ЗнЬ)г.н , . Пример. Пусть делимое а и делитель Ь представлены в дополнительном коде и равны

а а2аэафа5а6а7а8 0.10001111; Ь ЬгЪ3Ь 1.0011. 5 На выходе элемента 9, получают знак частного © .

На выходе элемента 10., и соответственно на вторых входах сумматора 5 1 логический О и, следовательно, зна- 0 чения разрядов делителя поступают без инверсии на вторые входы одноразрядных сумматоров . На второй вход разряда поступает величина Зна. На первые входы разрядов 1,- 1S поступает код 10000. На вход переноса разряда 1 поступает значение

3. сг

Сумматор 14-15 производит суммирование

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1667077A1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

| Устройство для деления | 1989 |

|

SU1633395A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Устройство для деления | 1988 |

|

SU1621034A1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| Матричное устройство для деления | 1983 |

|

SU1141402A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

Изобретение относится к вычислительной технике и может быть использовано автономно или в составе вычислительной системы для увеличения производительности вычислений. Целью изобретения является расширение функциональных возможностей за счет выполнения деления чисел, представленных в дополнительном коде. Новым в устройстве, содержащем N N-разрядных параллельных сумматоров и N N-разрядных сумматоров по модулю два, является введение N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, двух элементов НЕ и блока формирования цифр частного. Это дает возможность организовать структуру устройства, удобную для применения в качестве быстродействующего спецпроцессора в составе вычислительных систем, и реализовать его в виде большой интегральной схемы. 1 з.п. ф-лы, 1 ил.

10011 - код на вторых + 1 - значение а,100100 - код на выходе разрядов 1,,-15.

На выходе разрядов 1,-15 появляется величина невязки Ј,00100. На выходе переноса старшего разряда 1( - величина переноса . Значение р 1 поступает на вход сумматора 13 по модулю два, на выходе которого образуется величина р1 © , поступающая на второй вход элемента 9if на вторые входы сумматоров 6 и на пер- вый вход разряда 25 параллельного сумматора .

Таким образом, на первые входы разрядов поступает незязка 6,

01000 - код на первых входах разрядов +

10011 - код на вторых входах разрядов + 1 - значение аб

11100 - код на выходе разрядов .

Таким образом, Ј2 11100; . Значение переноса р2 0 поступает на

входах разрядов 1,-lj

структурно сдвинутая на один разряд в сторону старших разрядов (что эквивалентно умножению на 2) - код 0100. На вторые входы разрядов поступают значения разрядов делителя, сдвинутые структурно на один разряд в сторону младших разрядов (что эквивалентно умножению на ) - код 10011. На вход переноса разряда 2S поступает величина а 1.

На выходе сумматора формируется величина невязки Е& и переноса р2 из старшего разряда 2,:

вход сумматора 13Z по модулю два, нг выходе которого образуется величина

р2 ® . Значения разрядов делителя ЗнЬ. Ь(Ь2Ь3ЬФ 1.0011 инвертируют- ся на элементе 93 и сумматоре 7. На вторые входы разрядов сумматора поступает код 01100. На первые входы

11001 - код на первых входах разрядов +

01100 - код на вторых входах разрядов + 1 - величина ат

100110 - код на выходе разрядов 3,-Зд.

Таким образом, 00110$ . Значение р3 1 поступает на вход сумматора 13 по модулю два, где образуется величина р3 б , поступающая на второй вход элемента 9/±, вторые входы сумматора 8 и на первый вход разряда Ь5. На первые входы разрядов

01100 - код на первых входах разрядов 4 ,-4

10011 - код на вторых входах разрядов 4,-4s; + 1 - величина ай

100000 - код на выходе разрядов 4ч-45.

Таким образом, 00000; . значение р 1 поступает на вход сум- .чтора 13 по модулю два, где образуется величина р © , поступающа s-га вход сумматора 14 по модулю два. На выходе сумматора 14 формируется яь-ь-чение младшего разряда частного

. 4© ЗнЬ .

. На выходе элемента-И 15 формиру- а-. ся значение двоичной переменной

. г3( ЗнЬ).

Беличина г3 поступает на первый вход сумматора 143 по модулю дваэ на выходе которого образуется значение разряда х3

© ЗнЬ .

На выходе элемента И 152 формируется величина

г(р3 @ЗнЪ).

Аналогично, на выходе сумматора 14.г по модулю два формируется значение © ЗнЬ +

на выходе элемента И 15,- величи-

©ЗнЬ), на выходе сумматора 14, по модулю два значение старшего разряда частного (© ЗнЬ © г, 0.

разрядов поступает величина , на первый вход разряда 3 - величина р2 © .

Сумматор 5-формирует значения разрядов невязки 53И переноса р3:

41-4ч. поступают разряды величины код 0110. На вторые входы разрядов - неинвертированные значения разрядов делителя ЗиЪ Ъ Ъ2Ъ3Ъ. Сум-- матор ,j- формирует значения не- вязки Ј,к переноса р4:

5

Таким образом, получены значения 30 разрядов частного х:

Знх х х2х3х4 1.0101.

0

Формула изобретения

5

щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения деления чисел, представленных в дополнительном коде, в него введены группа из п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента НЕ и блок формирования цифр частного, причем вход знака делителя устройства соединен с первым входом j-ro элемен- та ИСКЛЮЧАЮЩЕЕ ИЛИ группы и первым управляющим входом блока формирования цифр частного, второй управляющий вход которого соединен с выходом знака частного устройства, входом первого элемента НЕ и выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, второй вход которого соединен с входом Знака делимого устройства и входом ёторого элемента НЕ, выход которого соединен с вторым входом первого разряда первого .параллельного сумматора, первый вход (п+1)-го разряда которого соединен с вторым входом j-ro разряда первого сумматора по модулю два и выходом первого элемента НЕ, выход k-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (k-2, 3,...,п) соединен соответственно с вторым входом первого разряда k-ro параллельного сумматора, .выход пере- носа первого разряда j-ro параллельного сумматора соединен соответственно с j-м информационным входом блока формирования цифр частного, j-й информационный выход которого соединен соответственно с выходом j-ro разряда частного устройства, m-й управляющий выход (,...,п-1) блока формирования цифр частного соединен соответственно с вторым входом (га+17-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторым входом каждого j-ro разряда (га+1)-го сумматора по модулю два и первым входом (п+1)-го разряда (т+1)-го параллельного сумматора.

днд

| Устройство для деления | 1985 |

|

SU1317431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Параллельные вычислительные структуры на основе разрядных методов вычислений | |||

| - Киев; Наукова думка, 1987, с.52 | |||

| рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-21—Подача