1

Изобретение относится к вычислительной технике, в частности к устройствам управления ЭВМ.

Известно г шкропрограммное устрой- j ство управления, содержащее два запо.минающих блока, регистры адресов, .элементы Ир.}.

Недостатком .указанного .устройства является сложность.10

Наиболее близким к предлагаемому . устройству по технической сущности является микропрограммное устройство управ гения, содержащее триггер, элементы И, коммутатор,первнй и fs второй выходы которого подключены .ко входам первой и второй групп элементов, каждая из которых состоит из последовательно соединенных регистра ресов и запоминающего .блока, 20 подключенного входом через элемент И к соответствующему входу устройства, причем выход первого запоминающего блок подключен к нулевому входу триггера,- а выход второго запоми- 25 наввдего блока - к единичному входу триггера, единичный выход, которого подключен ко второму входу первого элемента и, а нулевой выход - ко вто.рому входу элемента И И . . 30

Недостаток данного устройства сложность, обусловленная наличием в схеме двух коммутаторов, работающих поочередно, а также необходимостью расширения входов регистров адресов для обеспечения записи информации с любого из двух коммутаторов.

Цель изобретения - упрощение устройства. .

Это достигается тем, что микропрограммное устройство управления, содержащее коммутатор, первый и второй выходы которого соединены соответственно со входами первого и второго регистра адреса, выходы которых соединены с первыми входами первого и второго блока памяти соответственно, вторые входы которых соединены соответственно с выходами первого и второго элементов И, первый вход первого элемента И является первым входом устройства, второй вход соединен с единичным выходом триггера, первый вход второго элемента И является вторым входом устройства, а второй вход соединен с нулевым выходом триггера, нулевой вход которо.го соединен с первым выходом перво го блока памяти, а единичный входпервым выходом второго блока памяи, содержит первые и вторые элемены НЕ и ИЛИ, группу элементов ИЛИ, ричем первый и второй входы элеменов ИЛИ группы соединены соответстенно со вторыми выходами первого и торого блока памяти, первый выход первого блока памяти соединен через первый элемент НЕ со входом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого соединен через второй элемент НЕ с первым выходам второго блока памяти и со вторым входом первого элемента ИЛИ, выход которого соединен с первым входом коммутатора, выход втоfioro элемента ИЛИ соединен со вторым входом коммутатора, выход элементов ИЛИ группы соединен с третьим входом коммутатора.

В устройстве используют только один коммутатор, который работает в каждом такте работы устройства и обеспечивает запись информации с выходов блока памяти в нужный регистр адреса (т.е. в тот, с которого она должна считываться в следующем такте) . .

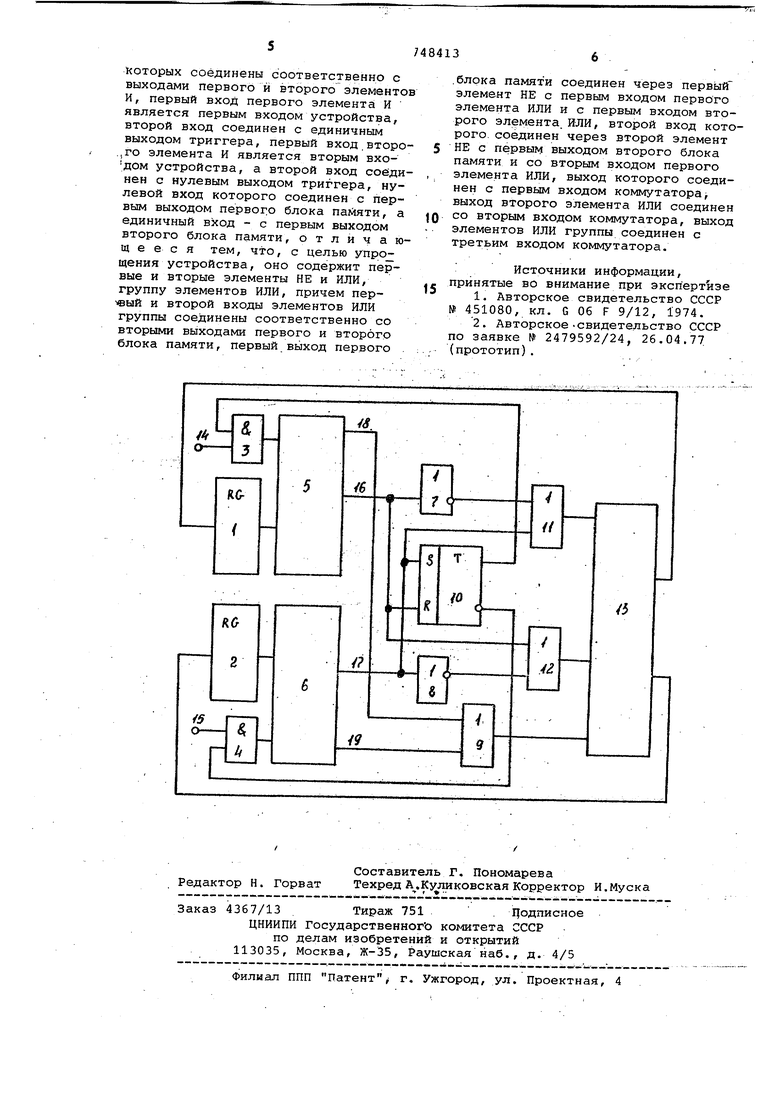

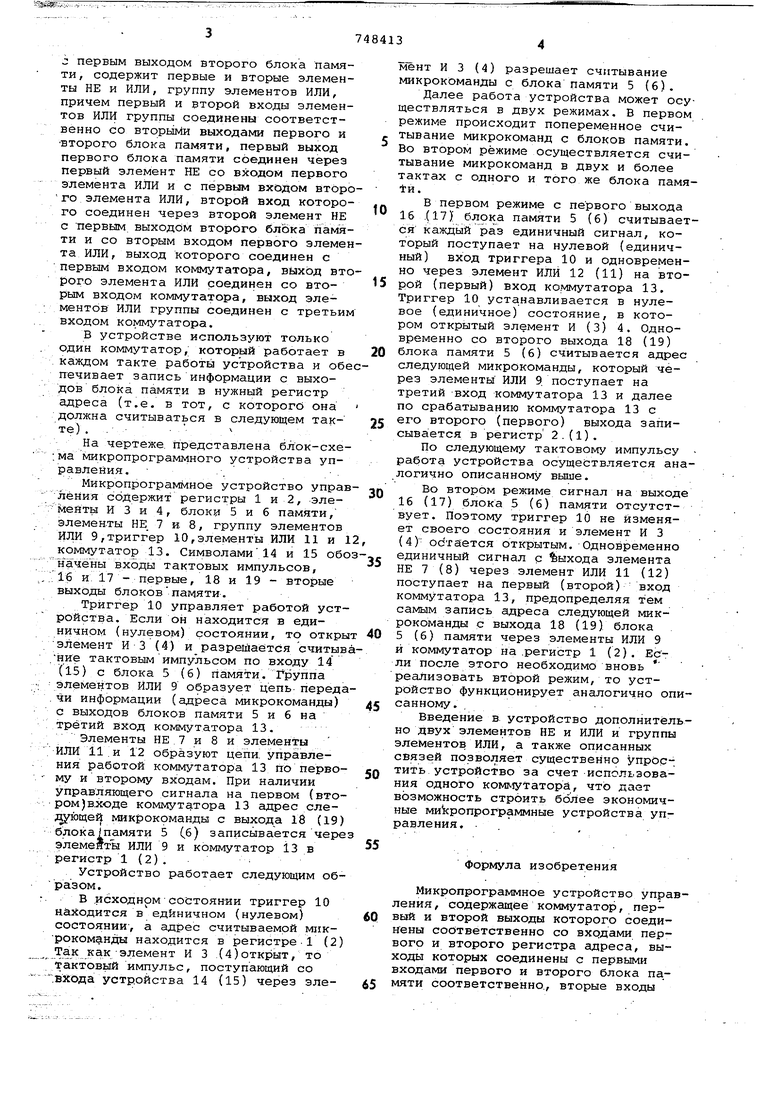

На чертеже. Представлена блок-схема микропрограммного устройства управления. . .

Микропрограммное устройство управления содержит регистры 1 и 2, элементы И 3 и 4, блоки 5 и 6 памяти, элементы НЕ 7 и. 8, группу элементов ИЛИ 9,триггер 10,элементы ИЛИ 11 и 12, коммутатор 13. Символами14 и 15 обозначёны входы тактовых импульсов, 16 и 17 - первые, 18 и 19 - вторые выходы блоковпамяти.

Триггер 10 управляет работой устройства. Если он находится в единичном (нулевом) состоянии, то открыт элемент ИЗ (4) и разрешается считывание тактовымимпульсом по входу 14 (15) с блока 5 (6) памяти. Труппа элементов ИЛИ 9 образует цепь-передачи информации (адреса микрокоманды)

с выходов блоков памяти 5 и 6 на третий вход коммутатора 13.

/Элементы НЕ.7 и В и элементы ИЛИ 12 образуют цепн управления работой коммутатора 13 по первому ивторому входам. При наличии управляющего сигнала на первом (втором)в.ходе коммутатора 13 адрес следующей микрокоманды с выхода 18 (19) блока1памяти 5 (6) записывается через элементы ИЛИ 9 и коммутатор 1з в регистр 1(2).

Устройство работает следующим образом.

В .исходном состоянии триггер 10 находится в единичном (нулевом) СОСТОЯНИИ , а адрес считываемой микроком нды находится в регистре.1 (2) Так как-элемент И 3 (4)открыт, то тактовый импульс, поступающий со .входа устройства 14 (15) через элемент ИЗ (4) разрешает считывание микрокоманды с блока памяти 5 (6).

Далее работа устройства может осуществляться в двух режимах. В первом режиме происходит попеременное считывание микрокоманд с блоков памяти. Во втором режиме осуществляется считывание микрокоманд в двух и более тактах с одного и того же блока памя±и.

В первом режиме с первого выхода 16 .(17) блока памяти 5 (6) считывается каждый раз единичный сигнал, который поступает на нулевой (единичный) вход триггера 10 и одновременно через элемент ИЛИ 12 (11) на второй (первый) вход коммутатора 13. Триггер 10 устанавливается в нулевое (единичное) состояние, в котором открытый элемент И (3) 4. Одновременно со второго выхода 18 (19) блока памяти 5 (6) считывается адрес следующей микрокоманды, который через элементы ИЛИ 9. поступает на третий вход коммутатора 13 и далее по срабатыванию коммутатора 13 с его второго (первого) выхода записывается в регистр 2.(1).

По следующему тактовому импульсу работа устройства осуществляется аналогично описанному выше.

Во втором режиме сигнал на выходе 16 (17) блока 5 (6) памяти отсутствует. Поэтому триггер 10 не изменяет своего состояния и элемент И 3 (4)- ос5тается открытым. Одновременно единичный сигнал с хода элемента НЕ 7 (8) через элемент ИЛИ 11 (12) поступает на первый (второй) вход коммутатора 13, предопределяя тем самым запись адреса следующей микрокоманды с выхода 18 (19) блока 5 (6) памяти через элементы ИЛИ 9 и коммутатор на .регистр 1 (2). Если после этого необходимо вновь реализовать второй режим, то устройство функционирует аналогично описанному.

Введение в устройство дополнительно двух элементов НЕ и ИЛИ и группы элементов ИЛИ, а также описанных связей позволяет существенно упростить устройство за счет использования одного коммутатора, что дает возможность строить более экономичные микропрограммные устройства управления. .

Формула изобретения

Микропрограммное устройство управления , содержащее коммутатор, первый и второй выходы которого соединены соответственно со вхрдами первого и второго регистра адреса, выходы которых соединены с первыми входами первого и второго блока па.мяти соответственно., вторые входы

которых соединены соответственно с выходами первого и второго элементов И, первый вход первого элемента И является первым входом устройства, второй вход соединен с единичным выходом триггера, первый вход,второ.,го элемента И является вторым входом устройства, а второй вход соединен с нулевым выходом триггера, нулевой вход которого соединен с первым выходом первого блока пайяти, а единичный вход - с первым выходом второго блока памяти, отличающееся тем, что, с целью ynpoj щения устройства, оно содержит первые и вторые элементы НЕ и ИЛИ, группу элементов ИЛИ, причем первый и второй входы элементов ИЛИ группы соединены соответственно со вторыми выходами первого и второго блока памяти, первый выход первого .

.блока памяти соединен через первый элемент НЕ с первым входом первого элемента ИЛИ и с первым входом второго элемента, ИЛИ, второй вход которого, соединен через второй элемент НЕ с первым выходом второго блока памяти и со вторым входом первого элемента ИЛИ, выход которого соединен с первым входом коммутатора выход второго элемента ИЛИ соединен со вторым входом коммутатора, выход

0 элементов ИЛИ группы соединен с третьим входом коммутатора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 451080, кл, G 06 F 9/12, 1974.

2. Авторское-свидетельство СССР по заявке № 2479592/24, 26.04.77 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммного управления | 1977 |

|

SU679980A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Устройство для контроля микропрограмм | 1982 |

|

SU1034042A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

Авторы

Даты

1980-07-15—Публикация

1978-07-03—Подача