(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОЙ

ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением отказов | 1981 |

|

SU1005192A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство | 1978 |

|

SU696543A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

1

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля оперативной памяти, в котором в качестве управляющих сигналов для оконечного регистрирующего цифропечатающего устройства используются сигналы из блока адреса и из блока контроля для печати адреса бракованного элемента и характера брака 1

Недостаток устройства - низкая производительность.

Наиболее близким техническим решением к данному изобретению является устройство для контроля оперативной памяти, содержащее блок формирования тестов, блок управления, адресный блок, блок подключения матриц, блок печати и блок обнаружения неисправностей, причем вход адресного блока подключен к выходу блока формирования тестов, первый выход адресного блока соединен со входом блока подключения матриц, выход которого подключен ко входу блока обнаружения неисправностей, первый выход которого соединен со входом блока управления, одни из выходов которого соединены с управляющими входами блока формирования тестов, адресного блока и блока обнаружения неисправностей 2.

Недостаток устройства - увеличение времени контроля всей оперативной памяти на время распечатки данных о забракованных J элементах и, вследствие этого, низкое быстродействие устройства.

Цель изобретения - повышение быстродействия устройства.

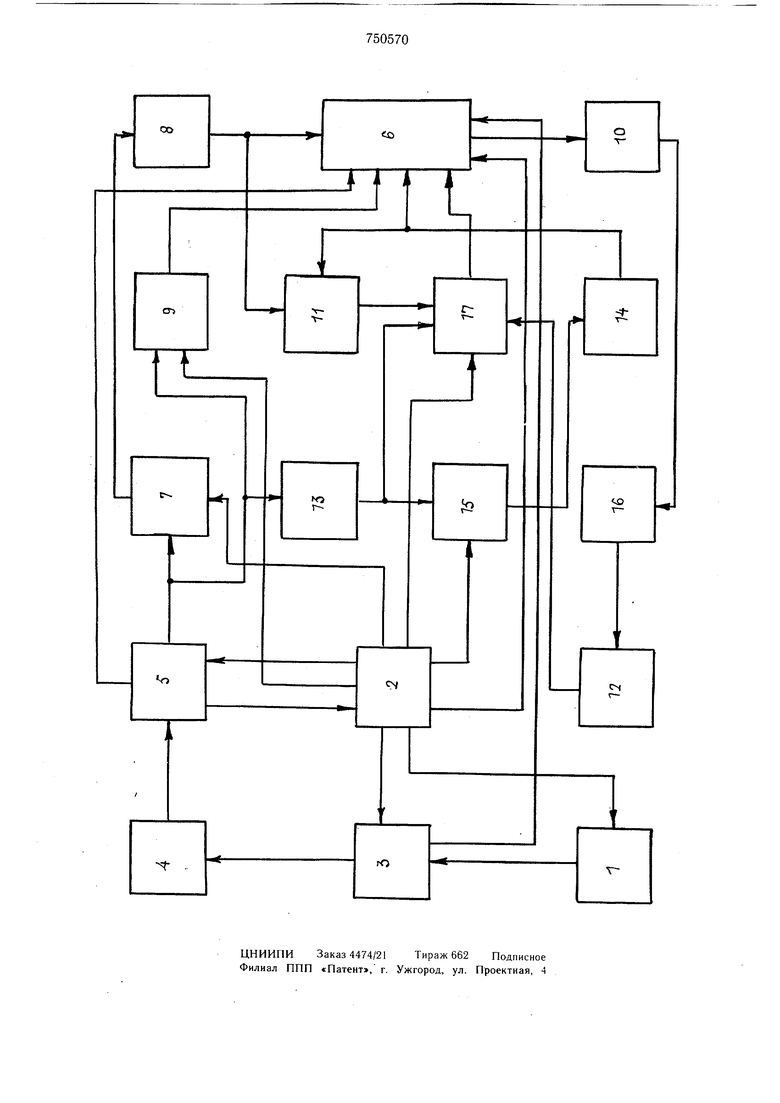

Поставленная цель достигаестся тем, что устройство содержит накопитель, регистры, О блок местного управления, схему сравнения, элементы И и элемент НЕ, причем первые входы первого элемента И и второго элемента И и вход элемента НЕ подключены к третьему выходу блока обнаружения неисправностей, первые входы третьего элемента И и четвертого элемента И соединены с выходом элемента НЕ, выход первого элемента И подключен ко входу первого регистра, выход которого соединен с одним из входов схемы сравнения, другой вход которой подключен к выходу второго регистра, входы второго и третьего регистров соединены соответственно с выходом третьего элемента И и выходом накопителя, вход которого подключен к выходу блока местного управления, один из входов которого и вторые входы элементов И соединены с другими выходами блока управления, третий и четвертый входы четвертого элемента И подключены к выходу схемы сравнения и выходу блока печати, вход которого соединен с выходом третьего регистра, вторые выходы адресного блока и блока обнаружения неисправностей, выходы первого регистра, второго элемента И, второго регистра и четвертого элемента И соединены с другими входами блока местного управления. На чертеже изображена блок-схема предлагаемого устройства. Устройство состоит из блока 1 формирования тестов, блока 2 управления, адресного блока 3, блока 4 подключения матриц, блока 5 обнаружения неисправностей, блока 6 местного управления, первого элемента И 7, первого регистра 8, второго элемента И 9, накопителя 10, схемы 11 сравнения, блока 12 печати, элемента НЕ 13, второго регистра 14, третьего элемента И 15, третьего регистра 16 и четвертого элемента И 17. Вход адресного блока 3 подключен к выходу блока 1 формирования тестов, а первый выход - ко входу блока 4 подключения матриц, выход которого соединен со входом блока 5 обнаружения неисправностей. Первый выход блока 5 соединен со входом блока 2 управления, одни из выходов которого соединены с управляющими входами |§лока 1 формирования тестов, адресного |0лока 3 и блока 5 обнаружения неисправностей. Первые входы элементов И 7 и И 9 и вход элемента НЕ 13 подключень к выходу блока 5 обнаружения неисправностей. Первые входы элементов И 15 и И 17 соединены с выходом элемента НЕ 13. Выход элемента И 7 подключен ко входу регистра 8, выход которого соединен со входом блока 6 местного управления и с одним из входов схемы 11 сравнения, другой вход которой подключен к выходу регистра 14. Входы регистров 14 и 16 соединены соответственно с выходом элемента И 15 и выходом накопителя 10, вход которого подключен к выходу блока 6 местного управления. Один из входов блока 6 и вторые входы всех четырех элементов И соединены с другими выходами блока 2 управления. Третий и четвертый входы элемента И 17 соединены с выходом схемы 11 сравнения и выходом блока 12 печати, вход которого подключен к выходу регистра16. Вторые выходы адресного блока 3 и блока 5 обнаружения неисправностей, выходы элементов И 9 и И 17 и регистра 14 соединены с другими входами блока 6 местного управления. Устройство работает следующим образом. Проверяемая матрица подключается к блоку 4. Блок 1 формирования тестов вырабатывает последовательность управляющих сигналов вида теста, определяемого блоком 2 управления, которые в адресном блоке 3 преобразуются в сигналы записи-чтения и по определенным адресам подаются на блок 4 подключения матриц. При обнаружении элемента памяти с параметрами считанного сигнала, не соответствующими установленным требованиям, из блока 5 обнаружения неисправностей выдается сигнал в блок 2 управления для останова работы адресного блока 3. Адрес бракованного элемента проверяемой матрицы подается в блок 6 местного управления,, в который подается из блока 2 управления информация о номере проверяющего теста и из блока 5 обнаружения неисправностей - информация о характере брака. При наличии брака на один вход первого элемента И 7 из блока 5 подается разрещающий потенциал и через второй вход проходит из блока 2 управления сигнал установки адреса на первом регистре 8 - регистре адреса записываемых слов. Разрешающий сигнал из блока 5 подается также на второй элемент И 9, через который из блока 2 управления в блок 6 местного управления проходит команда на запись первого слова, содержащего информацию из блока 5 обнаружения неисправностей, блока 2 управления и адресного блока 3, в накопитель 10. После записи информации о первом забракованном элементе блок управления 2 снимает блокировку работы адресного блока 3 и производится проверка следующих запоминающих элементов. При обнаружении следующего бракованного элемента блок 2 управления установит на первом регистре 8 адрес второго слова, по которому в накопителе 10 записывается информация о втором забракованном элементе. При отсутствии брака блок 5 выдает на первый 7 и второй 9 элементы И запрещающий потенциал, который преобразуется элементом НЕ 13 в разрещающий для прохождения через третий элемент И 15 сигнала из блока 2 управления на установку второго регистра 14, являющегося регистром адреса считываемых слов, в состояние, соответствующее адресу первого слова накопителя 10. Разрещающий сигнал с выхода элемента НЕ 13 подается на четвертый элемент И 17, на который подается также разрешающий сигнал от блока 12 печати в случае окончания распечатки и разрещающий сигнал иа схемы 11 сравнения состояний регистров в случае, когда на первый регистр 8 занесен адрес номера слова, который не меньше номера слова, занесенного во второй регистр 14. При наличии этих разрешающих сигналов через элемент И 17 от блока 2 управления проходит в блок 6 местного управления сигнал считывания слова из накопителя 10 в третий регистр 16, с которого информация подается для распечатки в блок 12 печати. При отсутствии сигнала брака с блока 5 операция считывания из накопителя 10 может повториться, пока номер слова регистра 14 не станет больше номера слова регистра 8. По окончании проверки матрицы вся информация о ней окажется записанной в накопитель 10 и часть ее (или вся) будет распечатана. При установке в блоке 4 подключения матриц новой матрицы распечатка оставшихся слов может продолжаться. Технико-экономическое преимущество предлагаемого устройства заключается в существенном увеличении быстродействия за счет того, что длительность записи и считывания информации о бракованном элементе .матрицы значительно меньше времени ее распечатки и работа цифропечатающего устройства происходит одновременно с проверкой матрицы или ее заменой после проверки. Формула изобретения Устройство для контроля оперативной памяти, содержащее блок формирования тестов, блок управления, адресный блок, блок подключения матриц, блок печати и блок обнаружения неисправностей, причем вход адресного блока подключен к выходу блока формирования тестов, первый выход адресного блока соединен со входом блока подключения матриц, выход которого подключен ко входу блока обнаружения неисправностей, первый выход которого соединен со входом блока управления, одни из выходов которого соединены с управляющими входами блока формирования тестов, адресного блока и блока обнаружения неисправностеи, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит накопитель, регистры, блок местного управления, схему сравнения, элементы И и элемент НЕ, причем первые входы первого и второго элементов И и вход элемента НЕ подключены к третьему выходу блока обнаружения неисправностей, первые входы третьего и четвертого элементов И соединены с выходом элемента НЕ, выход первого элемента И подключен ко входу первого регистра, выход которого соединен с одним из входов схемы сравнения, другой вход которой подключен к выходу второго регистра, входы второго и третьего регистров соединены соответственно с выходом третьего элемента И и выходом накопителя, вход которого подключен к выходу блока местного управления, один из входов которого и вторые входы элементов И соединены с другими выходами блока управления, третий и четвертый входы четвертого элемента И подключены к выходу схемы сравнения и выходу блока печати, вход которого соединен с выходом третьего регистра, вторые выходы адресного блока и блока обнаружения неисправностей, выходы первого регистра, второго элемента И, второго регистра и четвертого элемента И соединены с другими входами блока местного управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 464019, кл. G 11 С 29/00, 1973. 2.Авторское свидетельство СССР № 516103, кл. G И С 29/00, 1974 (прототип).

Авторы

Даты

1980-07-23—Публикация

1978-06-27—Подача