(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения | 1978 |

|

SU860062A1 |

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Устройство для умножения | 1981 |

|

SU991414A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

Изобретение относится к вычислительной технике и может быть применено в качестве решающего узла цифровой вычислительной машины.

Известно устройство умножения двоичных чисел, представленных последовательным кодом, содержащее 2п-разрядный сумматор, (п-1)-разрядные регистры множимого и множителя и элементы И 1.

Однако в этом устройстве только г/шожимое подается старшими разрядами вперед, а результат получается через п.циклов вычислений.

Известно устройство для умножения, содержащее регистры множимого и множителя, регистр результата, сумглатор результата, сумматор сомножителей, блок анализа разрядов, регистр сдвига, элементы И и элементы ИЛИ, в котором производится ввод сомножителей поразрядно, старшими разрядами вперед 2.

Однако в данном устройстве каждый разряд результата получается за три такта работы, т.е. устройство имеет низкое быстродействие.

Наиболее близким к изобретению по технической сущности является устройство для умножения, содержащее регистр множимого, регистр множителя.

сумматор результата, регистр результата, регистр сдвига, два коммутатора и элементы И 3.

Недостатком этого устройства является невозможность работы последовательным методом, начиная со старшего разряда, т.е. низкое быстродействие.

Цель изобретения - повыгчение быстродействия устройства.

10

Поставленная цель достигается тем, что в устройство для умножения, содержащее регистр сдвига, первый , татор, информационные входы которого соединены с выходами регистра сдвига,

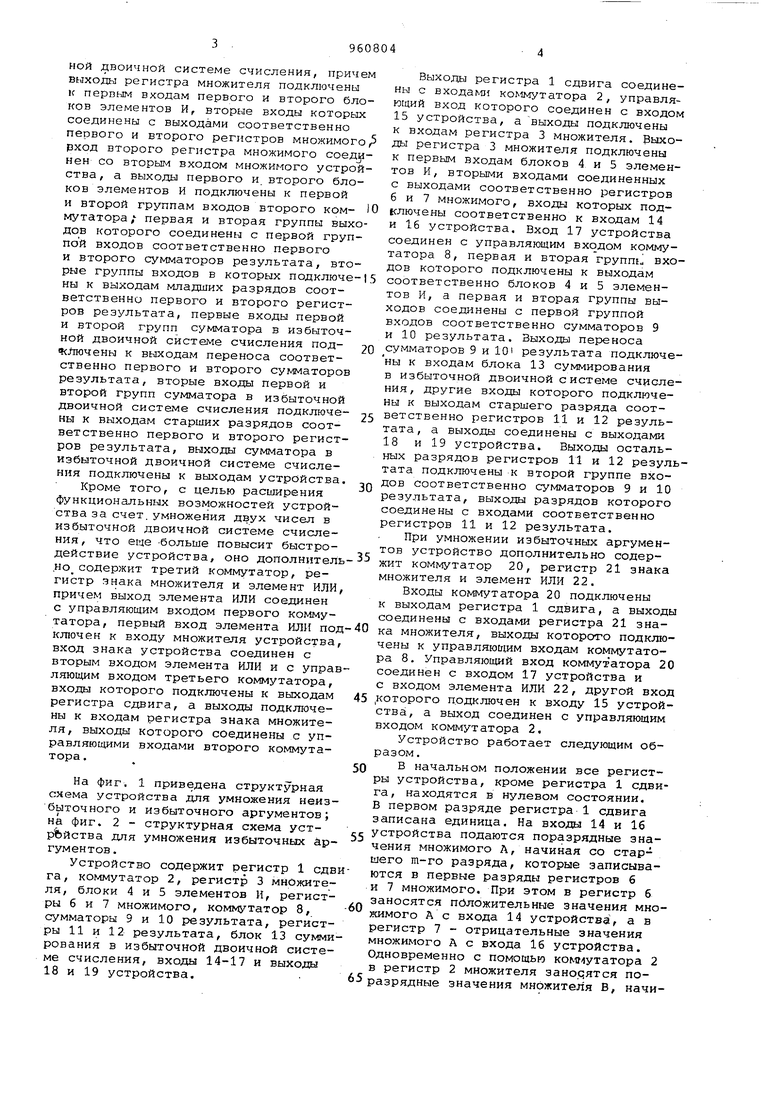

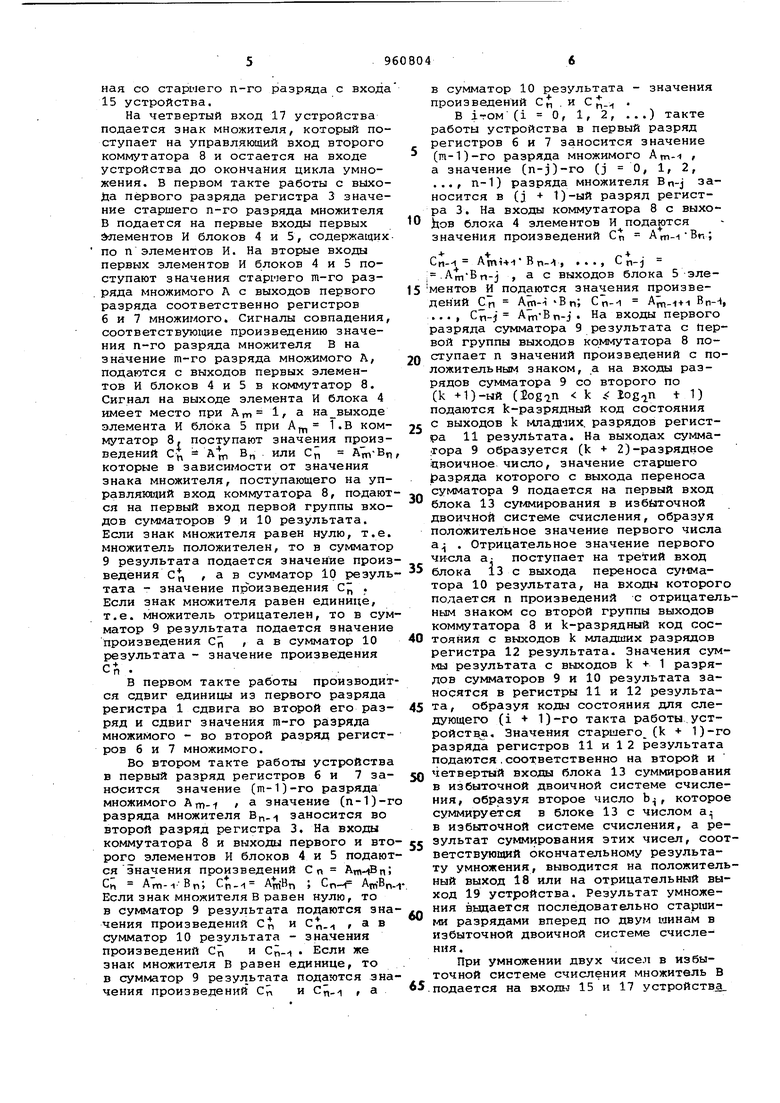

15 а управляю1ций вход подключен к входу множителя устройства, регистр множителя, входы которого подключены к выходам первого коьлмутатора, первый регистр множимого, вход которого подклю20чен к первому входу множимого устройства, второй комглутатор, управляющий вход которого соединен с входом знаka устройства, первый сумматор результата и первый регистр результата, вхо25ды которого соединены с выходами первого сумматора результата, введены первый и второй блоки элементов И, второй регистр множимого, второй сумматор результата, второй регистр ре30зультата, блок суммирования в избыточной двоичной системе счисления, прич выходы регистра множителя подключены к первым входам первого и второго бл ков элементов И, вторые входы которы соединены с выходами соответственно первого и второго регистров множимог рход второго регистра множимого соед нен со вторым входом множимого устро ства, а выходы первого и второго бло ков элементов И подключены к первой и второй группам входов второго коммутатора/ первая и вторая группы вых дов которого соединены с первой груп пой входов соответственно первого и второго сумматоров результата, вто рые группы входов в которых подключе вы к выходам младших разрядов соответственно первого и второго регистров результата, первые входы первой и второй групп сумматора в избыточной двоичной системе счисления подключены к выходам переноса соответственно первого и второго сумматоров результата, вторые входы первой и второй групп сумматора в избыточной двоичной системе счисления подключе- ны к выходам старших разрядов соответственно первого и второго регистров результата, выходы сумматора в избыточной двоичной системе счисления подключены к выходам устройства. Кроме того, с целью расширения функциональных возможностей устройства за счет, умножения двух чисел в избыточной двоичной системе счисления , что erne -больше повысит быстродействие устройства, оно дополнитель но содержит третий коммутатор, регистр знака множителя и элемент ИЛИ, причем выход элемента ИЛИ соединен с управляющим входом первого коммутатора, первый вход элемента ИЛИ под ключен к входу множителя устройства, вход знака устройства соединен с вторым входом элемента ИЛИ и с управ ляющим входом третьего коммутатора, входы которого подключены к выходам регистра сдвига, а выходы подключены к входам регистра знака множителя, выходы которого соединены с управляющими входами второго коммутатора. . На фиг. 1 приведена структурная схема устройства для умножения неизбыточного и избыточного аргументов; на фиг. 2 - структурная схема устрЬйства для умножения избыточных йргументов. Устройство содержит регистр 1 сдв га, коммутатор 2, регистр 3 множителя, блоки 4 и 5 элементов И, регистры 6 и 7 множимого, коммутатор 8, сумматоры 9 и 10 результата, регистры 11 и 12 результата, блок 13 сумми рования в избыточной двоичной системе счисления, входы 14-17 и выходы 18 и 19 устройства, Выходы регистра 1 сдвига соединены с входами коммутатора 2, управляющий вход которого соединен с входом 15 устройства, а выходы подключены к входам регистра 3 множителя. Рыходы регистра 3 множителя подключены к первым входам блоков 4 и 5 элементов И, вторыми входами соединенных с выходами соответственно регистоов 6 и 7 множимого, входы которых подключены соответственно к входам 14 и 16 устройства. Вход 17 устройства соединен с управляющим входом коммутатора 8, первая и вторая групш входов которого подключены к выходам соответственно блоков 4 и 5 элементов И, а первая и вторая группы выходов соединены с первой группой входов соответственно сумматоров 9 и 10 результата. Выходы переноса сумматоров 9 и 101 результата подключены к входам блока 13 суммирования в избыточной двоичной системе счисления, другие входы которого подключены к выходам старшего разряда соответственно регистров 11 и 12 результата, а выходы соединены с выходами 18 и 19 устройства. Выходы остальных разрядов регистров 11 и 12 результата подключены к второй группе входов соответственно сумматоров 9 и 10 результата, выходы разрядов которого соединены с входами соответственно регистров 11 и 12 результата. При умножении избыточных аргументов устройство дополнительно содержит коммутатор 20, регистр 21 знака множителя и элемент ИЛИ 22. Входы коммутатора 20 подключены к выходам регистра 1 сдвига, а выходы соединены с входами регистра 21 знака множителя, выходы которого подключены к управляющим входам коммутатора 8. Управляющий вход коммутатора 20 соединен с входом 17 устройства и с входом элемента ИЛИ 22, другой вход .которого подключен к входу 15 устройства, а выход соединен с управляюшим входом коммутатора 2, Устройство работает следующим образом . В начальном положении все регистры устройства, кроме регистра 1 сдвига, находятся в нулевом состоянии. В первом разряде регистра 1 сдвига записана единица. На входы 14 и 16 устройства подаются поразрядные значения множимого Л, начиная со старшего т-го разряда, которые записываются в первые разряды регистров б и 7 множимого. При этом в регистр б заносятся положительные значения множимого Ас входа 14 устройства, а в регистр 7 - отрицательные значения множимого А с входа 16 устройства. Одновременно с помощью коммутатора 2 в регистр 2 множителя заносятся поразрядные значения множителя В, начиная со старшего п-го разряда с входа 15 устройства. На четвертый вход 17 устройства подается знак множителя, который поступает на управляющий вход второго коммутатора 8 и остается на входе устройства до окончания цикла умножения. В первом такте работы с выхоJaa первого разряда регистра 3 значение старшего п-го разряда множителя 8подается на первые входы первых Элементов И блоков 4 и 5, содержащих по п элементов И. На вторые входы первых элементов И блоков 4 и 5 поступают значения старшего т-го разряда множимого Л с выходов первого разряда соответственно регистров 6 и 7 множимого. Сигналы совпадения, соответствующие произведению значения п-го разряда множителя В на значение т-го разряда множимого А, подаится с выходов первых элементов И блоков 4 и 5 в коммутатор 8. Сигнал на выходе элемента И блока 4 имеет место при АГП 1 а на выходе элемента И блока 5 при А 1 .В коммутатор 8, поступают значения произведений Cf, А Вг, или Сп которые в зависимости от значения знака множителя, поступающего на управляющий вход коммутатора 8, подают ся на первый вход первой группы входов сумглаторов 9 и 10 результата. Если знак множителя равен нулю, т.е. множитель положителен, то в сумматор 9результата подается значение произ ведения С t а в сумматор 10 резуль тата - значение прЪизведения С . Если знак множителя равен единице, т.е. множитель отрицателен, то в сум матор 9 результата подается значение произведения С , а в сумматор 10 результата - значение произведения С + п ... В первом такте работы производит ся сдвиг единицы из первого разряда регистра 1 сдвига во второй его разряд и сдвиг значения т-го разряда множимого - во второй разряд регистров б и 7 множимого. Во втором такте работы устройства в первый разряд регистров б и 7 заносится значение (m-l)-ro разряда множимого АП)--Г а значение (n-l)-r разряда множителя Br,-i заносится во второй разряд регистра 3. На входы коммутатора 8 и выходы первого и вто рого элементов И блоков 4 и 5 подают ся значения произведений Сп Сп Am--(БГ,; , AinBi-i ; Ср-f AirfBr,. Если знак множителя В равен нулю, то в сумматор 9 результата подаются зна чения произведений С, иС. ,ав сумматор 10 результата - значения произведений С и С. . Если же знак множителя В равен единице, то в сумматор 9 результата подаются зна чения произведений Сг и , а в сумматор 10 результата - значения произведений С . и С . В irOM (i О, 1, 2, ...) такте работы устройства в первый разряд регистров 6 и 7 заносится значение (m-l)-ro разряда множимого Ащ-- а значение (n-j)-ro (j О, 1, 2, ..., п-1) разряда множителя заносится в (J + 1)-ый разряд регистра 3. На входы коммутатора 8 с выхоЬов блока 4 элементов И подаются значения произведений Сп Ani-iBr.; Cfi-i А|П14-1 В Р--1, . ., С п-j |.AniBn-j , а с выходов блока 5 элементов И подаются значения произведений Сп Arn-i Вп; Сп-- А.1+-| Bn-, ..., ArnBfi-j На входы первого разряда сумматора 9 результата с Первой группы выходов коммутатора 8 поступает п значений произведений с положительным знаком, а на входаа разрядов сумматора 9 со второго по (k )-ый (login k : t 1) подаются k-разрядный код состояния с выходов k 1ллад1шх. разрядов регистра 11 результата. На выходах сумма:гора 9 образуется (k 2)-разрядное двоичное число, значение старшего р)азряда которого с выхода переноса сумматора 9 подается на первый вход блока 13 суГО 1ирования в избйточной двоичной системе счисления, образуя положительное значение первого числа а . Отрицательное значение первого числа а: поступает на третий вход блока 13 с выхода переноса сумматора 10 результата, на входы которого полается п произведений с отрицательным знаком со второй группы выходов коммутатора 3 и k-разрядный код состояния с выходов k младших разрядов регистра 12 результата. Значения суммы результата с выходов k + 1 разрядов сумматоров 9 и 10 результата заносятся в регистры 11 и 12 результата, образуя коды состояния для следующего (i + 1)-го такта работы,устройств а. Значения CTaptaero (k + 1)-го разряда регистров 11 и 1 2 результата подаются.соответственно на второй и четвертый входы блока 13 суммирования в избыточной двоичной системе счисления, образуя второе число Ь, которое суммируется в блоке 13 с числом а в избыточной системе счисления, а результат суммирования этих чисел, соответствующий окончательному результату умножения, выводится на положительный выход 18 или на отрицательный выход 19 устройства. Результат умножения выдается последовательно старшими разрядами вперед по двум шинам в избыточной двоичной системе счисления ., . При умножении двух чисел в избыточной системе счисления множитель В подается на входы 15 и 17 устройства. И поступает через элемент или г. нж управляющий вход сумматора 2. Кроме того, отрицательные значения множите ля с входа 17 устройства поступают на управляющий вход коммутатора 20, на i-ый вход которого в i-ом такте работы подается, единица с выхода (i 1)-го разряда регистра 1 сдвига При наличии единицы в отрицательном значении (п - i)-ro разряда множителя в С1+1)-ый разряд регистра 21 зна ка заносится единица и хранится в нем до окончания цикла умножения. Каждый разряд знака множителя управляет соответствующим разрядом коммутатора 8. В остальном работа устрой ства аналогична умножению неизбыточного и избыточного аргументов. При подаче одного из аргументов (множителя) параллельным кодом отпадает необходимость в регистре 1 сдви га, коммутаторах 2 и 20, т.е. устрой ство становится более простым. Таким образом, данное устройство позволяет производить умножение чисе одно из которых (или оба) выражено в избыточной двоичной системе счисле ния, последовательнЕлм методом старши ми разрядами вперед. При этом резуль тат умножения получается на выходах устройства одновременно с вводом раз рядов умножаемых чисел. По сравнению с известным устройством быстродействие увеличено примерно в три раза. При этом разрядность m г ожимого может быть больше разрядности п множителя. Формула изобретения 1. Устройство для умножения, содержащее регистр сдвига, первый коммутатор, информационные входы которого соединены с выходами регистра сдви га, а управляющий вход подключен к входу множителя устройства, регистр множителя, входы которого подключены к ВЕЛходам первого коммутатора, первый регистр множимого, вход которого подключен к первому входу множимого устройства, второй коммутатор управляющий вход которого соединен с входом знака устройства, первый сумматор результата и первый регистр результата, входы которого соединены Q выходами первого сумматора резуль та, отличающе еся тем, то, с целью увеличения быстродействия, в него введены первый и второ блоки элементов И, второй регистр множимого, второй сумматор результата, второй регистр результату, блок суммирования в избыточной двоичной системе счисления, причем выходы регистра множителя подключены к первым входам первого и второго блоков элементов И, вторые входы которых соединены с выходами соответственно первого и второго регистров множимого, вход второго регистра множимого соединен с вторым входом множимого устройства, а выходы первого и второго блоков элементов И подключены к первой и второй группам входов второго коммутатора, первая и вторая группы выходов которого соединены с первой группой входов соответственно первого и второго сумматоров результата, вторые группы входов в которых подключены к выходам младших разрядов (соответственно первого и второго pe-j гистров результата, первые входы первой и второй групп сумматора в избыточной двоичной системе счисления подключены к выходам переноса соответственно первого и второго сумматоров результата, вторые входы первой и второй групп сумматора в избыточной двоичной системе счисления подключены к выходам старших разрядов соответственно первого и второго регистров результата, выходы сумматора в избыточной двоичной системе счисления подключены к выходам устройства. 2. Устройство по п. 1, отличающееся тем, что, с целью расширения функциональных возможностей за счет умножения двух чисел в избыточной системе счисления, оно дополнительно содержит третий коммутатор, регистр знака множителя и элемент ИЛИ, причем выход элемента ИЛИ соединен с управляющим входом первого коммутатора, первый вход элемента ИЛИ подключен к входу множителя устройства, вход знака устройства соединен с вторым входом элемента ИЛИ и с управляющим входом третьего комр/гутатора, входы которого подключены к выходам регистра сдвига, а выходы подключены к входам регистра знака множителя, выходы которого соединены с управляющими входами второго коммутатора . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 631919, кл. G.06 F 7/39, 1975. 2.Авторское свидетельство СССР № 603989, кл. G 06 F 7/39, 1976. 3.Авторское свидетельство СССР № 451079, кл. G 7/39, 1973 (прототип).

118A/5

/

n

Ю

IL i

Ф

DH

Т

/7

/

Фиг./

Авторы

Даты

1982-09-23—Публикация

1979-08-22—Подача