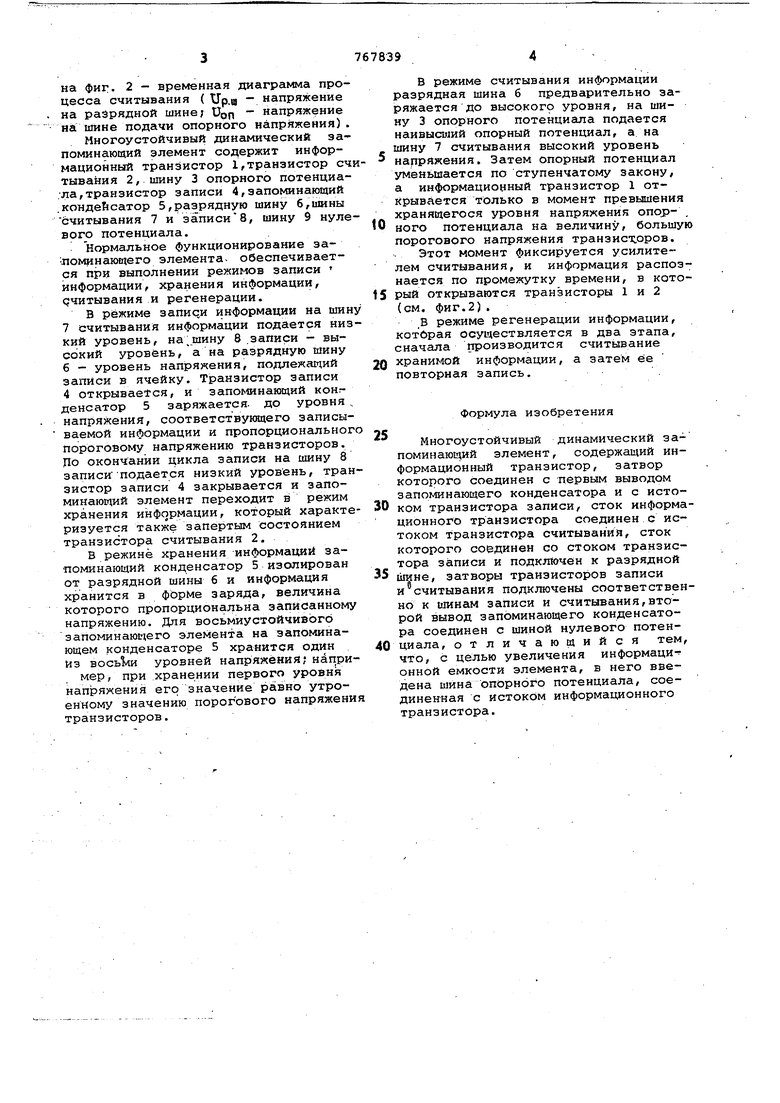

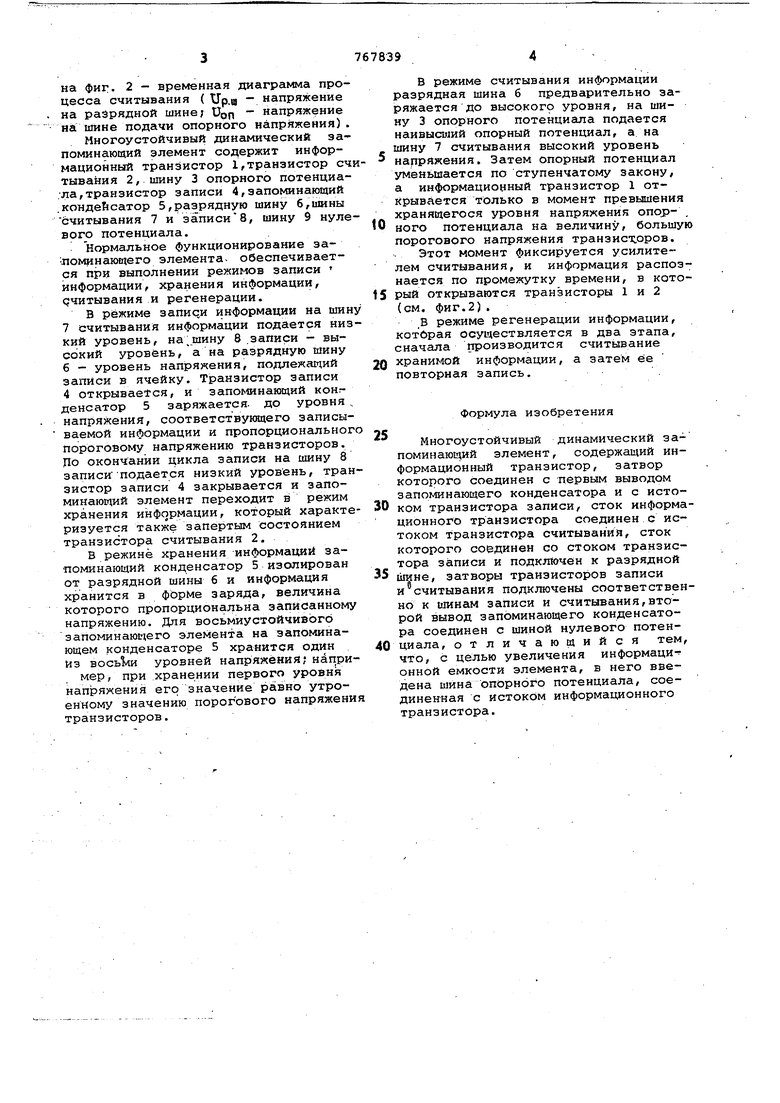

Изобретение относится к вычислительной технике.и может использовать ся при построении оперативных запоминающих устройств. , Известны многоустойчивые фазоимпульсные запоминающие элементы, соде жащие запоминающий конденсатор, два диода, узел заряда, разряда и считывания информации. . . Недостатками их являются сложност конструкции и невозможность произвольной выборки. Известны другие sanoNiMHaKflJiHe эле .менты, содержащие полевой транзистор с. двойным затвором; один из затворов является изолированным и слу-жит для хранения заряда, а другой является управляющим. Такая конструк ция позволяет хранить заряды различных величин, что повышает информационную емкость., запоминающего элемента. . Этот запоминающий элемент, однако имеет большое время записи и с.пож«ую конструкцию. Наиболее близким техническим решением к предлагаёмоглу изобретению, является динамический запоминающий элемент, содержащий информационный транзистор, затвор которого соединен с первым выводом запоминающего конденсатора и с истоком транзистора записи, сток информационного транзистора соединен с истоком транзистора считывания, сток которого соединен со стоком транзистора записи и подключен к разрядной шине, затворы транзисторов записи и считывания подключены соответственно к шинам записи и считывания, а вторсэй вывод запоминающего конденсатора и исток информационного транзистора соединены с шиной нулевого потенциала. Недостатком итого запоминающего элемента является малая информационная емкость, так как он позволяет хранить всего 1 бит. информации. Целью изобретения является увеличение информационной емкости запоминаюиего элемента за счет обеспечения хранения нескольких бит информации ,. Это достигается тем, что в предлагаемый динамический запоминающий элемент введена мина опорного потенциала, которая соединена с истоком информационного транзистора. На фиг. 1 приведена электрическая схема предлагаемого многоустойчивогс динамического запоминающего элемента;

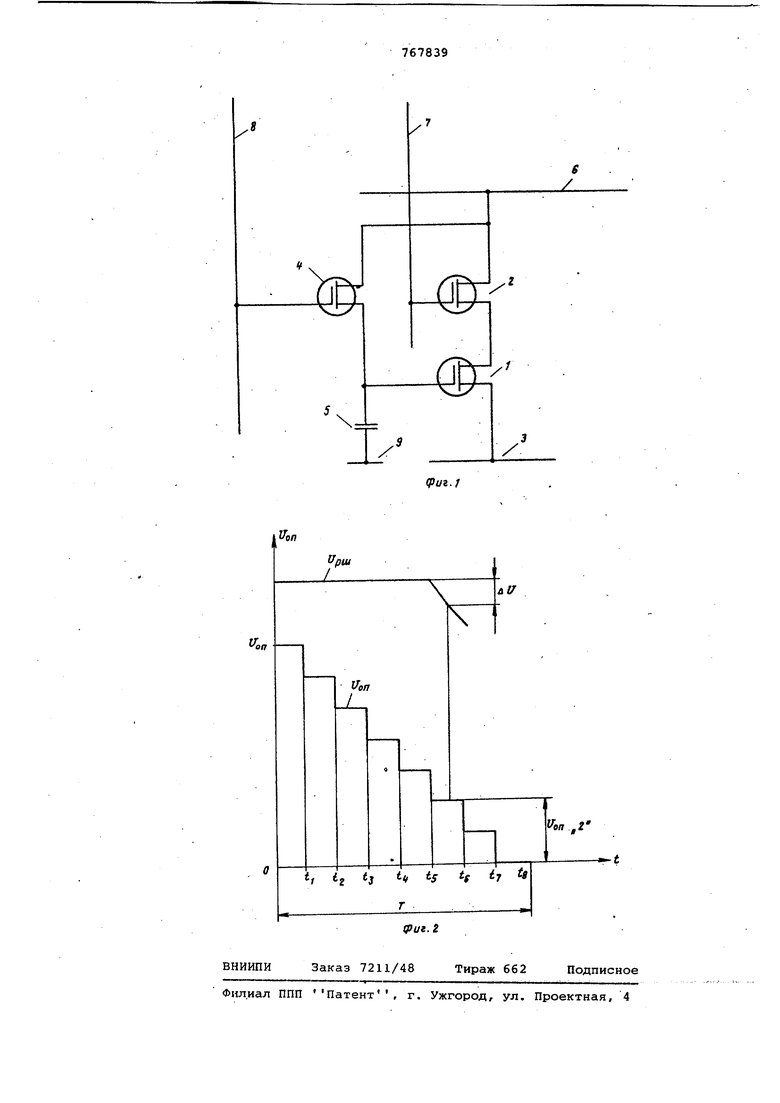

на фиг. 2 - временная диаграмма процесса считывания ( Up.a - напряжение на разрядной шине; Don напряжение на шине подачи опорного напряжения).

Многоустойчивый динамический запоминающий элемент содержит информационный транзистор I,транзистор счтывания 2, шину 3 опорного потенциа.ла,транзистор записи 4,запоминающий .конденсатор 5,разрядную шину б,шины считывания 7 и записи8, шину 9 нулевого потенциала.

нормальное функционирование за ломинающего элемента, обеспечивается при выполнении режимов записи информации, хранения информации, дчитывания и регенерации.

В режиме запис,и информации на шин 7 считываний информации подается низкий уровень, на.шину 8 .записи - высокий уровень, а на разрядную шину б - уровень напряжения, подлежащий записи в ячейку. Транзистор записи 4 открывается, и запоьетнающнй кон.денсатор 5 заряжается, до уровня , напряжения, соответствующего записываемой информации и пропорциональног пороговому напряжению транзисторов. До окончании цикла записи на шину 8 записи подается низкий уровень, транзистор записи 4 закрывается и запоминающий элемент переходит в режим хранения информации, который характеризуется также запертым состоянием транзистора считывания 2.

В режинё хранения информации запоминающий конденсатор 5 изолирован от разрядной шины 6 и информация хранится в форме заряда, величина которого пропорциональна записанному напряжению. Для восьмиустойчивЬгб запоминающего элемента на запоминающем конденсаторе 5 хранится один Из уровней напряжения; например, при хранении первого уровня напряжения его значение равно утроенному значению порогового напряжени транзисторов.

В режиме считывания информации разрядная шина б предварительно заряжается до высокого уровня, на шину 3 опорного потенциала подается наивысвшй опорный потенциал, а на шину 7 считывания высокий уровень напряжения. Затем опорный потенциал уменьшается по ступенчатому закону, а информационный транзистор 1 открывается только в момент превышения хранящегося уровня напряжения опор- .

О ного потенциала на величину, большую порогового напряжения транзисторов. Этот момент фиксируется усилителем считывания, и информация распознается по промежутку времени, в который открываются транзисторы 1 и 2 (см. фиг.2).

Ъ режиме регенерации информации, которая осуществляется в два этапа, сначала производится считывание

0 хранимой информации, а затем ее повторная запись.

Формула изобретения

Многоустойчивый динамический запоминающий элемент, содержащий информационный транзистор, затвор которого Соединен с первым выводом запоминающего конденсатора и с истоком транзистора записи, сток информационного транзистора соединен с истоком транзистора считываний, сток которого соединен со стоком транзистора записи и подключен к разрядной

5 шине, затворы транзисторов записи и считывания подключены соответственно к шинам записи и считывания,второй вывод запоминающего конденсатора соединен с шиной нулевого потенциала, отличающийся тем, что, с целью увеличения информационной емкости элемента, в него введена шина опорного потенциала, соединенная с истоком информационного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Способ хранения информации на МДП-транзисторе и запоминающий элемент для осуществления этого способа | 1977 |

|

SU943846A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Ячейка памяти | 1976 |

|

SU630640A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

Авторы

Даты

1980-09-30—Публикация

1977-05-10—Подача