(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Запоминающее устройство с коррекцией дефектных элементов памяти | 1981 |

|

SU980165A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Программируемое постоянное запоминающее устройство | 1981 |

|

SU999111A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Программируемый дешифратор | 1986 |

|

SU1399816A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Резервированное запоминающее устройство с самоконтролем | 1982 |

|

SU1070609A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

I

- Изобретение относится к вычислительной технике и может быть использовано при построении постоянных запоминающих устройств (ПЗУ).

Одно из известных ПЗУ содержит узел постоянной памяти, состоящий из m модулей, узел сменной информации, выходное устройство, схемы ИЛИ и блок блокировки, при этом вход первого канала выходного устройства соединен с выходом узла сменной информации, а вход второго канала соединен с выходом блока блокировки, вход которого соединен с выходом узла постоянной памяти и с выходом схем ИЛИ, входы узла постоянной памяти и узла сменной информации объединены 1 .

Недостаток известного устройства - ограниченная возможность коррекции за- писанной информации.

Наиболее близким техническим решением к данному изобретению является постоянное запоминающее устройство, содержащее fn основных запоминающих модулей, адресные входы которых объединены 2.

Недостаток этого устройства - ограниченная возможность коррекций ЗапШЖной информации, так как программирование

запоминающего модуля производится путем пережигания плавких вставок микросхем памяти, входящих в состав заполгинающего модуля. При этом в случае записи «1 в каком-либо разряде слова производится пережигание соответствующей плавкой вставки, при записи 0 пережигание не производится. Из этого ясно, что при коррекции информации в модуле имеется возможность вместо «О записать «1, т. е. пережечь соответствующую вставку, восстановить

10 плавкую вставку нельзя, т. е. нельзя записать «О вместо «1, что приводит к необходимости замены модуля.

Цель изобретения - обеспечение коррекции записанной информации в устройстве.

IS

Для достижения этой цели устройство содержит дополнительный запоминающий модуль, элементы И и коммутаторы по числу

основных запоминающих модулей, при этом В1ыходы каждого основного запоминающего

20 модуля соединены сбо гвётствёННй с перейми входами соответствующих коммутаторов и входами элемента И, выходы дополнительного запоминающего модуля подключены к соответствующим вторым входам коммутаоров, третьи входы которых соединены с ыходами соответствующих элементов И.

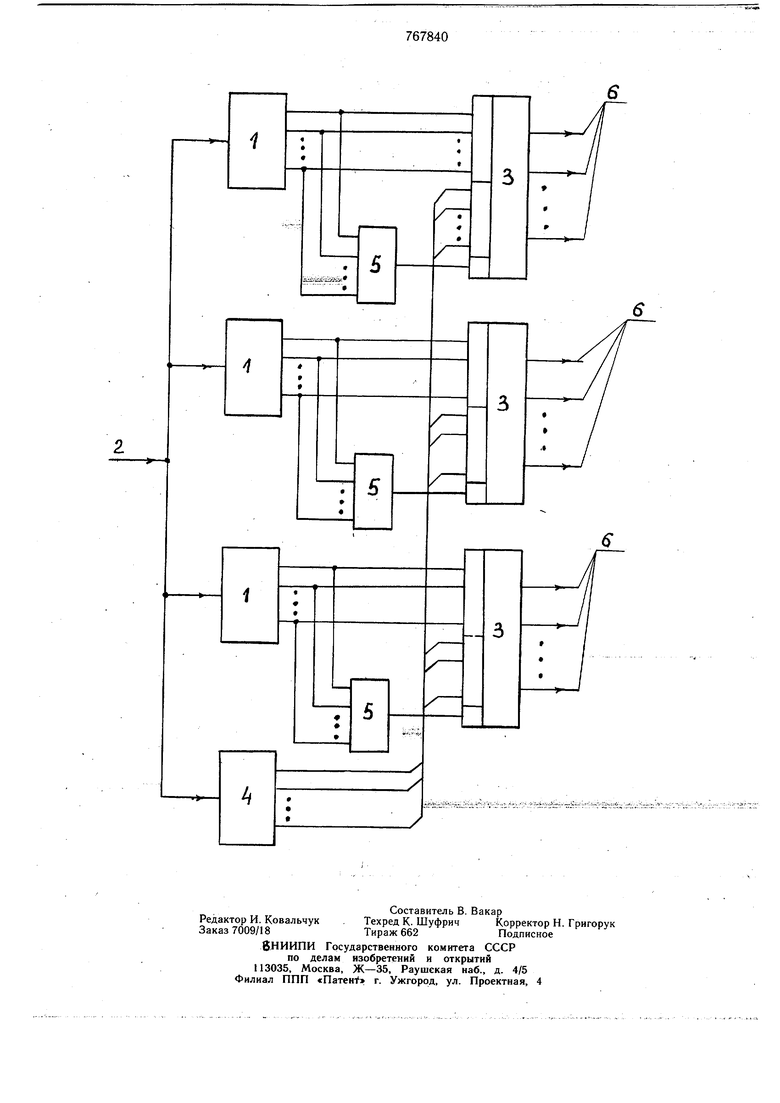

На чертеже приведена блок-схема предагаемого устройства.

Устройство содержит fri основных запоинающих модулей 1, адресные входы коорых объединены и подключены к входным шинам адреса 2, m коммутаторов 3, дополнительный запоминающий модуль 4, m элементов 5 И.,.:-..,...-.-....

Устройство работает следующим образом.

Код адреса по адресным щинам 2 податся на основные запоминающие модули I : и дополнительный запоминающий модуль 4. При этом с каждого основного запоминающего модуля 1 и с дополнит-ельного запоминающего модуля 4 по соответствующему адресу считывается п-разрядное число. Если по данному адресу не производится коррекция информации, то п-разрядное число с выходов основных запоминающих модулей 1 поступаег соответственно на первые входы соответствующих коммутаторов 3 и далее на выходные шины, так как на третьи входы коммутаторов 3 в этом случае с выходов соответствующих элементов 5 И подается нулевой управляющий сигнал, разрешающий прохождение информации с первых входов на выходные шины коммутаторов 3.

Предлагаемое устройство позволяет произвести коррекцию информации по несовпадающим адресам каждого из ш основных запоминающих модулей 1. Это означает, что по данному адресу возможна коррекция информации одного из m основных запоминающих модулей 1. При этом предварительно по данному адресу в основной запоминающий модуль 1 заносится единичная информация, а в дополнительный запоминающий модуль 4 по тому же адресу заносится правильная информация.

Рассмотрим как работает устройство в этом случае.

По определенному адресу в бдном из основных запоминающих модулей 1 записаны все единицы. При считывании инфорйа1ШГ С этого модуля на входь соответствующего элемента 5 И поступят все единичные сигналы. Одновременно на соответствующие первые входы соответствующего коммутатора 3 поступит та же информация. На выходе данного элемента 5 И появится единичный сигнал, который поступит на третий вход соответствующего коммутатора 3. В этом случае коммутатор 3 производит подключение вторых своих входов к выходным шинам 6. На вторых входах коммутатора 3 имеется информация, считанная по этому адресу из дополнительного запоминающего модуля 4. Таким образом, на выходные щины коммутатора поступит информация, которая была считана с дополнительного зaпoминaющefo модуля 4 и которая соответствует правильной информации.

Из рассмотрения работы ясно, что коррекция информации какого-либо основного запоминающего модуля 1 возможна лишь в случае, если п;о данному адресу в других основных запоминающих модулях 1 не записан единичный п-разряднь1Й кбд. В противном случае на выходах нескольких элементоаБ И появится единичный сигнал, по

которому соответствующие коммутаторы 3 подключают к выходным шянам выходы дополнительного запоминающего модуля 4,

0 в котором записана информация лишь одного корректируемого основного запоминающего модуля 1.

В случае, если по одному и тому же адресу в основных запоминающих модулях 1 записана во всех разрядах единичная информация и ее не нужно корректировать, то для правильной работы устройства необходимо предварительно по этому адресу в дополнительный запоминающий Модуль 4 записать п-разрядный единичный код. Тогда

0 при считывании информации на выходных шинах соответствующих коммутаторов 3 появится единичная информация, соответствующая той, которая записана по данному адресу в каждом основном запоминающем модуле 1.-1

Таким образом, данное устройство позволяет осуществить коррекцию записанной информации без замены модуля, в котором произощла ошибочная запись информации.

Формула изобретения

Постоянное запоминающее устройство, содержащее ш основных запомина:ющих модулей, отличаюи ееся Тем, что, с целью осуществления коррекции записанной информации в устройстве, оно содержит дополнительный запоминающий модуль, элементы И и коммутаторы по числу основных запоминающих модулей, при этом выходы каЖдОго Основного запоминающего модуля соединены соответственно с первыми входами соответствующих коммутаторов и входами элемента И, выходы дополнительного запоминающего модуля подключены к соответствующим вторым входам коммутаторов, третьи входы которых соединены с выходами соответствующих элементов И.

Источники информации, принятые вО внимание при экспертизе

Авторы

Даты

1980-09-30—Публикация

1977-05-27—Подача