НЕ, выход первого элемента И первой группы соединен с первым входом первого элемента ИЛИ, выходы остальных элементов И первой группы - со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ, единичные выходы разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов -И первой группы, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И первой группы и со входами третьего элемента ИЛИ, вторые входы элементов И первой группы соединены меладу собой и являются входом опроса устройства, выход /-ГО (/ 1-г-4) элемента ИЛИ группы через i-й элемент НЕ группы соединен с третьим входом (/+1)-го элемента И первой группы, дополнительно содержит вторую группу элементов И, счетный триггер, единичный выход которого соединен с первыми входами элементов И второй группы. Второй вход /-ГО элемента И второй группы соединен с выходом (t-M)-ro элемента |И первой группы, а выход i-ro элемента -И второй групы - с нулевым Ьходом (i-f 1)-го разряда входного регистра. Вход счетного триггера соединен с выходом второго элемента ИЛИ. Выходы первого и третьего элементов ИЛИ соответственно являются информационными и сигнальным выходами преобразователя.

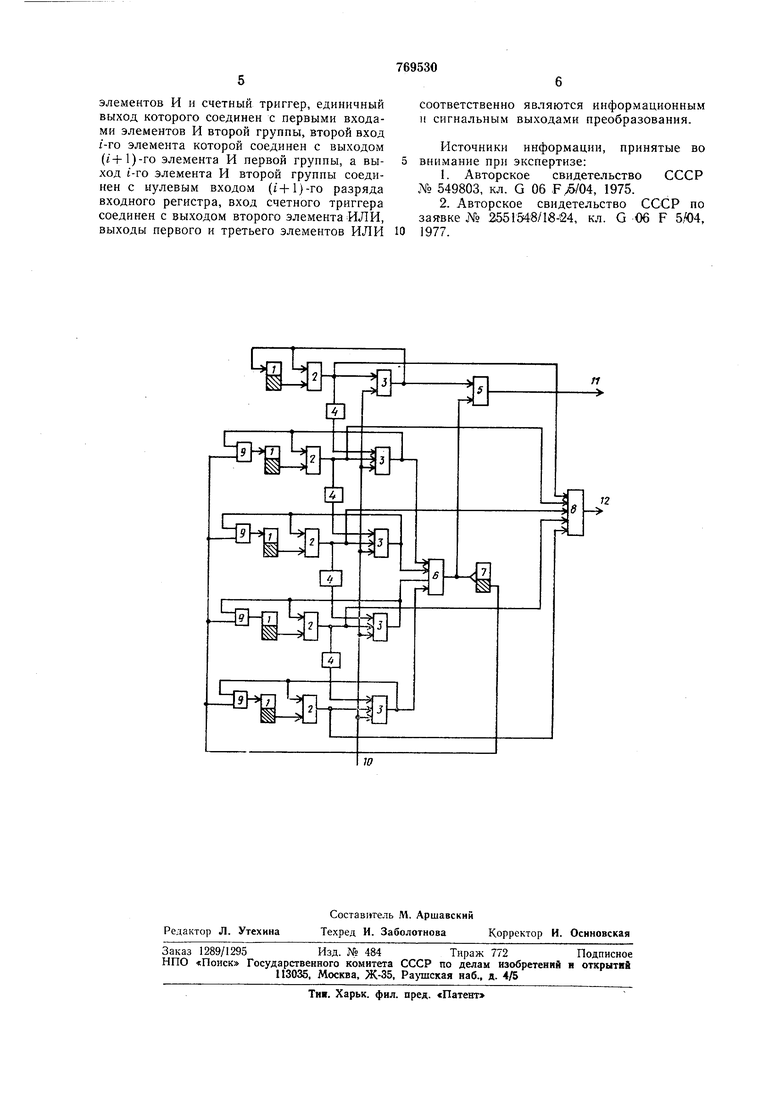

На чертеже представлена структурная схема преобразователя.

Он содержит входной регистр /, состоящий из триггеров, группу элементов ИЛИ 2, первую группу элементов И 3, группу элементов sHE 4, первьш и второй элементы ИЛИ 5 и 6, счетный триггер 7, третий элемент ИЛИ 8 и вторую группу элементов И 9.

Преобразователь работает следующим образом.

Если в триггер с весом «2°, соответствующий разряду входного регистра 1, записана «1, то при поступлении первого импульса опроса по входу 10 на второй вход элемента И первой группы соответствующего разряда на выходе элемента ИЛИ 5 формируется одиночный импульс, который поступает на информационный выход //. При этом второй элемент И 3 первой группы по третьему входу закрыт на время действия тактового импульса опроса сигналом с первого элемента НЕ 4 группы. Импульс, сформированный на выходе первого элемента И 3 первой группы, обнуляет триггер первого разряда. Если этот триггер в исходном состоянии сброщен, а взведен следующий триггер с весом «2, то по первому тактовому импульсу срабатывает второй элемент И 5 первой группы. При этом по заднему фронту тактового импульса срабатывает счетный триггер. Сигнал с единичного выхода триггера открывает по первому входу соответствующий элемент И 9 второй группы. Следующий тактовый импульс также проходит на выход элемента И 3 первой группы и через соответствующий элемент И 9 второй группы сбрасывает второй триггер входного регистра и по заднему фронту обнуляет счетный триггер. Лри этом элементы И 9 второй группы закрываются по первому входу. Таким образом, на выход элемента И 3 первой группы с весом «2 проходят два тактовых импульса, которые через элементы ИЛИ 5 и 5 поступают на информационный выход //,/ устройства. Опрос следующих элементов И 3 первой группы проводится аналогично.

Выходной код выдается в виде пачки

импульсов, равномерно распределенных во времени.

После опроса последнего эле.мента .И 3 первой группы, когда входной регистр примет нулевые значения во всех разрядах, на

выходе третьего элемента ИЛИ 8 формируется сигнал «(Конец преобразования, который поступает непосредственно на сигнальный выход /2 преобразователя. Таким образом, устройство позволяет

получать на выходе последовательный код в виде пачки импульсов, равномерно распределенных во времени при любой произвольной частоте поступающих на вход импульсов опроса.

Формула изобретения

Преобразователь двоично-десятичного кода Ii2222 в последовательный код, содержащий входной регистр, первую группу элементов И, первый, второй и третий элементы ИЛИ, группу элементов ИЛИ, группу элементов НЕ, выход первого элемента И первой группы соединен с первым входом первого элемента ИЛИ, вь1ходы остальных элементов И первой группы соединены со входами второго элемента ИЛИ, выход которого соединен со вторым входом первого элемента ИЛИ, единичные выходы

разрядов входного регистра соединены с первыми входами соответствующих элементов ИЛИ группы, вторые входы которых соединены с выходами соответствующих элементов И первой группы, выходы элементов ИЛИ группы соединены с первыми входами соответствующих элементов И первой группы и со входами третьего элемента ИЛИ, вторые входы элементов И первой группы соединены между собой и являются

входом опроса преобразователя, выход i-ro (i 4) элемента ИЛИ группы через -й элемент НЕ соединен с третьим входом {(-l-l)-ro элемента И первой группы, отличающийся тем, что, с целью повыщения

надежности, он содержит вторую группу

элементов И и счетный триггер, единичный выход которого соединен с первыми входами элементов И второй группы, второй вход /-ГО элемента которой соединен с выходом (i+l)-ro элемента И первой группы, а выход t-ro элемента И второй группы соединен с нулевым входом (i+l)-ro разряда входного регистра, вход счетного триггера соединен с выходом второго элемента-ИЛИ, выходы первого и третьего элементов ИЛИ

соответственно являются информационным и сигнальным выходами преобразования.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 549803, кл. G 06 F.04, 1975.

2.Авторское свидетельство СССР по заявке № 2551548/18-24, кл. G 06 F 5Ю4, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода"12222" B пОСлЕдОВАТЕльНый КОд | 1979 |

|

SU840878A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587642A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь @ -значного двоичного кода в @ -значный код | 1983 |

|

SU1087982A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоично-десятичного кода 12222 в унитарный код | 1977 |

|

SU746497A1 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

//

Авторы

Даты

1980-10-07—Публикация

1978-10-06—Подача