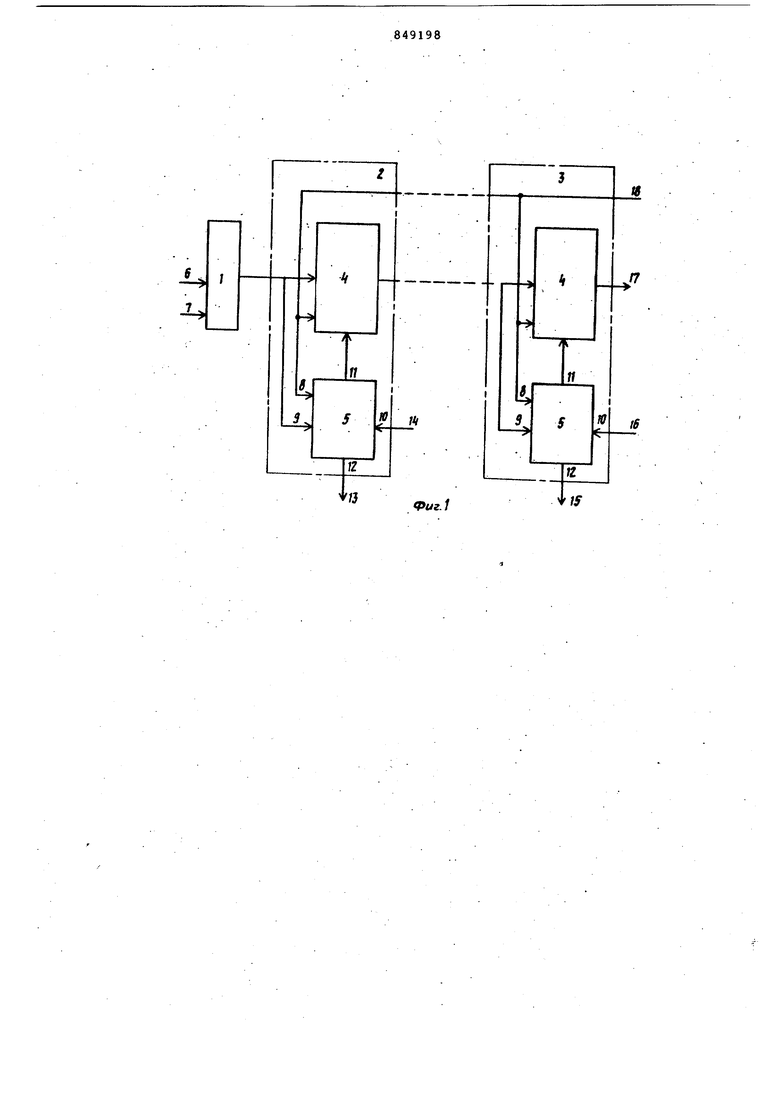

управляющим входом, преобразователя и соединен с управляющим входом, бло ка формирования двоичных эквивалентов, выход сумматора является выходом каскада, выход - п-го каскада я ляется выходом младшего разряда десяткчного исла и-двоичным выходом преобразователя Г2. ; Недостаток таких преобразователе состоит в низком быстродействии,являющемся следствием циклического ре .жима работы и использования последовательных кодов. Цель изобретения - увеличение быстродействия. Поставленная цель достигается тем, что в реверсивном преобразователе ДВОИЧНОГО кода в двоично-десятичный , содержащем регистр и п, (где п - число разрядов десятичного кода) последовательно соединенны каскадов преобразования, каждый из которых содержит сумматор и блок формирования двоичных эквивалентов двоичный выход которого соединен с первым входом сумматора, а десятичный выход является двоично-десятич ым выходом соответствующего разряд .реобразователя, второй вход сумматора является двоичным входом каскада и соединен с двоичным входом блока формирования двоичных эквивалентов, управляющий вход сумматора является управляющим входом преобра вателя и соединен с управляющим входом блока формирования двоичных эквивалентов, выход сумматора явля ется выходом каскада, первый вход регистра является двоичным входом преобразователя, а выход, регистра соединен с двоичным вхо.дом первого каскада, выход п-го каскада являем выходом младшего разряда десятично числа и двоичным выходом прес1бразо вателя, десятичные входы блоков формирования двоичных эквивалентов являются входами старших десятичны разрядов преобразователя, второй вход регистра является входом млад шего десятичного разряда преобразо вателя, причем блок формирования двоичных эквивалентов содержит схе сравнения, два шифратора двоичных эквивалентов, шифратор десятичного кода в двоично-десятичный, четыре группы элементов И, три группы эле ментов ИЛИ, элемент И, элемент НЕ и два дешифратора, причем, первый вход первого дешифратора соединен первым входом схемы сравнения и является двоичным входом блока фор рования двоичнйх эквивалентов, пер -ВЫХОД первого дешифратора соединен с первыми входами первых элементов И и ИЛИ первых групп , остальные во семь его выходов подключены к первым входам соответствующих элементов И первой и второй группИ элементов ИЛИ первой группы, вторые входы элементов И второй группы соединены с управляющим входом первого шифратора двоичных эквивалентов и с выходом меньше сравнения, выход больше которой соединен с первым входом элемента И и вторыми входами элементов И первой группы, вторые входы элементов ИЛИ первой группы соединены с выходами Второго дешифратора, вход которого является десятичным входом блока формирования двоичных эквивалентов, ВЫХОДЫ элементов И второй группы подключены к соответствующим входам первого шифратора двоичных эквивалентов и к первым входам соответствующих элементов ИЛИ второй группы, вторые входы которых соединены с выходами первых восьми элементов И первой группы, а выходы элементов ИЛИ второй группы соединены с первыми восемью входами шифратора десятичного кода в двоично-десятичный, девятый вход которого соединен с выходом десятого элемента И первой группы, выход шифратора десятичного кода в двоично-десятичный является десятичным выходом блока формирования двоичных эквивалентов, выходУ второ-го шифратора двоичных эквивалентов соединены с первыми входами соответствующих элементов И третье(| и четвертой групп и со вторым входом схемы сравнения, управляющий вход первого дешифратора является управляющим входом блока формирования двоичных эквивалентов и соединен со вторым входом элемента И и через элемент НЕ соединен со вторыми входами элементов И третьей группы, выход элементг( И соединен со вторыми входами элементов И четвертой группы, а выходы первого шифратора двоичных эквивалентов третьей и четвертой группы элементов И соответственно подключены к первым, вторым и третьим входам соответствующих элементов ИЛИ третьей группы, выходы которой являются двоичным выходом блока формирования двоичных эквивалентов. На фиг. 1 представлена структурная схема предлагаемого реверсивного преобразователя, н.а фиг. 2 структурная схема блока формирования двоичных эквивалентов. Реверсивный преобразователь двоичного кода в двоично-десятичный содержит регистр 1, каскад 2 старшего десятичного разряда, каскад 3 второго разряда десятичного числа, сумматор 4, блок 5 формирования двоичного эквивалента, двоичный вход 6 преобразователя, вход 7 преобразователя младшегр разряда десятичного числа, управляющие вход 8 блока формирования двоичных эквивалентов,двоичный вход 9 и десятичный вход 10 блока формирования двоичных эквивалентов, двоичный выход 11 и деся- I

тичный выход.12 блока формирования двоичных эквивалентов, выход 13 старшего десятичного разряда преобразователя, вход 14 старшего десятичного разряда преобразователя, выход 15 второго десятичного разряда преобразователя, вход 16 второго десятичного разряда преобразователя, выход 17 младшего разряда десятичного числа и двоичного числа, управляющий вход 18 преобразова,теля.

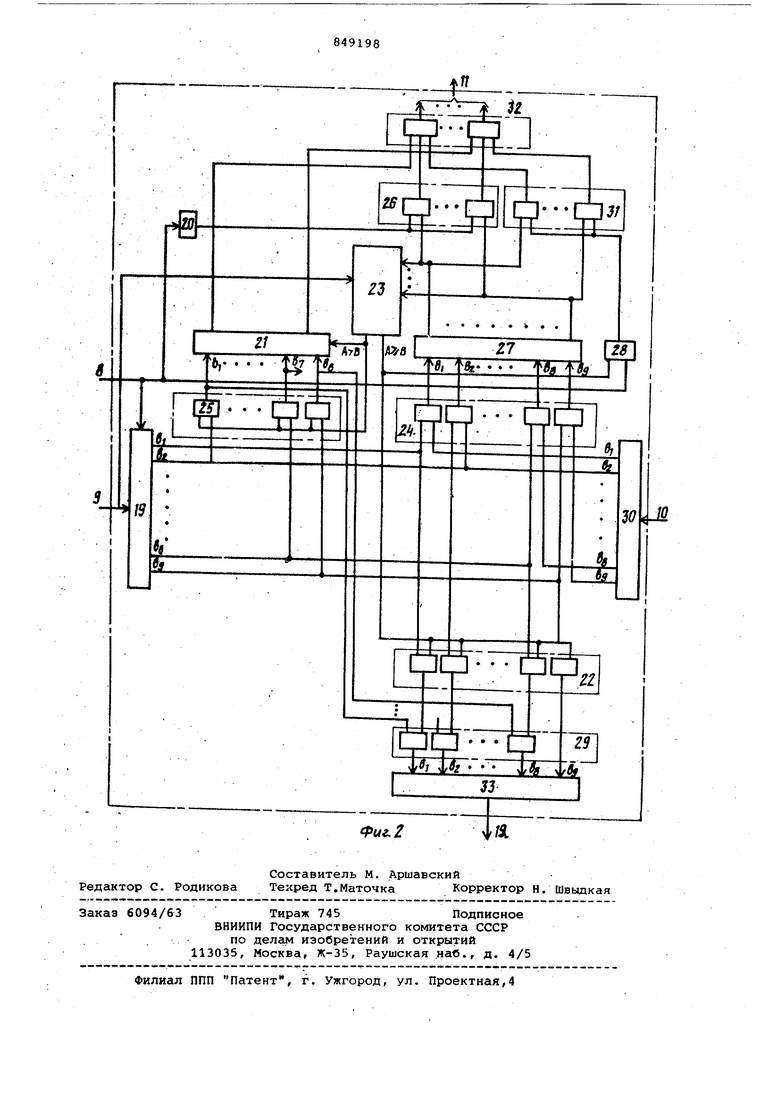

Блок формирования двоичных эквивалентов содержит первый дешифратор 19, элемент НЕ 20, первый шифратор 21 двоичных эквивалентов, первую, группу 22 элементов И, схему 23 сравнения, первую группу 24 элементов ИЛИ, вторую 25 и третью 26 группы элеме нтов И, второй шифратор 27 двоичных эквивалентов, элемент И 28 вторую группу 29 -элементов ИЛИ, второй дешифратор 30, четвертуюгруппу 31 элементов И, третью группу 32 элементов ИЛИ, шифратор 33 десятичного кода в двоично-десятичный.

Преобразователь работает следующим образом.

В режиме преобразования двоичного кода в двоично-десятичный на управляющий вход 18 подается сигнал ло-. гической единицы, который поступает на управляющий вход 8 блока 5 формирования двоичных эквивалентов, чем обеспечивается подача сигнала на вход переносаВ младший разряд и на входы старших разрядов, находящихся за пределами разрядности двоичных эквивалентов, комбинационкого сумматора 4 для получения дополнительного кода из обратного кода двоичного эквивалента. Двоичный код преобразуемого числа А заносится по входу 6 в регистр 1. С выхода, регистра 1 параллельным кодом число А подается на входы сумматора 4 и на вход 9 блока 5 формирования двоичных эквивалентов, относящихся к старшему разряду десятичного числа 2.

В блоке 5 формирования двоичных эквивалентов определяется и на первом выходе 11 формируется обратный код двоичного эквивалента В Ь 10 (где Ъ. 1,2. . .9; 0,1,2. ..:номер .десятичного разряда) со старшим числом Ь; из условия А В, С выхода 11 сформированный двоичный эквивалент подается на вход сумматора 4 и вычитается из преобразуемого двоичного числа А. Полученный остаток разности с сумматора 4 поступает на вхоД сумматора и двоичный вход блока формирования двоичных эквивалентов следующего каскада.

Кроме того, на выходе 13 первого каскада 2 в соответствии с выделенны числом Ь,- формируется двоично-десятичный код старшего десятичного разряда,Процесс формирования остатко

и двоично-десятичных кодов в следую щих десятичных разрядах происходит аналогично. Младший десятичный разряд получается непосредственно на выходе 17 четырех младших разрядов сумматора 4(п-1)-го каскада.,

В режиме обратного преобразования на управляющий вход 18 подается сигнал логического нуля, который поступает на вход 8 блока 5 формирования двоичных эквивалентов, запрещая ввод

0 числа по входу 9, на перенос в младший разряд и на входы старших разрядов, находящихся за пределами раз рядности двоичных эквивалентов,сумматора, так как в этом режиме про5исходит сложение чисел в прямом коде. Старший разряд преобразуемого двоично-десятичного числа подается на вход 14 первого каскада 2, а младший разряд - на вход 7, т.е. на четыре

0 младших разряда регистра 1. С регистра 1 младший разряд преобразуемого числа подается на вход cyNiMaTopa 4 и складывается с двоичн1з1м эквивалентом старшего десятичного разряда, который соответствует поданному на вход 14

5 двоично-десятичному коду. Полученная сумма с выхода сумматора 4 поступает на первый вход сумматора следующего каскада. Далее процесс формирования двоичного числа происходит аналогич0но.

Результат преобразования снимается с выхода 17 сумматора 4 (n-l)-ro каскада.

Рассмотрим работу блока формирова5ния двоичных эквивалентов в режиме преобразования двоичного кода в двот ично-десятичный.

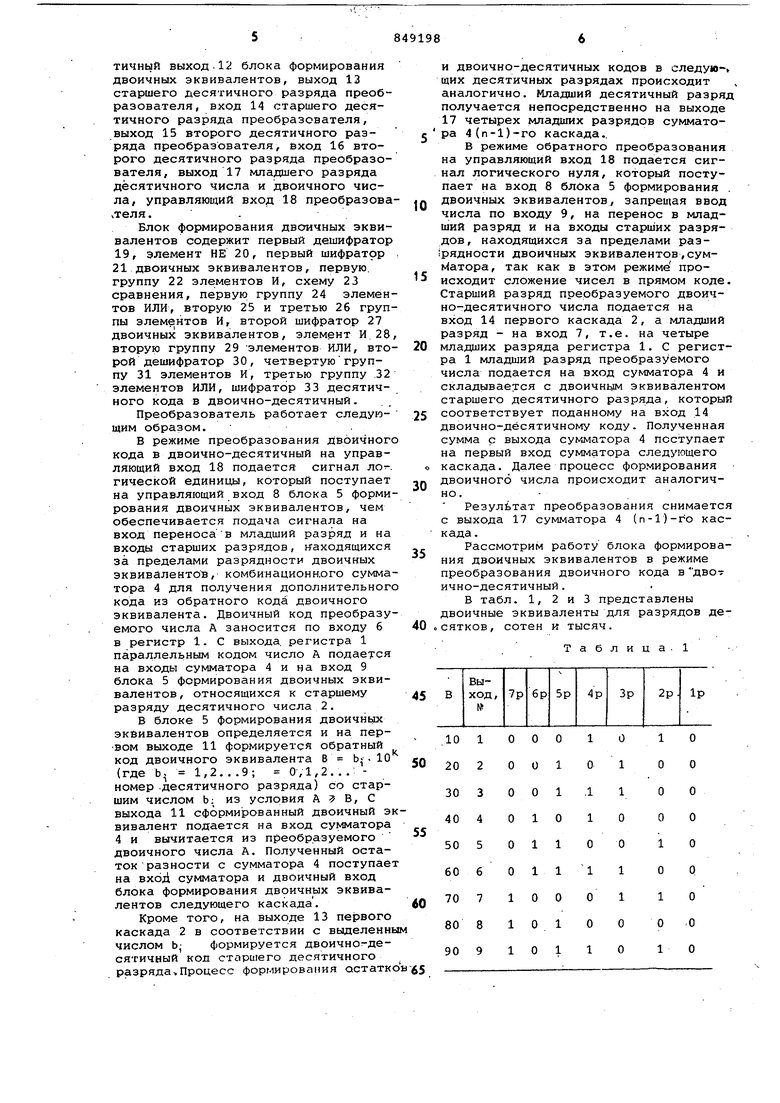

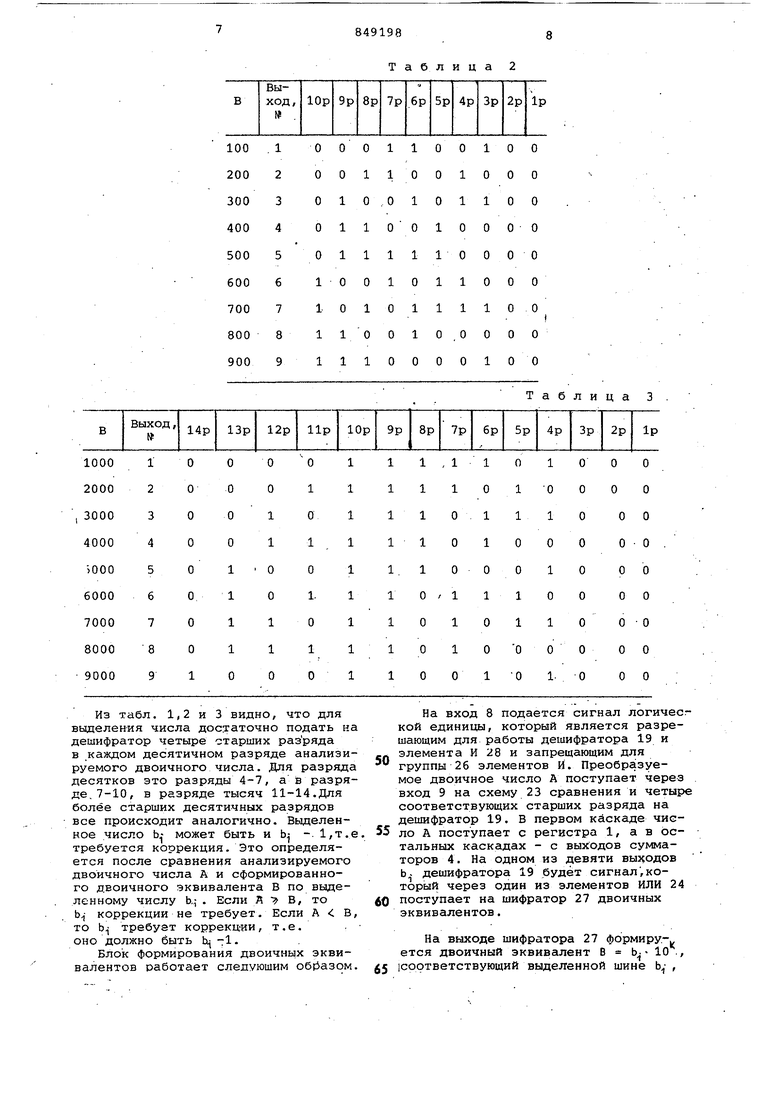

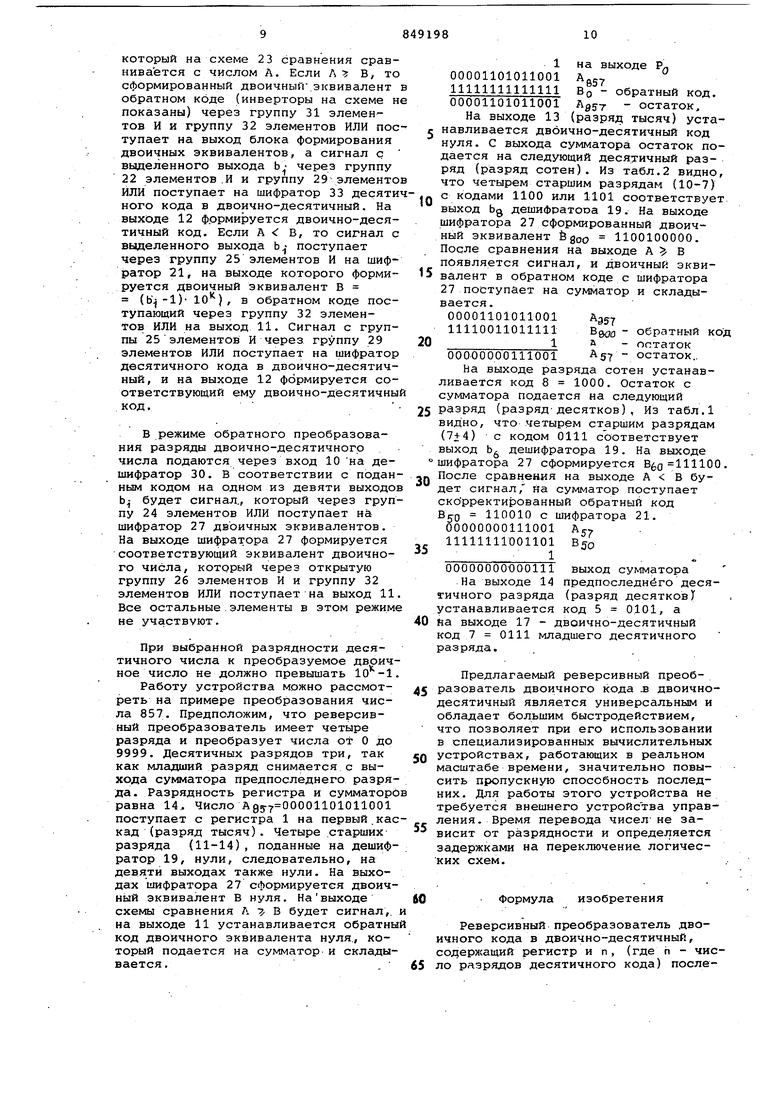

В табл. 1, 2 и 3 представлены двоичные эквиваленты для разрядов де0бсятков, сотен и тысяч.

Таблица. 1

45

50

55

40

65

Таблица 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1982 |

|

SU1097995A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Устройство для преобразования последовательного десятичного кода в последовательный двоичный код | 1974 |

|

SU636606A2 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

Из табл. 1,2 и 3 видно, что для выделения числа достаточно подать на дешифратор четыре старших разряда в каждом десятичном разряде анализируемого двоичного числа. Для разряда десятков это разряды 4-7, а в разряде. 7-10, в разряде тысяч 11-14.Для более старших десятичных разрядов все происходит аналогично. Выделенное число Ц- может быть и Ь -. 1,т.е требуется коррекция. Это определяется после сравнения анализируемого двоичного числа А и сформированного двоичного эквивалента В по выделенному числу Ь, . Если Л В, то коррекции не требует. Если А В, то Ъ требует коррекд-ии, т.е. оно должно быть Ц -1.

Блок формирования двоичнь х зквивалентов работает следующим образом.

Таблица 3

На вход 8 подается сигнал логичесгкой единицы, который является разрешающим для работы дешифратора 19 и

--J элемента И 28 и запрещающим для

группы 26 элементов И. Преобразуемое двоичное число А поступает через вход 9 на схему 23 сравнения и четыре соответствующих старших разряда на дешифратор 19. В первом каскаде число А поступает с регистра 1, а в остальных каскадах - с выходов сумматоров 4. На одном из девяти Ь- дешифратора 19 бУДет сигнал ,который через один из элементов ИЛИ 24

40 поступает на шифратор 27 двоичных эквивалентов.

На выходе шифратора 27 формируется двоичный эквивалент В 10 ., 5 соответствующий выделенной шине Ь , который на схеме 23 сравнения сравнивается с числом Л. Если Л В, то сформированный двоичный эквивалент обратном коде (инверторы на схеме н показаны) через группу 31 элементов И и группу 32 элементов ИЛИ пос тупает на выход блока формирования двоичных эквивалентов, а сигнал с выделенного выхода Ь через группу 22 элементов.И и группу 29-элементо ИЛИ поступает на шифратор 33 десяти ного кода в двоично-десятичный. На выходе 12 формируется двоично-десятичный код. Если А В, то сигнал с выделенного выхода поступает через группу 25 элементов И на шифратор 21, на выходе которого формируется двоичный эквивалент В (Ц-) 10), в обратном коде поступающий через группу 32 элементов ИЛИ на выход 11. Сигнал с группы 25 элементов И через группу 29 элементов ИЛИ поступает на шифратор десятичного кода в двоично-десятичный, и на выходе 12 формируется соответствующий ему двоично-десятичны код. В режиме обратного преобразования разряды двоично-десятичного числа подаются через вход 10 на дешифратор 30. В соответствии с подан ным кодом на одном из девяти выходов Ь будет сигнал., который через груп пу 24 элементов ИЛИ поступает на шифратор 27 двоичных эквивалентов. На выходе шифратора 27 формируется соответствующий эквивалент двоичного числа, который через открытую группу 26 элементов И и группу 32 элементов ИЛИ поступает на выход 11 Все остальные,элементы в этом режиме не участвуют. При выбранной разрядности десятичного числа к преобразуемое двоичное число не должно превышать 10-1. Работу устройства можно рассмотреть на примере преобразования числа 857. Предположим, что реверсивный преобразователь имеет четыре разряда и преобразует числа от О до 9999. Десятичных разрядов три, так как младший разряд снимается с выхода сумматора предпоследнего разряда. Разрядность регистра и сумматоро равна 14, Число Agerr OOOOllOlOllOOl поступает с регистра 1 на первый кас кад (разряд тысяч). Четыре старших разряда (11-14) , поданные на дешифратор 19, нули, следовательно, на девяти выходах также нули. На выходах шифратора 27 сформируется двоичный эквивалент В нуля. Навыходе схемы сравнения Л т- В будет сигнал,, на выходе 11 устанавливается обратны код двоичного эквивалента нуля., который подается на сумматор и складывается . на выходе Рд 00001101011001 657 11111111111111 BO - обратный код. 00001101011001 957 остаток. На выходе 13 (разряд тысяч) устанавливается двоично-десятичный код нуля. С выхода сумматора остаток подается на следующий десятичный разряд (разряд сотен). Из табл.2 видно, что четырем старшим разрядам (10-7) с кодами 1100 или 1101 соответствует выход Ьд дешифратооа 19. На выходе шифратора 27 сформированный двоичный эквивалент 6 goo 1100100000. После сравнения на выходе А В появляется сигнал, и двоичный эквивалент в обратном коде с шифратора 27 поступает на сумматор и складывается. 00001101011001 11110011011111 &оо обратный код и -остаток А5- -остаток,. 00000000111001 На выходе разряда сотен устанавливается код 8 1000. Остаток с сумматора подается на следующий разряд (разряд-десятков), Из табл.1 видно, что четырем старшим разрядам (7+4) с кодом 0111 соответствует выход bg дешифратора 19. На выходе шифратора 27 сформируется B Q 111100. После сравнения на выходе А В будет сигнал, йа сумматор поступает скорректированный обратный код В5-0 110010 с шифратора 21. 00000000111001 А 11111111001101 Bjo 00000000-000111 выход сумматора На выходе 14 предпоследнего десятичного разряда (разряд десятков У устанавливается код 5 0101, а на выходе 17 - двоично-десятичный код 7 0111 младшего десятичного разряда. Предлагаемый реверсивный преобразователь двоичного кода л двоичнодесятичный является универсальным и обладает большим быстродействием, что позволяет при его использовании в специализированных вычислительных устройствах, работающих в реальном масштабе времени, значительно повысить пропускную способность последних. Для работы этого устройства не требуется внешнего устройства управления. Время перевода чисел-не зависит от разрядности и определяется задержками на переключение логических схем. Формула изобретения Реверсивный преобразователь двоичного кода в двоично-десятичный, содержащий регистр и п, (где h - число разрядов десятичного кода) после|Довательно соединенных каскадов преобразования, каждый из которых содержит сумматор и блок формирования

двоичных эквивалентов, двоичный выход которого соединен с первым входом сумматора, а десятичный выход является двоично-десятичным выходом соответствующего разряда преобразователя, второй вход сумматора является двоичным входом каскада преобразования и соединен с двоичным входом блока формирования двоичных эквивалентов, управляющий вход сумматора является управляющим входом преобразователя и соединен с уп равляющим входом блока формирования двоичных эквивалентов, выход сумматора является выходом каскада преобразования, первый вход регистра явлется двоичным входом преобразовател а выход регистра соединен с двоичны входом первого каскада преобразования, выход п-ого каскада преобразования является выходом младшего разряда десятичного числа и двоичны выходом преобразователя, отличающийся тем, что, с целью повышения быстродействия, в нем десятичные входы блоков формирования двоичных эквивалентов являются входами старших десятичных разрядов преобразователя, второй вход регистра является входом младшего десятичного разряда преобразователя, причем блок формирования двоичных эквивалентов содержит схему сравнения, два шифратора двоичных эквивалентов , шифратор десятичного кода в двоично-десятичный,четыре группы элементов И, три группы элементов ИЛИ, элемент И, элемент НЕ и два дешифратора, причем первый вход первого дешифратора соединен с первым вхдом схемы сравнения и является двоичным входом блока формирования двоичных эквивалентов, первый выход первого дешифратора соединен с первыми входами первых элементов И и ИЛИ первых групп, остальные восемь его выходов подключены к первым входам соответствующих элементов И первой и второй групп и элементов ИЛИ первой группы, вторые входы элементов И второй группы соединены с управляющим входом перво.го шифратора двоичных- эквивалентов и выходом меньше схемы сравнения, выход больше которой соединен с первым входом элемента И и вторыми в одами элементов И первой группы, вторые входи элементов ИЛИ первой группы соединены с выходами второго дешифратора, вход которого является десятичным входом блока формирования двоичных эквивалентов, выходы элементов И второй, группы подключены к соответствующим входам Q первого шифратора двоичных эквивалентов и к первым входам соответствующих элементов ИЛИ второй группы, вторые входы которых соединены с выходами первых восьми элементов И |первой группы, а выходы элементов 5 «ИЛИ второй группы соединены с первыми восемью входами шифратора десятичного кода в двоично-десятичный, девятый цход которого соединен с выходом девятого элемента И первой 0 группы, выход шифратора десятичного кода в двоично-десятичный является ресятичным выходом блока формирования двоичных эквивалентов, выходы второго шифратора двоичных эквива5 лентЬв соединены с первыми входами соответствующих элементов И третьей и четвертой групп и со вторым входом схемы сравнения, управляющий вход первого дешифратора является управQ ляющим входом блока формирования двоичных эквивалентов и соединен со вторым входом элемента И и через элемент НЕ соединен со вторыми входами элементов И третьей группы, - выход элемента И соединен со вторыми входами элементов И- четвертой группы, а выходы первого шифратора двоичных эквивалентов третьей и четвертой группы элементов И соответственно подключены к первым,вторым и третьим входам соответствующих элементов ИЛИ третьей группы, выходы которых являются двоичным выходом блока формирования двоичных эквивалентов . ,

Источники информации, принятые во внимание при экспертизе

.. Авторское свидетельство СССР по заявке № 2759525,кл. G 06 F 5/02 10.04.79.

ПЗ

Фиг.1

Авторы

Даты

1981-07-23—Публикация

1979-10-26—Подача