1

Изобретение относится к вычислительной технике и может быть использовано для электронной цифровой вычислительной системы, выполненной на функциональных узлах с большой степенью интеграции.

Известны запоминающие устройства (ЗУ, используемые в цифровых вычислительных системах для надежного воспроизведения информации в условиях отказов 1.

Наиболее близким техническим решением к данному изобретению является запоминаюш.ее устройство, содержащее регистр адреса, соединенный через дешифраторы адреса с накопителями, к которым подключены соответствующие регистры слова, блока поразрядного сравнения, соединенные непосредственно и через элементы И с соответствующими регистрами слова, один из которых через элемент ИЛИ соединены с выходным регистром, подключенным к блоку местного управления и накопителям 2.

В этом ЗУ для обеспечения надежной работы в условиях отказов производится запись и чтение обратных кодов считанных из одноименных ячеек накопителей слов с последующей поразрядной выдачей. Однако, при наличии сбоев в разрядах считанных

слов правильная работа такого ЗУ невозможна.

Целью изобретения является повышение надежности работы ЗУ.

Поставленная цель достигается тем, что

устройство содержит дополнительный регистр слова, счетчик, дополнительный дешифратор и блок контроля, вход которого соединен через один из блоков поразрядного сравнения с входом счетчика, подключенного через дополнительный дешифратор к входу дополнительного регистра слова, выходы которого соединены с соответствующими регистрами слова, выходы блока контроля соединены с входами соответствующих регистров слова, блоков поразрядного сравнения, блока местного управления и выходным регистром.

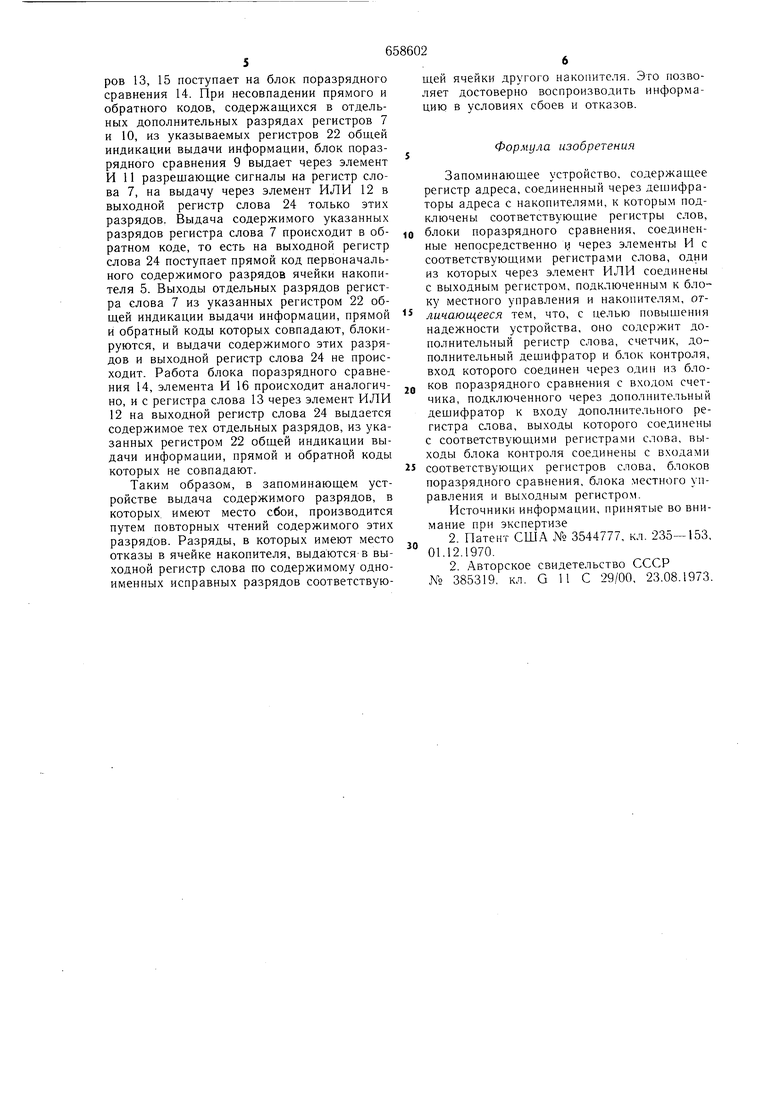

На чертеже представлена функциональная блок-схема устройства.

Устройство содержит регистр адреса I с информационным входом 2. Выход регистра адреса 1 соединен через дешифраторы адреса 3 и 4 с накопителями 5 и 6 соответственно. Накопитель 5 соединен с регистром слова 7, один выход которого соединен с блонами поразрядного сравнения 8 и 9 и регистром слова 10. Выход регистра слова 10 соединен с блоком поразрядного сравнения 9, выход которого соединен через элемент И 11 с одним управляющим входом регистра слова 7, другой выход регистра слова 7 соединен с элементом ИЛИ 12. Накопитель 6 соединен с регистром слова 13, один выход которого соединен с блоками поразрядного сравнения 8, 14 и регистром слова 15. Выход регистра слова 15 соединен с блоком поразрядного сравнения 14, выход которого соединен через элемент И 16 с одним управляющим входом регистра слова 13, другой выход регистра слова 13 соединен с элементом ИЛИ 12. Один выход блока поразрядного сравнения 8 соединен через элемент И 17 с входом регистра слова 7, а другой - через счетчик 18, и дополнительный дещифратор 19 с дополнительным регистром слова 20, два выхода которого соединены с управляющими входами регистров слова 7 и 13 соответственно. Третий выход блока поразрядного сравнения 8 соединен с блоком контроля, состоящим- из регистра 21 текущей индикации выдачи информации, регистра 22 общей индикации выдачи информации и блока 23 определения окончания выдачи информации. Один из выходов регистра 21 текущей индикации выдачи информации соединен с управляющим входом регистра слова 7. Другой выход 21 текущей индикации выдачи информации соединен с входом регистра 2-2 общей индикации выдачи информации, два выхода которого соединены с управляющими входами блоков поразрядного сравнения 9 и 14 соответственно, третий и четвертый выходы соединены с регистрами слова 7, 10 и регистрами слова 13, 15 соответств.енно, а пятый выход соединен с блоком 23 определения окончания выдачи информации. Выход блока 23 определения окончания выдачи информации соединен с первым входом выходного регистра слова 24, выход которого соединен с накопителем 5 и 6. Элемент ИЛИ 12 соединен со вторым входом выходного регистра слова 24, имеющим информационные вход 25 и выход 26. Дополнительный регистр слова 20 и блок 23 определения о-кончания выдачи соединены с входами блока местного управления 27, имеющий вход 28 и выход 29. Блок местного управления 27 соединен с управляющими входами регистра адреса 1, накопителей 5, б, элементов И 11, .16, 17, регистров слова 7, 10, 13, 15, счетчика 18, регистра 21 текущей индикации выдачи информации, регистра 22 общей индикации выдачи информации, выходного регистра слова 24. Запоминающее устройство работает следующим образом. Для обращения к ячейке запоминающего устройства адрес ее необходимо подать на вход 2 регистра адреса 1. При записи слово, предварительно записанное по входу 25 на выходной регистр слова 24, записывается в соответствующие одноименные ячейки накопителей 5, 6. Слова, считанные из соответствующих одноименных ячеек накопителей 5, б принимаются на регистры слова 7, 13 соответственно. Блок поразрядного сравнения 8 производит сравнение одноименным разрядов регистров слова 7, 13 и, в случае совпадения их содержимого, выдает соответствующие сигналы в регистры 21 текущей индикации выдачи информации, который разрещает выдачу указанным разрядам с регистра слова 7 на выходной регистр слова 24. Регистр 21 текущей индикации выдачи информации не разрещает выдачу разрядов, содержимое которых не совпало (например в результате сбоев по этим разрядам). Информация о выдаче разрядов, содержащаяся на регистре 21 текущей индикации выдачи информации, накапливается на регистре 22 общей индикации выдачи информации. Если регистр 22 общей индикации выдачи информации указывает, что не все разряды выданы, то блок 23 определения окончания выдачи информации обеспечивает повторное чтение из тех же одноименных ячеек накопителей 5, 6. Повторные чтения с последующим сравнением и выдачей производятся до тех пор, пока на регистре общей индикации выдачи информации 22 не будет зарегистрирована выдача всех разрядов. Указанная ситуация определяется блоком 23 определения окончания выдачи информации, которая при этом разрещает выдачу слова из выходного регистра слова 24 на выход 26. Количество повторных чтений подсчитывается счетчиком 18, содержание которого контролирует дополнительный дещифратор 19. После -определенного количества выдач (в случае отсутствия разрещения выдачи из блока 23 определения окончания выдачи информации предполагается, что несовпадение определенных разрядов произощло в результате отказов по этим разрядам) включается дополнительный регистр слова 20, который выдает управляющие сигналы на регистры 7, 13 и в блок местного управления 27. Содержи.мое разрядов регистров 7 и 13, указанных регистром 22 общей индикации выдачи информации, передается в регистры 10 и -15 соответственно. В те же ячейки накопителей 5 и 6 производится запись обратных кодов содержимого разрядов регистров 7 и 13, указываемых регистром 22 общей индикации выдачи информации, с последующим считыванием этих кодов на регистры 7 и 13. Содержимое разрядов, указываемых регистром 22 общей индикации выдачи информации, с регистров 7, 10 поступает на блок поразрядного сравнения 9, а с регистров 13, 15 поступает на блок поразрядного сравнения 14. При несовпадении прямого и обратного кодов, содержащихся в отдельных дополнительных разрядах регистров 7 и 10, из указываемых регистров 22 общей индикации выдачи информации, блок поразрядного сравнения 9 выдает через элемент И 11 разрешающие сигналы на регистр слова 7, на выдачу через элемент ИЛИ 12 в выходной регистр слова 24 только этих разрядов. Выдача содержимого указанных разрядов регистра слова 7 происходит в обратном коде, то есть на выходной регистр слова 24 поступает прямой код первоначального содержимого разрядов ячейки накопителя 5. Выходы отдельных разрядов регистра слова 7 из указанных регистром 22 общей индикации выдачи информации, прямой и обратный коды которых совпадают, блокируются, и выдачи содержимого этих разрядов и выходной регистр слова 24 не происходит. Работа блока поразрядного сравнения 14, элемента И 16 происходит аналогично, и с регистра слова 13 через элемент ИЛИ 12 на выходной регистр слова 24 выдается содержимое тех отдельных разрядов, из указанных регистром 22 общей индикации выдачи информации, прямой и обратной коды которых не совпадают.

Таким образом, в запоминающем устройстве выдача содержимого разрядов, в которых имеют место сбои, производится путем повторных чтений содержимого этих разрядов. Разряды, в которых имеют место отказы в ячейке накопителя, выдаются в выходной регистр слова по содержимому одноименных исправных разрядов соответствующей ячейки другого накопителя. Это позволяет достоверно воспроизводить информацию в условиях сбоев и отказов.

Формула изобретения

Запоминающее устройство, содержащее регистр адреса, соединенный через дешифраторы адреса с накопителями, к которым подключены соответствующие регистры слов, блоки поразрядного сравнения, соединен0ные непосредственно и через элементы И с соответствующими регистрами слова, одни из которых через элемент ИЛИ соединены с выходным регистром, подключенным к блоку местного управления и накопителям, огличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный регистр слова, счетчик, дополнительный дешифратор и блок контроля, вход которого соединен через один из блоков поразрядного сравнения с входом счет0чика, подключенного через дополнительный дешифратор к входу дополнительного регистра слова, выходы которого соединены с соответствующими регистрами слова, выходы блока контроля соединены с входами

5 соответствующих регистров слова, блоков поразрядного сравнения, блока местного управления и выходным регистром.

Источники информации, принятые во внимание при экспертизе

2. Патент США № 3544777, кл. 235-153,

0 01.12.1970.

2. Авторское свидетельство СССР № 385319. кл. G 11 С 29/00, 23.08.1973.

am 27

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1075312A1 |

| Запоминающее устройство с автономным контролем | 1978 |

|

SU780049A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Резервированное запоминающее устройство | 1975 |

|

SU619966A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385319A1 |

| Программируемый контроллер | 1989 |

|

SU1725182A1 |

Г

« p.

2S

Авторы

Даты

1979-04-25—Публикация

1977-03-17—Подача