Изобретение относится к области икроэлектроники и может быть использовано при построении интегральных схем запоминающих устройств с фазомпульсным представлением информации.

Известны запоминающие элементы, содержащие регистр сдвига с переноом заряда, к выходу которого присоеинен инвертор.

Недостатком таких устройств являтся ограниченное время хранения нформации.

Известен также запоминающий элемент, содержащий регистр сдвига на основе приборов с переносом заряда с вумя тактовыми шинами и выходной транзистор, сток которого соединен со входом регистра сдвига.

Данное устройство является ближайшим к изобретению по технической сущности и достигаемому результату.

Его недостаток заключается в том, что оно не позволяет оперативно изменять хранимую информацию, так как для перезаписи информации требуется предварительное обнуление запоминающего элемента, для чего необходимо, по крайней мере, число периодов управляющего направления, равное количеству разрядов регистра сдвига, и предварительное формирование фазоимпульсного кода записываемого числа.

Целью изобретения является повьш1екие скорости перезаписи информации.

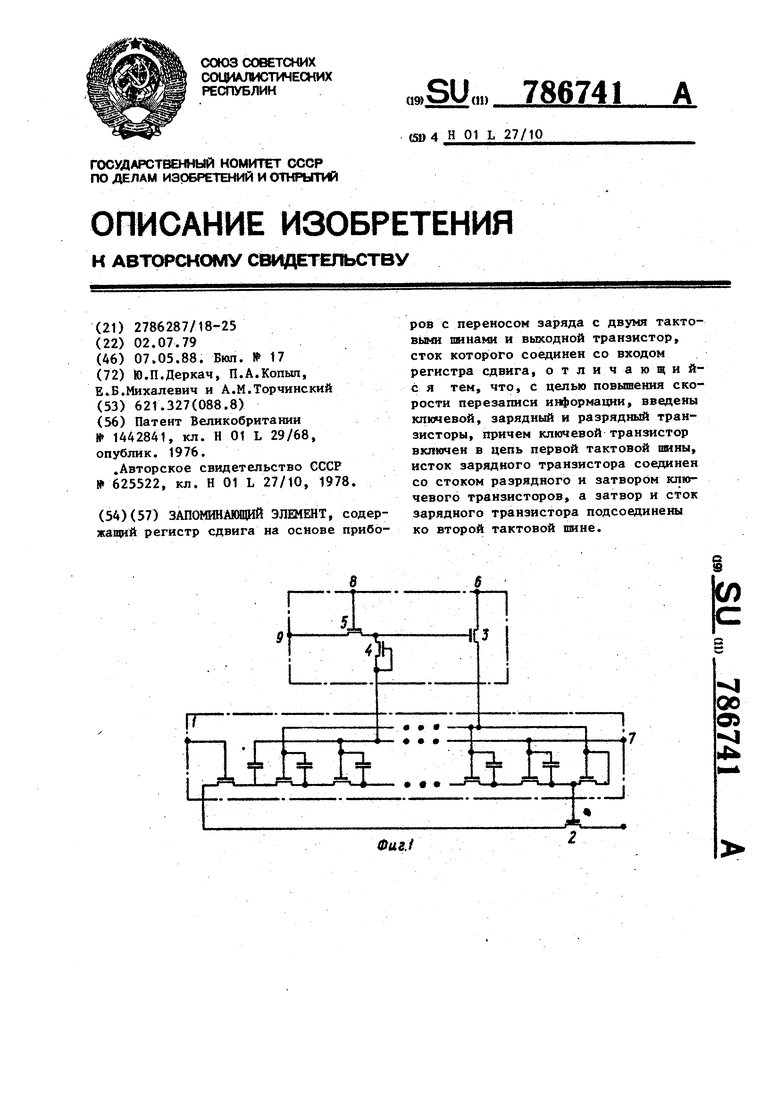

Указанная цель достигается тем, что в запоминающий элемент, содержащий регистр сдвига на основе приборов с переносом заряда с двумя тактовыми пшнами и выходной транзистор, сток которого соединен со входом регистра сдвига, введены ключевой зарядный и разрядный транзисторы, причем ключевой транзистор включен в цепь первой тактовой шины, исток зарядного соединен со стоком разрядного и затвором ключевого транзистора, а затвор и сток зарядного транзистора подсоединены ко второй тактовой шине.

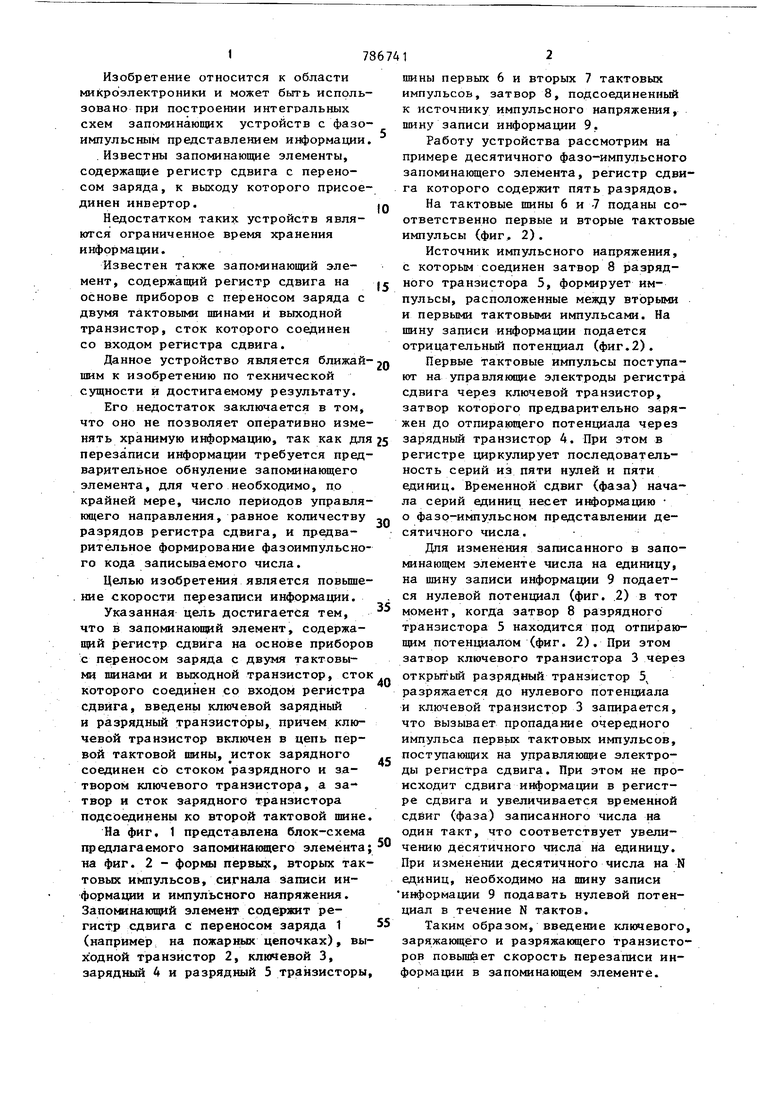

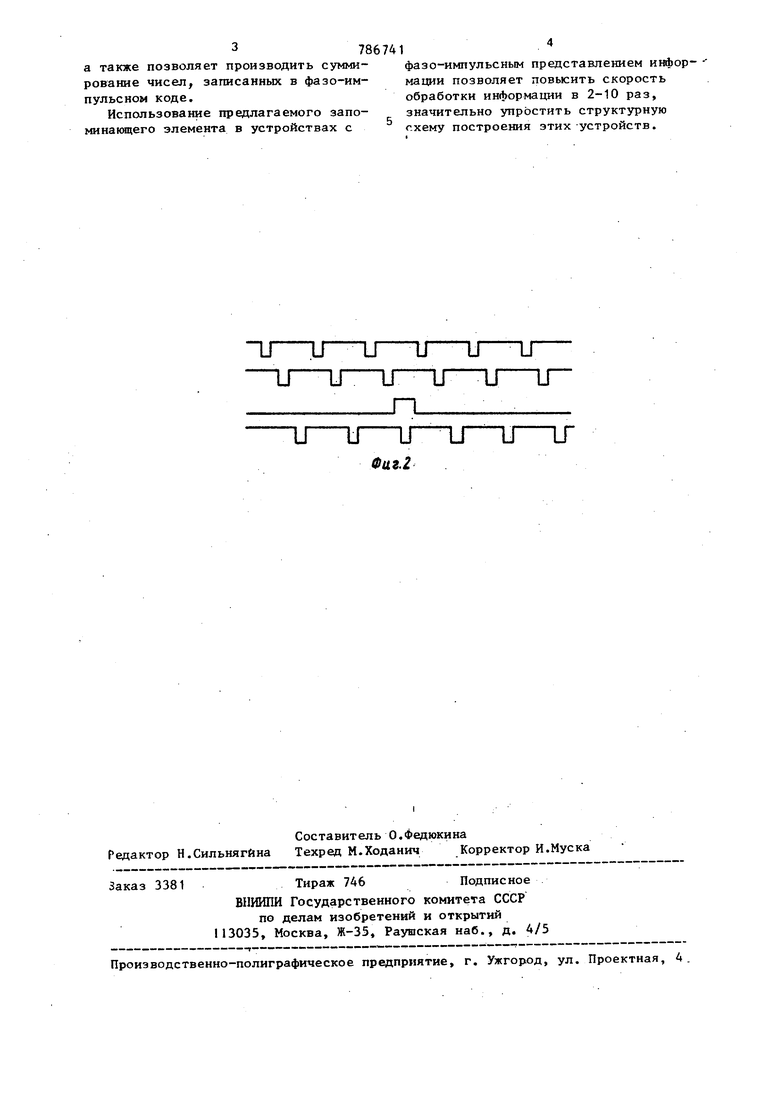

На фиг, 1 представлена блок-схема предлагаемого запоминающего элемента; на фиг. 2 - формы первых, вторых тактовых импульсов, сигнала записи инФорма1щи и импульсного напряжения. Запоь«наю1щ й элемент содержит регистр сдвига с переносом заряда 1 (например на пожарных цепочках), выходной транзистор 2, ключевой 3, зарядный 4 и разрядный 5 транзисторы.

шины первых 6 и вторых 7 тактовых импульсов, затвор 8, подсоединенный к источнику импульсного напряжения, шину записи информации 9.

Работу устройства рассмотрим на примере десятичного фазо-импульсного запоминающего элемента, регистр сдвига которого содержит пять разрядов.

На тактовые шины 6 и -7 поданы соответственно первые и вторые тактовы импульсы (фиг. 2).

Источник импульсного напряжения, с которым соединен затвор 8 разрядного транзистора 5, формирует импульсы, расположенные между вторыми и первыми тактовыми импульсами. На шину записи информации подается отрицательньй потенциал (фиг.2).

Первые тактовые импульсы поступают на управляющие электроды регистра сдвига через ключевой транзистор, затвор которого предварительно заряжен до отпирающего потенщ1ала через зарядный транзистор 4. При этом в регистре циркулирует последовательность серий из пяти нулей и пяти единиц. Временной сдвиг (фаза) начала серий единиц несет информацию о фазр-импульсном представлении десятичного числа,

Для изменения записанного в запоминающем элементе числа на единицу, на шину записи информации 9 подается нулевой потенциал (фиг. 2) в тот момент, когда затвор 8 разрядного транзистора 5 находится под отпирающим потенциалом (фиг. 2). При этом затвор ключевого транзистора 3 через открьп ый разрядный транзистор 5 разряжается до нулевого потенциала и ключевой транзистор 3 запирается, что вызывает пропадание очередного импульса первьк тактовых импульсов, поступакяцих на управляющие электроды регистра сдвига. При этом не происходит сдвига информации в регистре сдвига и увеличивается временной сдвиг (фаза) записанного числа на один такт, что соответствует увеличению десятичного числа на единицу. При изменении десятичного числа на N единиц, необходимо на шину записи информации 9 подавать нулевой потенциал в течение N тактов.

Таким образом, введение ключевого заряжающ|его и разряжающего транзисторов повьшйет скорость перезаписи информации в запоминакнцем элементе.

а также позволяет производить суммирование чисел, записанных в фазо-импульсном коде.

Использование предлагаемого запоминающего элемента в устройствах с

фазо-импульсным представлением информации позволяет повьюить скорость обработки информации в 2-10 раз, значительно упростить структурную схему построения этих-устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Регистр сдвига | 1985 |

|

SU1298806A1 |

| Регистр сдвига | 1988 |

|

SU1539842A1 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Динамический регистр сдвига на МДП-транзисторах | 1986 |

|

SU1341682A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ, содержащий регистр сдвига иа основе приборов с переносом заряда с двумя тактовыми шинами и выходной транзистор, сток которого соединен со входом регистра сдвига, отличающийся тем, что, с целью повышения скорости перезаписи информации, введены ключевой, зарядный и разрядный транзисторы, причем ключевой транзистор включен в цепь первой тактовой шины, исток зарядного траизистора соединен со стоком разрядного и затвором ключевого транзисторов, а затвор и сток зарядного транзистора подсоединены ко второй тактовой шине. (Л 00 Од sj 4

Авторы

Даты

1988-05-07—Публикация

1979-07-02—Подача