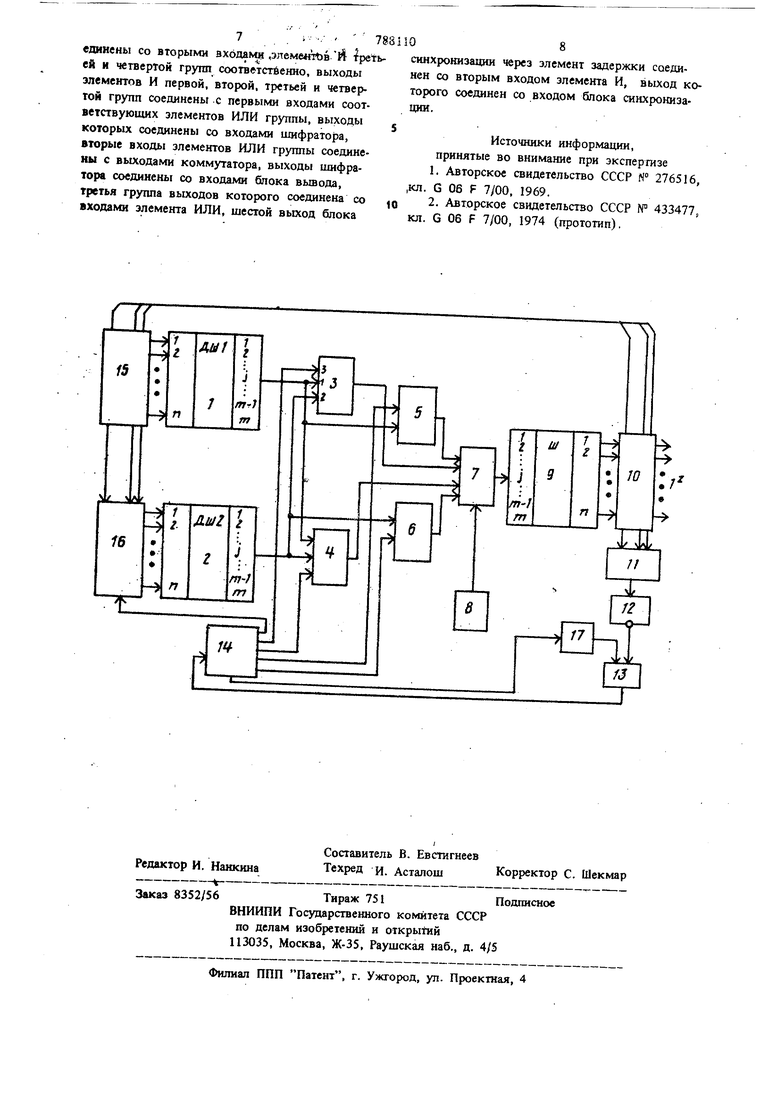

Изобретение относится к автоматике и вычислительной технике и может быть использовано для получения управляющих сигналов в дискретных системах автоматизации. Известен логический автомат, работа которого осуществляется по заданной программе. Имеющиеся в нем блок ввода переменных, блок памяти, блок задержек подают сигналы непосредственно и через злементы НЕ на программоноситель 11. Недостатками автомата являются ограниченность функций управления, возникающая из-за того, что преобразование входной информации в выходную происходит с помощью программо носителя и считьтающего устройства, считьшание информации с программоносителя, содержа щего программу, обуславливающее жесткую неизменяемую последов гельность образования управляющих воздействий; недостаточно полны контроль правилыюсти срабатьшания автомата. Наиболее близким к изобретению техническим рещением является логический автомат, содержащий блок памяти, блок элементов заде жки, блок вьгоода,первая группа выходов которого является выходом устройства, элемент ИЛИ, выходом соединенный через элемент НЕ с первым входом элемента И, программоноситель, входы блоков вьшода, элементов зааержкн, блока памяти соединены с соответствующими выходами программоносителя, первый н второй входы блока ввода являются входом устройства, а третий и четвертый входы соединены с выходами блока элементов задержки и блока памяти соответственно, выходы блока ввода соединены со входами программоносителя, прямые выходы программоносителя соединены со входами элемента ИЛИ, выход которого соединен с первым входом элемента И, инверсные выходь программоносителя соединены со входами элемента И, выход которого через элемент НЕ соединен со вторым входом элемента И, выходом через программоноситель соеди 1ен со входами блоков вьшода, элементов задержки н блока памяти 2. Основной недостаток логического автомата - ограниченность функций управления из-за наличия жесткой неизменной программы, а также низкие скоростные характеристики. 37 Цель изобретения - расширение функциональных возможностей устройства за счет отработки заданной программы как в прямом, так и в обратном направлениях. Поставленная цель достигается тем, что уст ройство содержит первый и второй дешифраторы, первую, вторую, третью и четвертую гругшы элементов И, группу элементов ИЛИ, шифратор, коммутатор, элемент задержки, бло синхронизации, причем вторая группа выходов блока вьшода соединен со входами блока элементов задержки, первая группа выходов которого соединена со входами первого дешифратора, а вторые выходы - с информационными входами блока памяти, выходами соединешюго со входами второго дешифратора, выходы первого дешифратора соединены с первыми входами элементов И первой, второй и третьей групп, выходы второго дешифратора соединены с первыми входами элементов И четвертой группы и со вторыми в ходами, элементов И первой и второй групп первый выход блока синхронизации соединен с управляющим входом блока памяти, второй и третий выходы блока синхронизации соединены с третьими входами элементов И первой и второй групп соответстве1шо, четвертый и пятый выходы блока синхронизации соединены со вторыми входами элементов И третьей и четвертой групп соответственно, выходы элементов И первой, второ третьей и четвертой групп соедзшены с первыми входами соответствующих элементов ИЛИ группы, выходы которых соединены со входами шифратора, вторые входы элементов ИЛИ группы соединены с выходами коммутатора, выходы шифратора соединены со входами бло ка вьтода, третья группа выходов которого соеданена со входами элемента ИЛИ, шестой выход блока синхронизации через элемент задержки соединен со вторым входом элемента И, выход которого соединен со входом блока синхронизации. На чертеже представлена блок-схема устрой ства. Устройство содержит первый и второй дешифраторы 1 и 2, первую, вторую, третью и четвертую группы элементов.. И 3-6, группу элементов ИЛИ 7, коммутатор 8, шифратор 9 блок 10 вьтода, элемент ИЛИ 11, элемент НЕ 12, элемент И 13, блок 14 синхронизации блок 15 элементов задержки, блок 16 памяти элемент 17 задержки. Устройство работает следующим образом. Программу, подлежащую отработке, задают в виДе матрицы, число строк которой равно числу тактов программы, а число столбцов - числу переменных. Элементы исходной матриц отображают в структуре дешифраторов и шиф тора с помощью наборных полей. Логический автомат работает по заданной программе, выдавая на вьиодах последовательности комбина1Щй сигналов, определенные последовательностью строк в матрице. Информация, получаемая на выходах блока 10 вьшода в каждый момент времени определяется двумя группами сигналов: первая группа сигналов соответствует информации, полученной на выходах автомата в предыдущий (т - Г)-ый момент времени, а вторая группа сигналов - информации, полученной в (г-2)ой момент времени. Обе информации сохраняются до настоящего времени т, причем информация (т-1)-го момента сохраняется с помощью элементов задержки. позволяет автомату работать в требуемом масщтабе времени. На выходах Z автомата в каждом такте т работы (в каждом рассматриваемом моменте времени т) появляется комбинация сигналов, определяемая как Z-v Zt,y), где Z/.. , Z j;-2N - комбинации сигналов, полученные на выходах автомата соответственно в (г-1) и (г-2) тактах. Для получения сигналов 2 блок 16 памяти посылает на выходы дешифратора 2 сохраненную информацию о (г-2)-м такте, а блок 15 элементов задержки посылает в дешифратор 1 информацию о (r-I)-M такте, задержанную до настоящего момента. На соответствующих выходах дешифраторов 1 и дешифратора 2 появляются сигналы, которые поступают на соответствующие входы элементов И групп 3-6. При правильной работе логического автомата на вторые входы элементов И групп 5 и 6 подаются нули, так как сигнал на выходе элемента И 13 отсутствует. Сигнал с выхода одного из элементов И групп 3 или 4 проходя через соответствующий элемент ИЛИ группы 7 поступает на вход шифратора 9 и размножается: на его выходах в комбинацию п двоичных сигналов, соответствующую такту т. Сигналы этой комбинации поступают на входы блока 15 задержки. Элементы блока 15 задерживают сигналы такта г на время t и заносят в течение этого времени сигналы (т-1)-го такта с блока 15 задержки в блок 16 памяти, после чего пропускают сигналы такта г на входы Д|цшфратора 1, Таким образом, в следующий момент времеш на входах дешифратора 1 появляется комбинация сигналов такта г, а на входах деш:ифратора 2 - комбинация сигналов (г-1)-го такта. На выходах автомата в этот момент времени возникает комбинация сигналов, определяемая2(14.1) ZfZ(.t-i). Эта комбинация поступает на входы блока 15 задержки и осушествляется следующий такт работы. 578 Число тактов, заданное программой, составляет один цикл работь автомата, Так как соединения выходов дешифраторов с входами элементов И групп 3 и 4 образуют кольцевую схему, то после отработки последнего такта цикла j m выполняется следующий такт, в котором комбинации сигналов на выходах соответствуют первой строке матрицы. Циклы могут повторяться бесконечно. Комбинации на выходах автомата можно получать как в прямой, так и в обратной последовательности. , Контроль информации и возможная обработка ложной информации происходит следующим образом. Для прохода сигналов через элементы И групп 3 и 4 необходимо, чтобы обе комбинации сигналов, поступившие одновременно на входы деишфраторов, соответствовали двум соседним строкам заданной матрицы. Кроме того, из двух соседних комбинаций, появившаяся на входах дешифратора 1, должна соответствовать комбинации (т-1)-го такта, а комбинация, появившаяся на входах дешифратора 2 комбинации сигналов (т-2)-го такта. Это возможно в том случае, если программа отрабатывается безошибочно, соответственно заданной матрице (как в прямом, так и в обратном направлении) Это также возможно, если на входах обоих дешифраторов появляются одновременно ошибочные, Г.-Э соседние комбр;нации сигналов (для неполных дешифраторов только те, которые входят в набор сигналов, реализуемых, дешифраторами) и только такие, перестановка которых соответстаует Е--бранному направле1шю програм мы. Выявление ошибки и коррекш1Я программы происходят следующим образом. При безошибоч ной работе автомата сигналы, появляющиеся в каждом такте на третьей группе выходов блока вьшода, отключают, через элемент ИЛИ элемент НЕ 12, находившийся до этого во вкл ченном состоянии. Сигнал, подаваемый к этому времени через элемент 17 задержки на второй вход элемента И 13, включает его. В том случае, если в блок задериоси поступает вместо правильной (j + 1)-ой комбинации ошибочная комбинация сигналов, то автомат оказьшает заяштное действие и в момент подачи тактирующего сигнала на выходе элемента И 13 появляется сигнал ошибки. Сигнал ошибки поступает в блок 14 синхронизации, проходя через второй элемент И 20, на втором входе которого присутствует сигнол с нулевого выхода триггера 19, через элемент ИЛИ 21, поступает на счетный вход триггера. Триггер переключается, и на его ешпшчном выходе появляется сигнал. Этот сигнал проходит на вторые входы элементов И групп 5 или 6 (.например на входы элементов группы 5 - прямое направление програм.мы). Так как на входы дешифратора 2 поступает информация (j-l)-ro такта (согласно прямому направлению), то включен (j -1)1й выход этого дешифратора. Сигнал с (j-l)-ro выхода дешифратора 2 и сигнал с единичного выхода триггера, поступая на оба входа элемента И j группы 5, включают его. На выходах блока 10 вывода появляется комбинация сигналов j-ой строки матрицы, которая проходит в блок 15 элементов задержки. К этому моменту времени на входы дешифратора 1 поступает с блока задержки комбинация сигналов j-ro такта. На входах дешифратора 2 сохраняется комбинация сигналов (j-l)-ro такта. Эти комбинации сигналов преобразуются на выходах автомата в комбинацию сигналов, соответствующую (+1)-ой строке матрицы. Автомат переходит к основному режиму работы согласно заданной программе. Таким образом, введение дополнительных блоков и связей позволяет отрабатывать заданную программу в прямом и обратном направлениях и проводить в процессе работы обнаружение и исправление некоторых внутренних ошибок. Формула изобретения Логический автомат, содержащий блок памяти, блок элементов задержки, блок вьшода, первая группа выходов которого является выходом устройства, элемент ИЛИ, выходом соединенный через элемент НЕ с первым входом элемента И, тличающийся тем, что, с целью расирения функциональных возможностей за счет тработки заданной программы как в прямом, так в обратном направлении, он содержит первый и торой дешифраторы, первую, вторую, третью и четвертую группы элементов И, группу элементов ИЛИ, шифратор, коммутатор, элемент задержки, блок синхронизации, причем вторая группа выходов блока вьтода соединена со входами блока элементов задержки, первая группа выходов которого соединена со входами первого деш1фратора, а вторая - - с информационными входами блока памяти, выходами соединенного со входам второго дешифратора, выходы первого дешифратора соединены с первыми входами элементов И первой, второй и третьей групп, выходы второго дешифратора соединены с первыми входами элементов И четвертой группы и со вторыми входами элементов И первой и второй групп, первый выход блока синхронизации соединен с управляющим входом блока памяти, второй и третий выходы блока синхронизации соединены с третьими входами элементов И первой и второй групп соответственно, четвертый и пятый выходы блока синхронизации Со7 , . i- . 7881 «динены со вторыми входами ,элеме«тОв и- третьей и четвертой групп соотввтстйенно, выходы элементов И первой, второй, третьей и четвертой групп соединены с первыми входами соответствующих элементов ИЛИ группы, выходы j которых соединены со BXOZUMH шифратора, вторые входы элементов ИЛИ группы соединены с выходами коммутатора, выходы шифратора соединены со входами блока вывода, третья группа выходов которого соединена со fQ входами элемента ИЛИ, шестой выход блока 08 синхронизации через элемент задержки соединен со вторым входом элемента И, выход которого соединен со входом блока синхронизации. Источники информации, принятые во внимание при экспергизе 1.Авторское свидетельство СССР № 276516, ,кл. G 06 F 7/00. 1969. 2.Авторское свидетельство СССР P 433477, кл. G 06 F 7/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство для контроля дефектов фотошаблона | 1989 |

|

SU1698712A1 |

| Устройство для синхронизациипЕРЕдАчи иНфОРМАции | 1979 |

|

SU849192A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Устройство кодирования | 1985 |

|

SU1300639A1 |

Авторы

Даты

1980-12-15—Публикация

1977-12-07—Подача