1

Изобретение относится к области радиоэлектроники и может быть использовано в ЭВМ с повышенными требованиями к дадежности и быстродействию.

Известно оперативное запоминающее устройство (ОЗУ) с самоконтролем 1, содержащее адресный запоминающий блок, подключенный к блокам кодирования и декодирования и основному ассоциативному накопителю, и блок управления. Такое ОЗУ имеет значительный объем, так как избыточные разряды имеют все без исключения ячейки адресного запоминающего блока независимо от того, исправны они или неисправны, какого вида неисправности в них и замещаются ли они ячейками ассоциативного накопителя.

Наиболее близким к изобретению по технической сущности является ОЗУ с самоконтролем 2, содержащее оперативный накопитель, два ассоциативных накопителя, блок кодирования, блок декодирования, блок управления, усилители считывания- записи, регистр слова и соответствующие связи.

Это устройство позволяет исправлять все одиночные ошибки за счет корректирующего кода, а многократные ошибки за счет замены неисправных ячеек.

Недостатком прототипа является низкое

быстродействие, определяющееся быстродействием наиболее медленно работающего блока - оперативного накопителя.

Целью изобретения является повыщение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее первый адресный блок, первый вход которого подключен к адресному входу устройства и к первым

входам первого и второго ассоциативных накопителей, оперативный накопитель, первый вход которого подключен к выходу первого адресного блока, а второй вход и выход - к блоку усилителей записи-считываНИН, первый регистр, выход которого подключен к входу блока усилителей записисчитывания, первый вход - к выходу блока кодирования и к второму входу первого ассоциативного накопителя, второй

вход - к первому выходу второго ассоциативного накопителя, третий вход - к входной шине устройства, блок управления, первый выход которого подключен к третьему входу первого ассоциативного накопителя,

второй выход - к второму входу второго ассоциативного накопителя, третий выход- к первым входам блока кодирования и блока декодирования, второй вход блока декодирования подключен к выходу первого ассоциативного накопителя, третий вход -

к второму входу блока кодирования и к третьему входу второго ассоциативного накопителя, введены второй адресный блок, первый вход которого подключен к четвертому выходу блока управления, второй вход и выход подключены соответственно к второму выходу и к третьему входу второго ассоциативного накопителя, второй регистр, первый вход которого подключен к выходу блока декодирования, второй вход - к второму выходу блока усилителей записисчитывания, третий вход - к входной шине устройства, первый выход - к входу блока управления, второй выход - к выходной шине устройства, а третий выход - к второму входу блока декодирования. Пятый выход блока управления подключен к второму входу первого адресного блока, а шестой выход - к четвертому входу первого регистра. Третий выход второго ассоциативного накопителя подключен к третьему входу первого адресного блока.

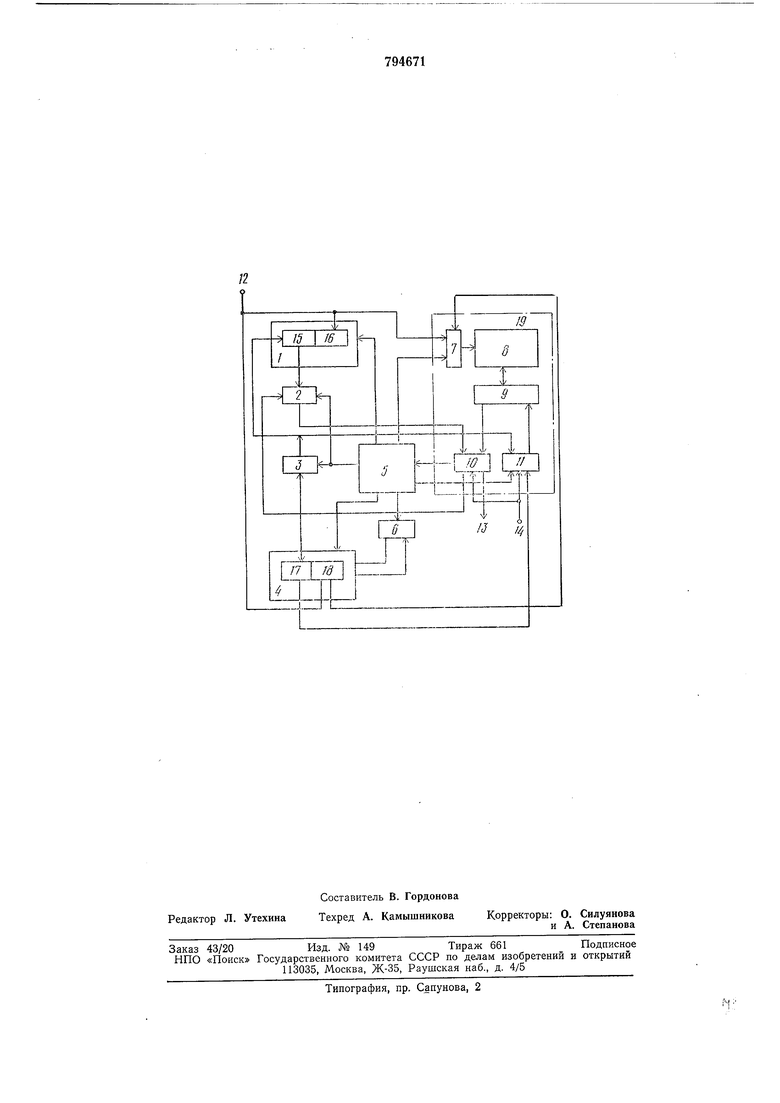

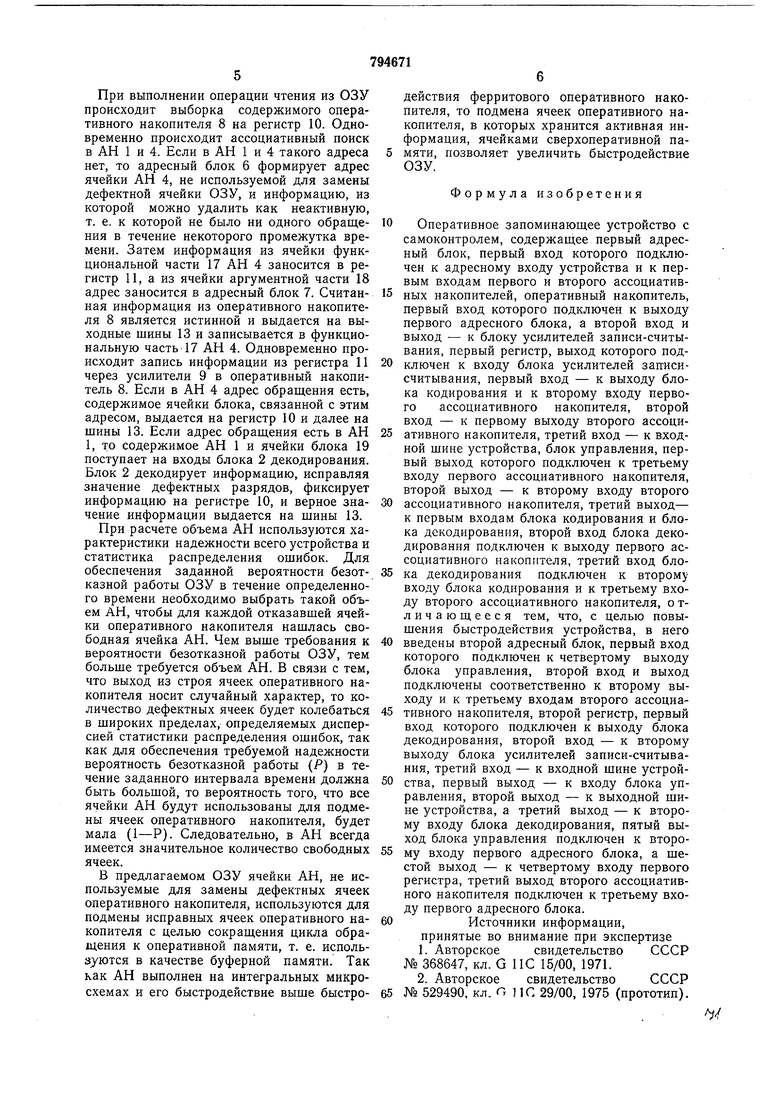

Схема предлагаемого устройства изображена на чертеже, где обозначены первый ассоциативный накопитель (АН) 1, блок декодирования 2, блок кодирования 3, второй АН 4, блок управления 5, второй адресный блок 6, первый адресный блок 7, оперативный накопитель 8, усилитель 9 записи-считывания, второй регистр 10, первый регистр 11, адресный вход 12 устройства, выходная шина 13 устройства, входная шина 14 устройства, функциональная 15 и аргументная 16 части АН 1, функциональная 17 и аргументная 18 части 18 АН и адресный запоминаюш,ий блок 19.

Функциональная часть 15 АН 1 служит для размещения избыточных разрядов при кодировании информации корректирующим кодом, а аргументная часть 16 - для запоминания адресов отказавших ячеек адресного запоминающего блока 19. Этот блок состоит из регистров, схем сравнения логических элементов И, ИЛИ, НЕ.

Адресный запоминающий блок 19 состоит из первого адресного блока 7, оперативного накопителя 8, блока 9 усилителей записи-считывания, первого Ни второго 10 регистров.

Адресный блок 7 предназначен для приема поступающего адреса при записи или считывании информации и состоит из регистров и логических элементов. Блок усилителей записи-считывания 9 используется по прямому назначению. Регистр 11 предназначен для приема информации от внещних устройств, от блока 3 кодирования и от АН 4, а также для выдачи и информации на блок 9 усилителей.

Регистр 10 предназначен для приема информации, поступающей из блока 19 и блока 2 декодирования и выдачи внещним абонентам, а также для выдачи информации в блок 5 управления, АН 4, блок 3 кодирования и блок 2 декодирования.

Блоки кодирования 3 и декодирования 2 используются по их прямому назначению.

Блок 5 управления предназначен для синхронизации работы всех блоков устрой5 ства и для определения исправности ячеек памяти.

Функциональная часть 17 AM 4 служит для размещения полного слова информации ячейки блока 19, а аргументная часть 18 -

10 для запоминания адреса ячейки адресного запоминающего блока 19. В первую очередь ячейки АН 4 используются для подмены дефектных ячеек адресного запоминающего блока 19, а свободные ячейки, неиспользуемые для подмены дефектных ячеек АН 4, используются для подмены исправных ячеек адресного запоминающего блока 19. АН 4 состоит из регистров, схемы сравнения и логических элементов И, ИЛИ, НЕ.

0 Адресный блок 6 предназначен для регистрации информации о наличии свободных ячеек АН 4, а также для выявления ячеек среди ячеек АН 4, подменяющих исправные ячейки оперативного накопителя 8, в кото5 ром хранится неактивная информация, т. е. информация, к которой не было ни одного обращения в течение некоторого промежутка времени. Устройство работает следующим обра0 зом.

В процессе стирания содержимого адресного запоминающего блока 19 или в паузах между внещними обращениями блок 5 управления осуществляет контроль исправности ячеек блока 19. При обнаружении неисправности в какой-либо ячейке блок 4 определяет тип ошибки и в зависимости от характера неисправности (однократной или многократной) адрес неисправной ячейки

0 фиксируется в аргументной части 16 или 18 АН 1 или АН 4.

При внещнем обращении ОЗУ по адресу, установленному на входе 12, происходит одновременное обращение как к запоминаю5 щему блоку 19, так и к АН 1 и 4.

При выполнении операции записи информация с входных шин 14 заносится в регистры 10 и 11. Если при ассоциативном поиске в блоке 4 обнаружен адрес обращения, то информация с регистра 10 записывается в функциональную часть 17 АН 4. Если адрес обращения обнаружен при ассоциативном поиске в АН 1, то информация

5 с регистра 10 поступает в блок 3 кодирования. Закодированная корректирующим кодом информация записывается в блок 19 (через регистр 11, усилители 9 в оперативный накопитель 8) и в функциональную

0 часть 15 АН 1 (избыточные разряды). Если адрес обращения не найден в АН 1 и 4, то с регистра 11 через усилители 9 информация записывается в оперативный накопитель 8 по адресу, зафиксированному в

ресном блоке 7.

При выполнении операции чтения из ОЗУ происходит выборка содержимого оперативного накопителя 8 на регистр 10. Одновременно происходит ассоциативный поиск в АН 1 и 4. Если в АН 1 и 4 такого адреса пет, то адресный блок 6 формирует адрес ячейки АН 4, не используемой для замены дефектной ячейки ОЗУ, и информацию, из которой можно удалить как неактивную, т. е. к которой не было ни одного обращения в течение некоторого промежутка времени. Затем информация из ячейки функциональной части 17 АН 4 заносится в регистр 11, а из ячейки аргументной части 18 адрес заносится в адресный блок 7. Считанная информация из оперативного накопителя 8 является истинной и выдается на выходные шины 13 и записывается в функциональную часть 17 АН 4. Одновременно происходит запись информации из регистра 11 через усилители 9 в оперативный накопитель 8. Если в АН 4 адрес обращения есть, содержимое ячейки блока, связанной с этим адресом, выдается на регистр 10 и далее на шины 13. Если адрес обращения есть в АН 1, то содержимое АН 1 и ячейки блока 19 поступает на входы блока 2 декодирования. Блок 2 декодирует информацию, исправляя значение дефектных разрядов, фиксирует информацию на регистре 10, и верное значение информации выдается на шины 13.

При расчете объема АН используются характеристики надежности всего устройства и статистика распределения ошибок. Для обеспечения заданной вероятности безотказной работы ОЗУ в течение определенного времени необходимо выбрать такой объем АН, чтобы для каждой отказавшей ячейки оперативного накопителя нашлась свободная ячейка АН. Чем выше требования к вероятности безотказной работы ОЗУ, тем больше требуется объей АН. В связи с тем, что выход из строя ячеек оперативного накопителя носит случайный характер, то количество дефектных ячеек будет колебаться в широких пределах, определяемых дисперсией статистики распределения ошибок, так как для обеспечения требуемой надежности вероятность безотказной работы (Р) в течение заданного интервала времени должна быть большой, то вероятность того, что все ячейки АН будут использованы для подмены ячеек оперативного накопителя, будет мала (1-Р). Следовательно, в АН всегда имеется значительное количество свободных ячеек.

В предлагаемом ОЗУ ячейки АН, не используемые для замены дефектных ячеек оперативного накопителя, используются для подмены исправных ячеек оперативного накопителя с целью сокращения цикла обращения к оперативной памяти, т. е. используются в качестве буферной памяти. Так как АН выполнен на интегральных микросхемах и его быстродействие выше быстродействия ферритового оперативного накопителя, то подмена ячеек оперативного накопителя, в которых хранится активная информация, ячейками сверхоперативной памяти, позволяет увеличить быстродействие ОЗУ.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее первый адресный блок, первый вход которого подключен к адресному входу устройства и к первым входам первого и второго ассоциативных накопителей, оперативный накопитель, первый вход которого подключен к выходу первого адресного блока, а второй вход и выход - к блоку усилителей записи-считывания, первый регистр, выход которого подключей к входу блока усилителей записисчитывания, первый вход - к выходу блока кодирования и к второму входу первого ассоциативного накопителя, второй вход - к первому выходу второго ассоциативного накопителя, третий вход - к входной шине устройства, блок управления, первый выход которого подключен к третьему входу первого ассоциативного накопителя, второй выход - к второму входу второго

ассоциативного накопителя, третий выход- к первым входам блока кодирования и блока декодирования, второй вход блока декодирования подключен к выходу первого ассоциативного накопителя, третий вход блока декодирования подключен к второму входу блока кодирования и к третьему входу второго ассоциативного накопителя, о тличающееся тем, что, с целью повышения быстродействия устройства, в него

введены второй адресный блок, первый вход которого подключен к четвертому выходу блока управления, второй вход и выход подключены соответственно к второму выходу и к третьему входам второго ассоциативного накопителя, второй регистр, первый вход которого подключен к выходу блока декодирования, второй вход - к второму выходу блока усилителей записи-считывания, третий вход - к входной шине устройства, первый выход - к входу блока управления, второй выход - к выходной щине устройства, а третий выход - к второму входу блока декодирования, пятый выход блока управления подключен к второму входу первого адресного блока, а шестой выход - к четвертому входу первого регистра, третий выход второго ассоциативного накопителя подключен к третьему входу первого адресного блока.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 368647, кл. G ПС 15/00, 1971.

2.Авторское свидетельство СССР № 529490, кл. О ПС 29/00, 1975 (прототип).

J4J3 IJIJLJ

tl

V Т-1-m г

1 „r--LiTi: :

Ш

/j /

ьП

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Оперативное запоминающее устройство с самоконтролем | 1975 |

|

SU529490A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU947912A2 |

Авторы

Даты

1981-01-07—Публикация

1979-01-04—Подача