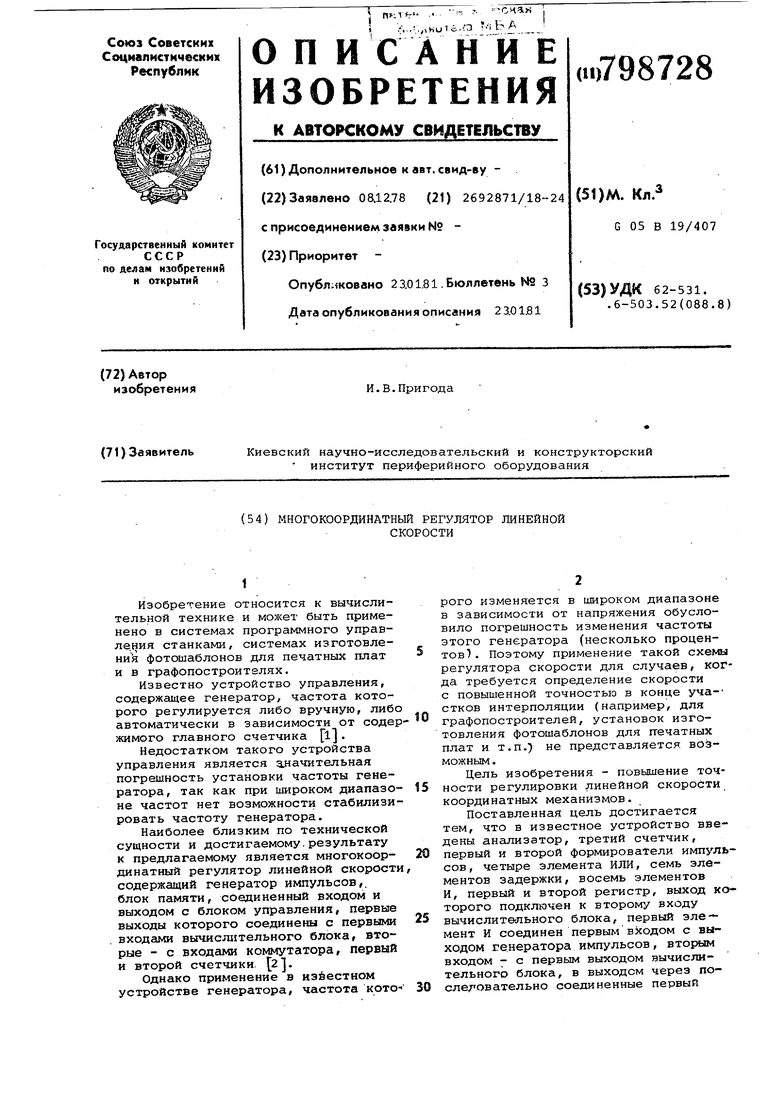

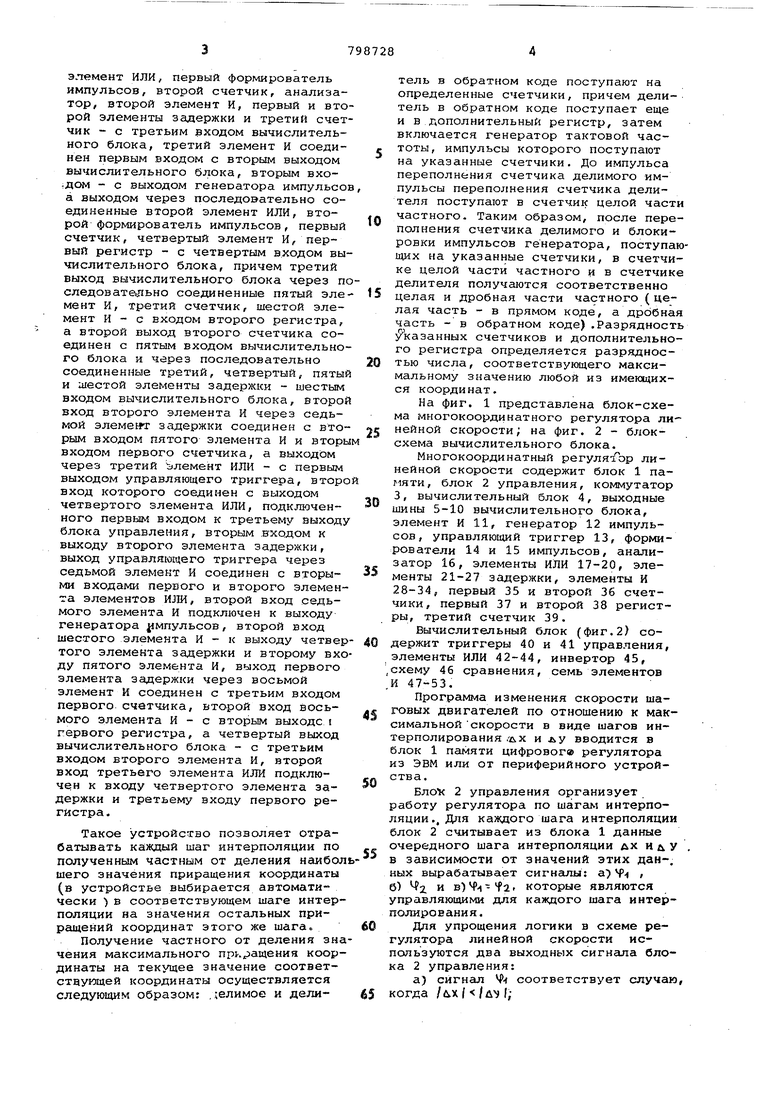

Изобретение относится к вычислительной технике и может быть применено в системах программного управлеция станками, системах изготовления фотсяааблонов для печатных плат и в графопостроителях. Известно устройство управления, содержащее генератор, частота которого регулируется либо вручную, либ автоматически в зависимости от соде жимого главного счетчика р.. Недостатком такого устройства управления является злачительная погрешность установки частоты генератора, так как при широком диапазо не частот нет возможности стабилизи ровать частоту генератора. Наиболее близким по технической сущности и достигаемому.результату к предлагаемому является многокоординатный регулятор линейной скорост содержащий генератор импульсов,, блок памяти, соединенный входом и выходом с блоком управления, первые выходы которого соединены с первыми входами вычислительного блока, вто рые - с входами коммутатора, первый и второй счетчики . Однако применение в иэбестном устройстве генератора, частота кото рого изменяется в широком диапазоне в зависимости от напряжения обусловило погрешность изменения частоты этого генератора (несколько процентов . Поэтому применение такой схемы регулятора скорости для случаев, когда требуется определение скорости с повышенной точностью в конце участков интерполяции (например, для графопостроителей, установок изготовления фотошаблонов для печатных плат и т.п.) не представляется возможным. Цель изобретения - повышение точности регулировки линейной скорости координатных механизмов. Поставленная цель достигается тем, что в известное устройство введены анализатор, третий счетчик, первый и второй формирователи импульсов, четыре элемента ИЛИ, семь элементов задержки, восемь элементов И, первый и второй регистр, выход которого подключен к второму входу вычислительного блока, первый элемент И соединен первым входом с выходом генератора импульсов, вторым входом - с первым выходом вычислительного блока, в выходом через после/овательно соединенные первый элемент ИЛИ, первый формирователь импульсов, второй счетчик, анализатор, второй элемент И, первый и вто рой элементы задержки и третий счет чик - с третьим входом вычислительного блока, третий элемент И соединен первым входом с вторым выходом вычислительного блока, вторым вхо,дом - с выходом генеоатора импульсо а выходом через последовательно соединенные второй элемент ИЛИ, второй формирователь импульсов, первый счетчик, четвертый элемент И, первый регистр - с четвертым входом вы числительного блока, причем третий выход вычислительного блока через п следовательно соединенные пятый эле мент И, третий счетчик, шестой элемент И - с входом второго регистра, а второй выход второго счетчика соединен с пятым входом вычислительно го блока и через последовательно соединенные третий, четвертый, пяты и шестой элементы задержки - шестым входом вычислительного блока, второ вход второго элемента И через седьмой элемент задержки соединен с вто рым входом пятого элемента И и вторы входом первого счетчика, а выходом через третий элемент ИЛИ - с первым выходом управляющего триггера, втор вход которого соединен с выходом четвертого элемента ИЛИ, подключенного первым входом к третьему выходу блока управления, вторым .входом к выходу второго элемента задержки, выход управляющего триггера через седьмой элемент И соединен с вторыми входами первого и второго элемента элементов ИЛИ, второй вход седьмого элемента И подключен к выходу генератора |1Мпульсов, второй вход шестого элемента И - к выходу четвер того элемента задержки и второму вхо ду пятого элемента И, выход первого элемента задержки через восьмой элемент И соединен с третьим входом первого счетчика, второй вход восьмого элемента И - с вторым выходе i первого регистра, а четвертый выход вычислительного блока - с третьим входом второго элемента И, второй вход третьего элемента ИЛИ подключен к входу четвертого элемента задержки и третьему входу первого регистра. Такое устройство позволяет отрабатывать каждый шаг интерполяции по полученным частным от деления наибол шего значения приращения координаты (в устройстве выбирается автоматически ) в соответствующем шаге интерполяции на значения остальных приращений координат этого же шага. Получение частного от деления зна чения максимального пркращения координаты на текущее значение соответствующей координаты осуществляется следующим образом: делимое и делитель в обратном коде поступают на определенные счетчики, причем делитель в обратном коде поступает еще и в дополнительный регистр, затем включается генератор тактовой частоты, импульсы которого поступают на указанные счетчики. До импульса переполнения счетчика делимого импульсы переполнения счетчика делителя поступают в счетчик целой части частного. Таким образом, после переполнения счетчика делимого и блокировки импульсов генератора, поступающих на указанные счетчики, в счетчике целой части частного и в счетчике делителя получаются соответственно целая и дробная части частного ( целая часть - в прямом коде, а дробная часть - в обратном коде).Разрядность ikaзaнныx счетчиков и дополнительного регистра определяется разрядностью числа, соответствующего максимальному значению любой из имеющихся координат. На фиг. 1 представлена блок-схема многокоординатного регулятора ли нейной скорости; на фиг. 2 - блоксхема вычислительного блока. Многокоординатный регуля Ър линейной скорости содержит блок 1 памяти, блок 2 управления, коммутатор 3, вычислительный блок 4, выходные шины 5-10 вычислительного блока, элемент И 11, генератор 12 импульсов, управляющий триггер 13, формирователи 14 и 15 импульсов, анализатор 16, элементы ИЛИ 17-20, элементы 21-27 задержки, элементы И 28-34, первый 35 и второй 36 счетчики, первый 37 и второй 38 регистры, третий счетчик 39. Вычислительный блок (фиг.2) содержит триггеры 40 и 41 управления, элементы ИЛИ 42-44, инвертор 45, схему 46 сравнения, семь элементов И 47-53. Программа изменения скорости шаговых двигателей по отношению к максимальной скорости в виде шагов интерполирования ,дьх и лу вводится в блок 1 памяти цифрового регулятора из ЭВМ или от периферийного устройства. Блок 2 управления организует работу регулятора по шагс1м интерполяции.. Для каждого шага интерполяции блок 2 считывает из блока 1 данные очередного шага интерполяции лх и л у , в зависимости от значений этих дан-. ных вырабатывает сигнашы: а) Чч / б) 2. и в) - f 2. которые являются управляющими для каждого шага интерполирования. Для упрощения логики в схеме регулятора линейной скорости используются два выходных сигнала блока 2 управления: а) сигнал 4 соответствует случаю, когда /бх( /uV f; б) сигнал f2 соответствует случа когда . Одновременное наличие признаков Ч и Yi соответствует /uX/-/&vf. Регулятор скорости производит де ление частоты шагов двигателя, осуществляклцего отработку наибольшего приращения координаты для каждого ш га интерполирования, на величину R г f ,если/U., или на величину R jfjl , если/л.. Для случа когда/дх/ /д- /, отработка шагов интерполирования для обеих координат происходит на максимальной скорости, которую обеспечивают шаговые двигате ли. Вначгше каждого шага интерполирования регулятор запускается сигналом И,.ц , вырабатываемь блоком 2. Затем этот блок получает из блока 1 памяти значения дх и йу для первого шага интерполирования, определяет признаки и 2 f поступающие в коммутатор 3 и в вычислительный блок 4 В зависимости от значения этих признаков блок 3 осуществляет передачу значений и & у по шинам .на сиетчи ки 35 и 36, регистр 37. Передача осуществляется обратными кодами следующим образом: при наличии признака f( и л.м передается на счетчик 35 и регистр 37, дх - на счетчик 36; при наличии признака Va указанные передачи происходят наоборот. После окончания этой передачи блок 2 вырабатывает импульс И.5с1пВ процессе деления приращерий дх и ду (ИЛИ наоборот) имиульсы переполнения счетчика 35 поступают через задержку 21-на время длительности этого импульса, элемент И 29 и элемент ИЛИ 20 на установку управ ляющего триггера 13 в О. Элемент И 9 блокирует прохождение этих импульсов в случае равенства нулю содержимого счетчика 36, определяемого анализатором 16, а при отработке приращений исполнительными механизмами. Этот же импульс после элемента И 29 поступает на задержку 22 на время переключения триггера 13, а после нее - на элемент И 30 передающий содержимое регистра 37 на счетчик 35. После окончания этой передачи импульс целой части частного Ицч появляется на выходе задерж ки 23, который поступает на вход счетчика 39 целой части частного в качестве счетного импульса и на эле мент ИЛИ 17 для установки триггера 13 в 1. После этого процесс деления продолжается описанным выла способом. Импульс переполнения счетчика 36 через зёщержку 24 на время длительности этого myльca поступает на установку в О регистра 37 и триггера 13 через элемент ИЛИ 20. Этим заканчивается процесс деления прира щений. Частное от деления фиксируется в счетчиках 35 и 39. По окончании деления осуществляется подготовка системы для выдачи соответствующих приращений лх и д у на отработку исполнительными механизмами. Для этого импульс после задержки 24 задерживается .линией задержки 25на время переключения триггера 13 и двух инверторных схем, затем через элементы И 11 и 31 передает частное от деления приращений со счетчиков 35 и 39 на регистры 37 и 38, этот же импульс через задержку 26на время указанной передачи кодов устанавливает счетчики 35 и 39 в О, затем через задержку 27 (АЗ (2)) поступает в вычислительный блок (фиг.2), где устанавливает через элемент ИЛИ 42 в 1 триггеры 40и 41, На этом заканчивается подго тонка регулятора линейной скорости для вьщачи приращений д,х иду. Последующая их выдача осуществляется вычислительным блоком 4. Блок 4 осуществляет вьодачу приращений дх и ду для .отработки их исполнительными механизмами. Выдача происходит последовательными колодами. Знаки соответствующих приращений выдаются на блок 2 управления исполнительными механизмами из блока 1. Триггер 40 управляет выдачей приращения Дх, триггер 41 - приращения ду. Если дх й.у(Ч -Чг-) , то используется для выдачи приращений триггер 40. Единичные выходы триггеров 40 и 41открывают элементы И 32 и 33, разрешая этим прохождение импульсов генератора 12 через элементы И 18 и 19, формирователи импульсов 14 и 15 на входы счетчиков 35 и 36. Нулевые выходы указанных триггеров поступают на элемент И 47, выход которого блокирует элемент И 29 на время отработки приращений координат, т.е-, импульсы переполнения счетчика 35 не поступают на вход счетчика ..39 при отработке приращений координат. Выход И 47 поступает также через инвентор 45 на элемент И 34, который разрешает прохождение импульсов переноса со счетчика 35 на счетчик 39 при отработке приращений дх и ь. у исполнительными механизмами. I Количество разрядов счетчиков 35, 36 и 39 и регистров 37 и 38 выбирается, исходя из максимальной частоты отработки приращений дх и ду. Если принять л-х ах УМСЯХ 4000, отах кГц, то количество разрядов указанных счетчиков и регистров будет равно 12. Частота тактового генератора при этом должнс быть 8,192 МГц. В процессе отработки приращений А,х и дубольшее по абсолютной величине приращение отрабатывается импульсами переполнения счетчика 36, а меньшее - импульсами сравнения (Hf-p), поступающих со схемы сравне-ния 46, где сравнивается частное от деления приращений, находящееся в регистрах 37 и 38, с содержимыми счетчиков 35 и 39,

проходят через элемент И 48, если () (ду), затем через элемент ИЛИ 43 - на выход регулятора линейно скорости. Иср проходят через элемент И 49, если , затем через ИЛИ 44 - на выход регулятора. Шлход с элемента ИЛИ 43 используется исполнительными механизмами блока управлен я для отработки приращения лх, а выход с элемента ИЛИ 44 - для. отработки приращения й.у.

Частота, соответствующая большему по абсолютной величине приращению, поступаккцая со счетчика 36 проходит через элементы И 50 и 51 на элементы ИЛИ 43 и 44, затем - на выход систем

Если лх ду ) импульс запуска регулятора поступает в вьачислительный блок 4, проходит элемент И 52, элемент ИЛИ 42 и устанавливает в 1 триггеге 40 и 41, Триггер 40 даёт разрешение на прохождение импульсов переполнения счетчика 36 через элемент И 53 на элементы ИЛИ 43 и 44,

После отработки приращений координат для каждого шага интерполяции блока 2 соответствующим импульсом для каждой координаты возвращает триггеры 40 и 41 в нулевое состояние

При количестве координат, большем двух, увеличивается количество признаков Ч . Например, при трех координатах количество этих признаков будет равно

А - 3 6,

Многокоординатный регулятор линейной скорости с тремя координатами строится по описанному выше принципу для двух координат с небольшим изменением схемы,

Максимсьпьная погрешность для данного способа построения регулятора линейной скорости определяется соотношением rf 2, где п - число двоичных разрядов каждого счетчика. Например, если } 12, максимальное значение координаты равно 4000, то погрешность отработки шагов интерполяции в предлагаемом устройстве составляет около 0,025%, что на два порядка ниже погрешности известных устройств .

Формула изобретения

Многокоординатный регулятор лине(ной скорости, содержащий генератор импульсов, упр. вляющий триггер

блок памяти, соединенный входом и . выходом с блоком управления, первые выходы которого соединены с первыми входами вычислительного блока, вторые - с входами коммутатора, подключенного первым выходом к первому входу первого счетчика, вторьм - к 1первому ьходу второго счетчика, отличающийся тем, что, с цел повышения точности регулятора, в него введены анализатор, третий счетчик, первый и второй формирователи импульсов, четыре элемента ИЛИ, сем элементов задержки, восемь элементо И, первый и второй регистр, выход которого подключен к второму входу вычислительного блока, первый элемент И соединен первым входом с выходом генератора импульсов, вторым - с первым выходом вычислительного блока, а выходом через последовательно соединенные первый элемент ИЛИ, п-ервый формирователь импульсов, второй счетчик, анализатор, второй элемент И, первый и второй элементы задержки и третий счетчик - с третьим входом вычислительного блока, третий элемент И соединен первым входом с выходом вычислительного блока, вторым входом - с выходом генератора импульсов, а выходом через последовательно соединенные второй элемент ИЛИ, второй формирователь импульсов первый счетчик, четвертый элемент И, первый регистр - с четвертым входом вычислительного блока, причем третий выход вычислительного блока через последовательно соединенные пятый элемент И, третий счетчик и шестой элемент И - с входом второго регистра, а второй выход второго счетчика соединен с пятым входом вычислительного блока и через последовательно соединенные третий, четвертый, пятый и шестой элементы задержки - с шестым входом вычислительного блока, второй вход второго элемента И через седьмой элемент задержки соединен с вторым входом пятого элемента И и втррым входом первого счетчика, а выходом через третий элемент ИЛИ - с первым выходом управляющего триггера, второй вход которого соединен с выходом четвертого элемента ИЛИ, подключенного первым входом к третьему выходу блока управления, вторым входом к ВЕлходу второго элемента задержки, выход управляющего триггера через седьмой элемент И соединен с вторыми входами первого и второго элементов ИЛИ, второй вход седьмого элемента И подключен к выходу генератора импульсов, второй вход шестого элемента И - к выходу четвертого эле 1ента задержки и второму входу пятого элемента И, выход первого элемента задержки через восьмой элемент И соединен с третьим входом первого счетчика, второй вход восьмого элемента И - с вторым выходом первого регистра, а четвертый выход вычислительного блока - с третьим входом второго элемента И, второй вход третьего элемента ИЛИ подключен к входу четвертого элемента задержки и третьему входу первого регистра

5678910

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ 2400028, , G 05 D 3/08, 1976.

кл

2. Авторское свидетельство СССР №209566, кл. G 05 В 19/18, 1966 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1978 |

|

SU807236A1 |

| Линейный интерполятор | 1988 |

|

SU1522157A1 |

| Многоканальный интерполятор для программного управления многокоординатным станком | 1978 |

|

SU746429A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Многокоординатный линейно-круговой интерполятор | 1984 |

|

SU1156008A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Линейно-круговой интерполятор | 1982 |

|

SU1149218A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1989 |

|

SU1695267A1 |

Авторы

Даты

1981-01-23—Публикация

1978-12-08—Подача