%7

U

/ bvMJ

/ f ФФ

-&

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1989 |

|

SU1725216A1 |

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| ОПЕРАЦИОННЫЙ БЛОК | 1993 |

|

RU2034330C1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Изобретение относится к области вычислительной техники и может быть исполь- зовано при построении процессоров, выполняющих операции двоичной и десятичной арифметики. Целью изобретения является повышение быстродействия. Устройство содержит группу двоичных операционных блоков 1-4, регистр 5 и мультиплексор 6. 2 ил.

CL

л

г

сз

/ v

л

Выход

М

ВходЗ$о

4 Ю Х4

О 00

Фцг.1

Изобретение относится к области вычислительной техники и может использоваться в ЭВМ с двоичной и десятичной арифметикой.

Известны арифметические устройства (АУ) на основе 4-разрядных двоичных операционных блоков с микропрограммным управлением, выполненных в виде микропроцессорных секций (МПС). Таков, например, процессор ЭВМ СМ-1420. В него входят арифметический модуль на базе 4-х МПС типа Е18.4ВС2 и микропрограммное устройство управления. Недостатком этого и подобных устройств является низкая производительность при выполнении десятичных операций из-за отсутствия в МПС средств десятичной коррекции.

Известны также устройства на базе 4- разрядных блоков, имеющих десятичные операции, таких как микросхемы К1800ВС1. Их использование не всегда возможно или желательно, так как блоки без десятичных операций могут иметь лучшие характеристики - наличие внутренней памяти, надежность, температурный диапазон и т.п.

Наиболее близким к предлагаемому техническому решению является арифметическое устройство (операционный блок), описанный в кн. под ред.В.Г.Колесникова Проектирование УЧ на комплектах микро- программируемых БИС, рис. 2.7, Устройство содержит 4 двоичных 4-разрядных МПС, соединенных по цепям сдвига и переноса, схему ускоренного переноса, схему управления состоянием и сдвигами, регистры входных и выходных данных. Недостатком устройства - низкое быстродействие при выполнении десятичных операций, так как отсутствие цепей десятичной коррекции приводит к длинным микропрограммам по- тетрадной обработки десятичных данных. Так для реализации десятичного сложения требуется как минимум 2 + К микрокоманд, где К - число тетрад десятичного кода.

Целью изобретения является повышение быстродействия при выполнении десятичных операций на двоичных операционных блоках.

Арифметическое устройство с микропрограммным управлением содержит группу двоичных операционных блоков, которые могут быть реализованы, например, на микросхемах типа К1804ВС2, в количестве п/4, где п - разрядность информации. Первые и вторые информационные входы и выходы блоков являются соответственно первым и вторым информационными входами и выходом устройства. Вход задания вида операции устройства соединен со входами задания вида операции двоичных операционных блоков группы. Выход переноса k- ого блока -соединен со входом переноса k+T-ro блока, где k 1 - п/4-1.

С целью повышения быстродействия в

устройство, в отличие от прототипа введены регистр и мультиплексор. Адресный вход и вход задания десятичных операций устройства соединены соответственно с первым информационным и управляющим входами

мультиплексора. Выходы переносов двоичных операционных блоков группы соединены со входами разрядов регистра, выходы разрядов которого соединены с соответствующими разрядами второго информацион5 ного входа мультиплексора, выходы разрядов которого соединены сог входами задания направления приема соответствующих операционных блоков. Совокупность перечисленных отличительных признаков

0 обеспечивает возможность выбора источника кода десятичной коррекции для каждой тетрады в отдельности, что позволяет выполнять операцию не более чем за три микрокоманды, независимо от разрядности.

5 при этом быстродействие по сравнению с прототипом при выполнении, например десятичного сложения, повышается вдвое при сложении 4-разрядных чисел, в три раза при сложении 7-разрядных и т.д.

0 Изобретение иллюстрируется на примере устройства для обработки 16-разрядных двоичных или -4разрядных десятичных чисел, схема которого представлена на фиг. 1 .АУ содержит группу из двоичных операци5 онных 4-разрядных блоков 1-4, В устройство также входят регистр запоминания переносов РЗП 5 и двувходовой мультиплексор М 6, разрядность которого равна числу блоков.

0 Первые и вторые информационные входы блоков 1-4 и их выходы являются соответственно первым и вторым информационными входами устройства И ВХЧ, ИВХ2 и выходом устройства. Блоки

5 могут выполнять двоичные операции над данными, поступающими с входов ИВХ1, ИВХ2 или записанными в их внутренней памяти. Выходы переносов С2, СЗ, С4 блоков 2, 3, 4 соединены соответственно со

0 входами переносов блоков 1, 2, 3. Вход задания вида операции ВхЗВО соединен со входами задания операции двоичных операционных блоков группы. Адресный входАВх и вход задания десятичной операции

5 ВхЗДО соединены соответственно с первым информационным (вход А) и управляющим входами мультиплексора б. Выходы переносов С1, С2, СЗ, С4 операционных блоков соединены с входами разрядов РЗП 5. Выходы разрядов РЗП соединены с соответствующими разрядами второго информационного входа (вход В) мультиплексора 6. Выходы разрядов мультиплексора Ml, М2, МЗ, М4 соединены со входами задания направления приема (выбора источника операнда) соответствующих двоичных операционных блоков группы.

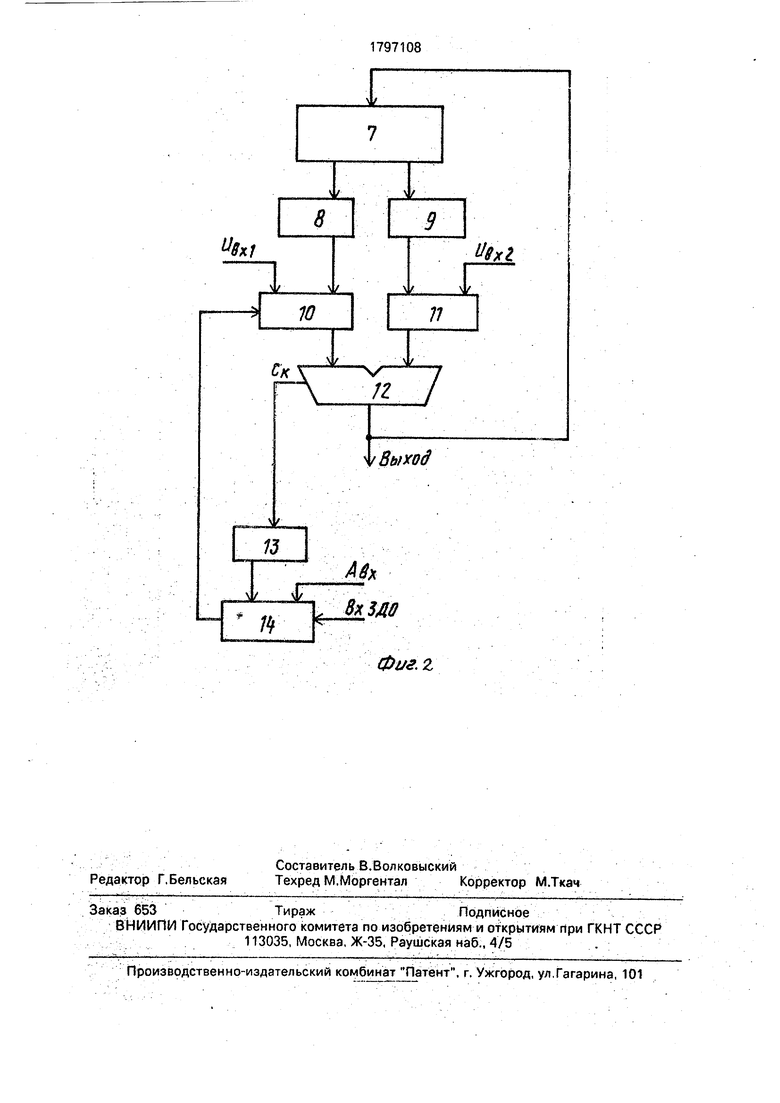

На фиг. 2 показан пример схемы одного операционного блока с триггером запоминания переноса, входящего в состав РЗП, и одним разрядом мультиплексора. В блок входят регистровое запоминающее устройство (РЭУ) 7, выходы которого соединены со входами регистров РгА, РгВ 8, 9, мультиплексоры операндов (М1, М2) 10.11, выхо- ды которых соединены со входами арифметико-логического устройства (АЛУ) 12, выход которого соединен с входом РЗУ и выходом блока. Информационные входы мультиплексора 10 соединены соответст- венно с выходами РгА и первым информационным входом, информационные входы мультиплексора 11 соединены соответственно с выходами РгВ и вторым информационным входом. Выход переноса Ск АЛУ 12 соединены с входом триггера Т 13, выход которого соединен со вторым информационным входом разряда мультиплексора Мк 14, выход которого подключен к управляющему входу мультиплексора 10, а первый информационный и управляющий входы соединены соответственно с адресным входом АВх и входом задания десятичной операции ВхЗДО.

Работу устройства рассмотрим на при- мере сложения двух десятичных чисел, записанных в регистрах РЗУ, которые обозначим Р1 и Р2. При этом будем считать, что при Мк 1 через мультиплексор М1 к АЛУ подключается выход РгА, а при М 0

Формула изобретения Арифметическое устройство с микропрограммным управлением, содержащее группу двоичных операционных блоков, причем первые и вторые информационные входы, выходы двоичных операционных блоков группы являются соответственно первым и вторым информационными входами и выходом устройства, вход задания вида операции которого соединен с входами задания вида операции двоичных операционных блоков

группы, выход переноса К-ого (К - -%-1, пколичество разрядов информации) двоичного операционного блока группы соединен с входом переноса (К+1)-го двоичного операцион- первый информационный вход, который может быть связан, например, с полем константы микрокоманды.

По первой микрокоманде задается сложение Р1 с кодом 6666. поступающим с первого информационного входа. При этом сигналы АВх 1, ВхЗДО 0. Сигналы Ml М2 МЗ М4 1 обеспечивают выбор кода 6666 в качестве первого операнда.

Вторая микрокоманда задает прибавление к Р1 второго слагаемого из Р2. Возникающие межблочные переносы С1, С2, СЗ, С4 фиксируются в РЗП 5.

По третьей микрокоманде из Р1 вычитается код коррекции, При этом сигнал ВхЗДО 1. Поэтому выбор источника первого операнда осуществляется для каждого блока в отдельности в зависимости от состояния РЗП из поля константы 6666 МК через ИВх1 или из адресуемого регистра РЗУ, в котором записан код 0000. Так при состоянии РЗП 0011 код коррекции для двух старших тетрад выбирается с ИВх1, а для двух младших

- из регистра РЗУ, то есть примет значение 6600.

Ниже приводится пример сложения десятичных чисел 3458 и 4089. Микрокоманда 1:0011 0100 0101 1000 +

0110 0110 0110 0110

Микрокоманда 2: +

1001 1010 1011 1110

Микрокоманда 3: 0100 0000 10000111 1101 1011 0100 0111 (Код переноса 0011)

0110 0110 0000 0000

0111 0101 0100 0111 7547.

ного блока группы, отличающееся тем, что, с целью повышения быстродействия, оно содержит регистр и мультиплексор, причем адресный вход и вход задания десятичных операций устройства соединены соответственно с первым информационным входом и с управляющим входом мультиплексора, выходы переносов двоичных операционных блоков группы соединены с входами разрядов регистра, выходы разрядов которого соединены с соответствующими разрядами второго информационного входа мультиплексора, выходы разрядов которого соединены с входами задания направления приема соответствующих двоичных операционных блоков группы.

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство с микропрограммным управлением | 1989 |

|

SU1725216A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1993-02-23—Публикация

1990-03-16—Подача