f

Изобретение относится к цифровой вычислительной технике и может применяться в цифровых вычислительных MeUiiHHcix для вычисленля элементарных функций.

Известны арифметические устройства, предназначенные для решения задач, содержащих элементарные функции I содержащие регистры, блоки сдвига, сумматоры 1 и 2.

Недостаток-устройств - низкое быстродействие при вычислении функций 1 fa , 5 Re-inavctaVx .и 4 RcosaiV4itc /x, где x, ,КиЧ аргументы; f, f, f, 4 - значения функций.

; Наиболее близким по технической сущности к предлагаемому является арифметическое устройство, содержащее первый , второй и третий регистр блок сдвига, сумматор, причем выход первого регистра подключен к первому входу второго регистра, выход которого подключен ко входу блока сдвига, первый, второй и третий входы сумматора подключены, соответственно, к выходам второго регистра, блока сдвига и третьего регистра, выходы сумматора подключены к первым входам первого и третьего регистров,

соответственно, вторые входы первого, второго и третьего регистров и управляющий вход сумматора соединены первым, вторым, третьим и четвертым входами устройства, соответственно, а выходы первого, второго и третьего регистров соединены, соответственно, с первым, вторым и третьим выходами устройства 2.

0

Одним из этапов вычисления является умножение аргумента R на постоянный коэффициент .

Т 1/k i/ ;Vbi:2 r:j(), (1) ТДе i 0,1-n-l, где n - разрядность,

,1} - цифры коэффициента Т f

5 представленного произведением вида (1), путем реализации выражений

.

0

U1

V s

+ 1- it-f )

25 где i OTl-n-l, с начальными уелоВИЯМИ 4(1 R , :)оИ XQ - произвольные числа, и конечными результатги«1

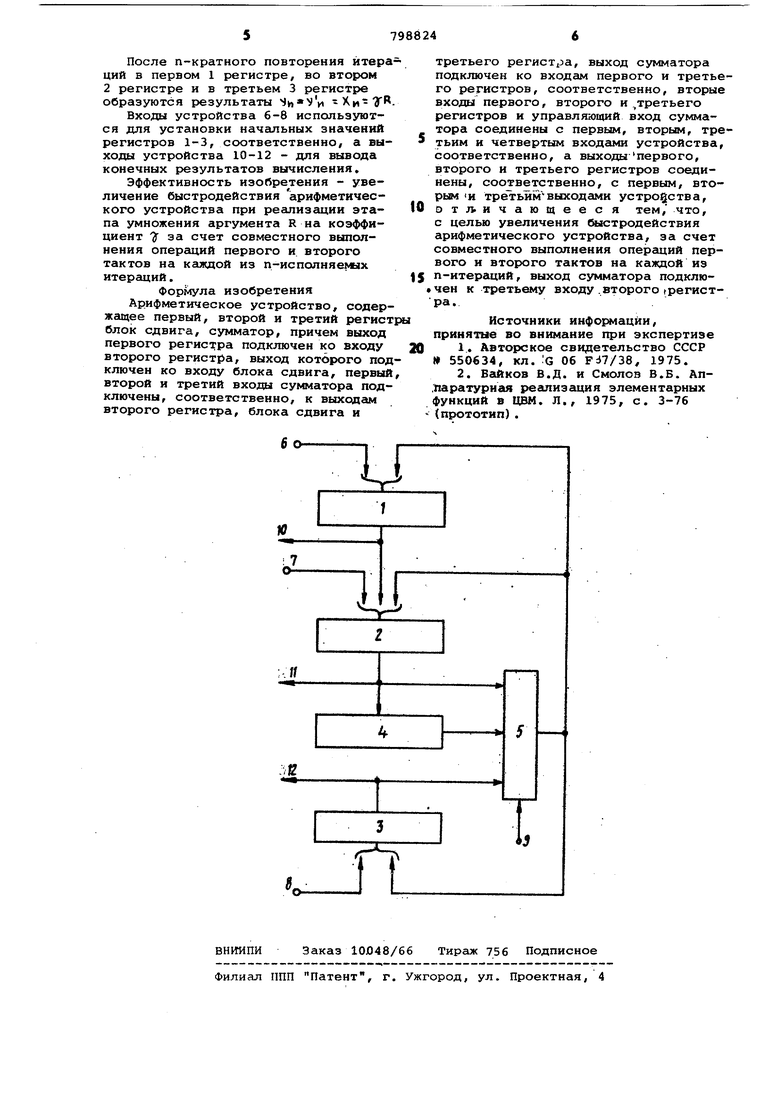

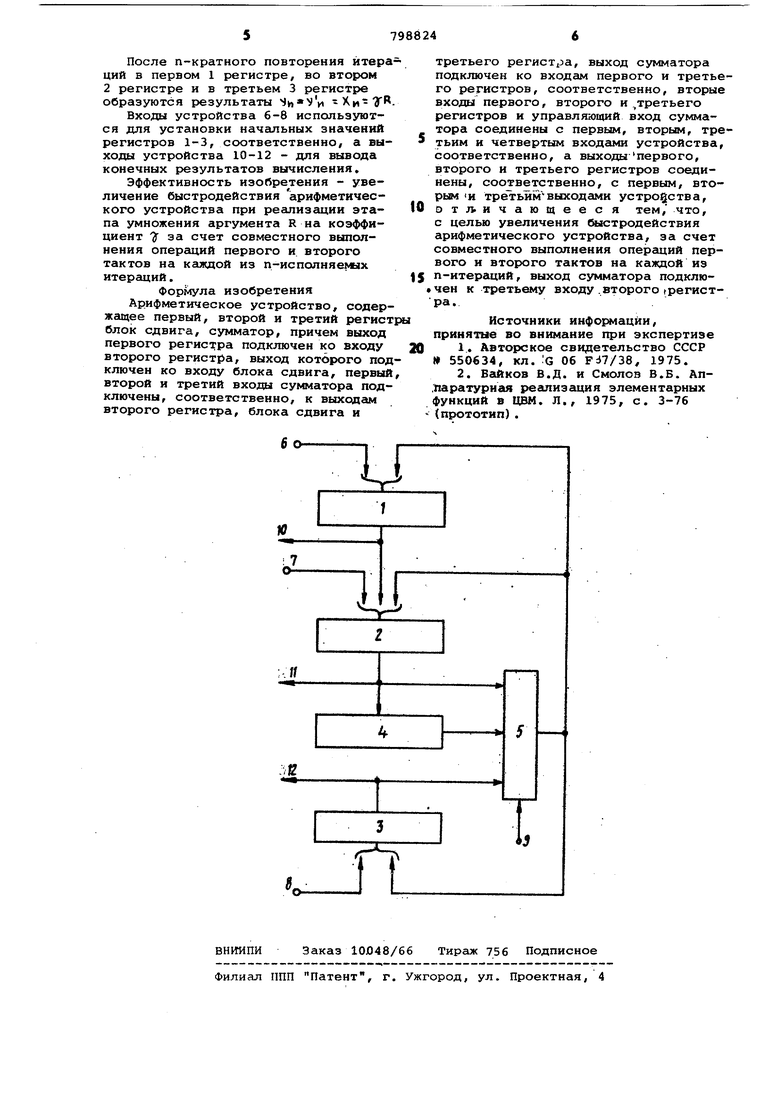

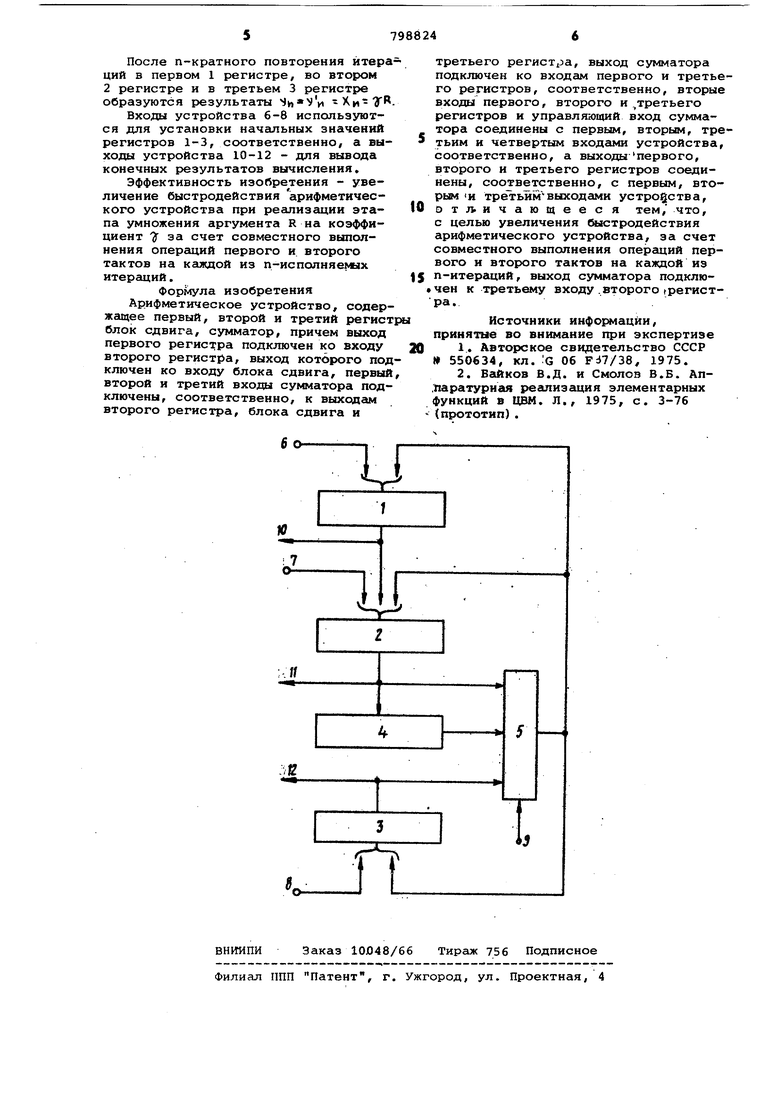

и и- h Первый регистр предназначен для 30 хранения величины ., , первоначально . равной произвольному числу, второй регистр предназначен для хранения величины -J , первоначсшьно равной R третий регистр предназначен для хра нения величины х, первоначально равной произвольному числу. Устройство работает на данном эт пе вычисления функций циклически (к дая итерация состоит из двух тактов Устройство работает следующим об разом на i-ой итерации. В первом такте величины постулает из второго регистра на первые входы cyiviMaTopa и на вход блока сдви га, где сдвигается на i-разрядов вправо, т.е. на выходах сдвига образуется величина , которая поступает на вторые входы сумматора. В зависимости от значения величины , поступившей на управляющий вход сумматора, в сумматоре происходит операция сложения (вычитания) прступивших в него величин Ч к j -1- , т.е. на выходах сумматора образуется величина , В конце первого такта величина передается из сумматора в первый ре гистр и одновременно - в третий регистр. Во втором такте величина . пе дается из первого регистра во второй регистр, т.е. .( - м . . После пкратного повторения итераций в первом, втором и третьем регистрах образуются результаты , -).v -2Гft Heдocтaтoк устройства - низкое быстродействие, обусловленное после довательным выполнением первого и второго тактов при умножении аргумента R на постоянный коэффициент. Цель изобретения - увеличение быстродействия арифметического устройства. Поставленная цель достигается те что в арифметическом .устройстве, содержсцдем первый, второй и третий регистры, блок сдвига, сумматор, пр чем выход первого регистра подключе к входу второго регистра, выход которого подключен ко входу блока сдв га, первый, второй и третий входы сумматора подключены, соответственн невыходам второпо регистра, блока сдвига и третьего регистра. Выход с мматора подключен ко входам перво qp .и третьего регистров, соответственно, вторые входы первого, второг и третьего регистров и управляющий вход сумматора соединены с первым, вторым, третьим и четвертым входами устройства, соответственно, а выход первого, второго и третьего регистров соединены, соответственно, с первым, вторым и третьим выходами устройства, дополнительно выход сум матора подключен к .третьему входу второго регистра. На чертеже показана блок-схема арифметического устройства. Арифметическое устройство содержит первый 1,второй 2 и третий 3 регистры, соответственно,блок 4 сдвига,сумматор 5, первый 6, второй 7, третий 8 и четвертый 9 входы устройства, соответственно, выходы устройства 10-12, J Предлагаемое устройство вычисляет значения элементраных функций f Rs-fn f2 RC094, flk.R9iy,. V/X, 4 Rcosa x:tt V /x, где x, -j, R и If- аргументы; f,f,,f и 4 - значения функций по сшгоритму цифра за цифрой . Одним из зтапов вычисления указанных функций является умножение аргумента R на постоянный коэффициент у--1/кн/гп-Л72 --Пи- 2-),: (3) где ,l-n-l, где п - разрядность; . цифры коэффициента у , представленного произведением вида (3), путем реализации выражений i-t-i i4-t 41 где ,l-n-l , с начальными условиями -jQiR, VQ Хо произвольные числа и конечными результатами ; h- ;i 4--TR. Первый 1 регистр предназначен для хранения величины I,- , первоначально равной произвольному числу, второй 2 регистр предназначен для хранения величины , первоначально равной R, третий 3 репютр предназначен для хранения величины х, первоначально равной произвольнсаду числу. Устройство работает на данном этапе вычисления фун.кций циклически (каикдая итерация состоит из одного такта). Устройство работает следующим образом на 1-ой итерации. Величина Ч: поступает из второго 2 регистра на первые входы сумматора 5 и на входы блока 4 сдвига, где сдвигается на 1-раэрядов вправо, Т.е. на выходах блока 4 сдвига образуется величина а, которая поступает на вторые входы сумматора 5. В зависимости от значения величины , поступившей на управляющий вход 9 сумматора 5, в сумматоре 5 происходит операция сложения (вычитания) поступивших в него величин Ч иЧ , т.е. на выходах суммато-: ра 5 образуется величин .,-2. В конце 1-ой итерации величина J 4 передается из сумматора 5 одновременно в первый 1 регистр, во второй 2 регистр и в третий регистр 3. После n-кратного повторения итера ций в первом 1 регистре, во втором 2 регистре и в третьем 3 регистре образуются результаты -Хи-Т Входы устройства 6-8 используются для установки начальных значений регистров 1-3, соответственно, а выходы устройства 10-12 - для вывода конечных результатов вычисления. Эффективность изойретения - увеличение быстродействия арифметического устройства при реализации этапа умножения аргумента R на коэффициент Tf за счет совместного выполнения операций первого и второго тактов на каждой из п-исполняемых итераций. Формула изобретения Арифметическое устройство, содер жащее первый, второй и третий регисТ блок сдвига, сумматор, причем выход первого регистра подключен ко входу второго регистра, выход которого под ключен ко входу блока сдвига, первый второй и третий входы сумматора подключены, соответственно, к выходам второго регистра, блока сдвига и

боитретьего регистра, выход сумматора подключен ко входам первого и третьего регистров, соответственно, вторые входы первого, второго и ,третьего регистров и управляющий вход сумматора соединены с первым, вторым, тре тьим и четвертым входами устройства, соответственно, а выходы первого, второго и третьего регистров соединены, соответственно, с первым, вторым И тре1гьйм выходами устройства, отл-ичающееся тем, что, с целью увеличения сйлстродействия арифметического устройства, за счет совместного выполнения опергщий первого и второго тактов на каждой из п-итераций, выход сумматора подключен к третьему входу.второго регистра. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 550634, кл. G Об Fi7/38, 1975. 2.Вайков В.Д. и Смолов В.Б. Апяаратуриая реализгщия элементарных функций в 1даМ. Л., 1975, с. 3-76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления корня пятой степени | 1976 |

|

SU691848A1 |

| Арифметическое устройство | 1979 |

|

SU798821A1 |

| Арифметическое устройство | 1979 |

|

SU798823A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Устройство для вычисления тригонометрических функций | 1979 |

|

SU877527A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1278886A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Авторы

Даты

1981-01-23—Публикация

1979-03-19—Подача