у,.-- I;

Изобретение относится к области цифровой вычислительной техники и может найти применение для аппаратной реализации операции вычисления. корня пятой степени в управляющих и вычислительных системах.Известно устройство для извлечения корня п-й степени, содержащее п сдвигающий регистров, п полноразрядных сумматоров, регистр аргумента, регистр начального коэффициента, регистр результата, коммутаторы результата и младшего коэффициента, блок управления, выходы которого связаны с регистрами и сумматорами, последние связаны друг с другом . двухсторонней связью 1.

Известное устройство не позволяет одновремешю вычислять корень пятой степени из аргумента, его квадрата, куба и четвертой степени.

Известно также устройство для Вьгаисления корня четвертой степени, содержащее девять регистров сдвига, четырнадцать одноразрядных суммаюров-вычитателей, блок памяти, блоки анализа сходимости и знака, блок управления, пфвые входы и первые выходы регистров

сдвига соединены с выходами и первыми входами соответствуйщих сумматоров-вычитателей, второй выход пятого регистра сдвига соединен со входом .блока сравнения, один выход которого подключен ко вторым входам сумматоров-вычлтателей, а другой - к входу блока управления, выходы которого соединены со сдвигающими входами регистров сдвига и вхо. дом блока формирования констант, первый выход которого соединен с третьим входом первого сумматора-вычитателя 2.

Однако известное устройство не предназначено Для вычисления корня пягой степени.

Целью изобретения является расишрение класса рещаемых задач за счет возможности вычисления корня пятой степени из аргумента и одновреме1шо из квадрата, куба и четвертой степени аргумента.

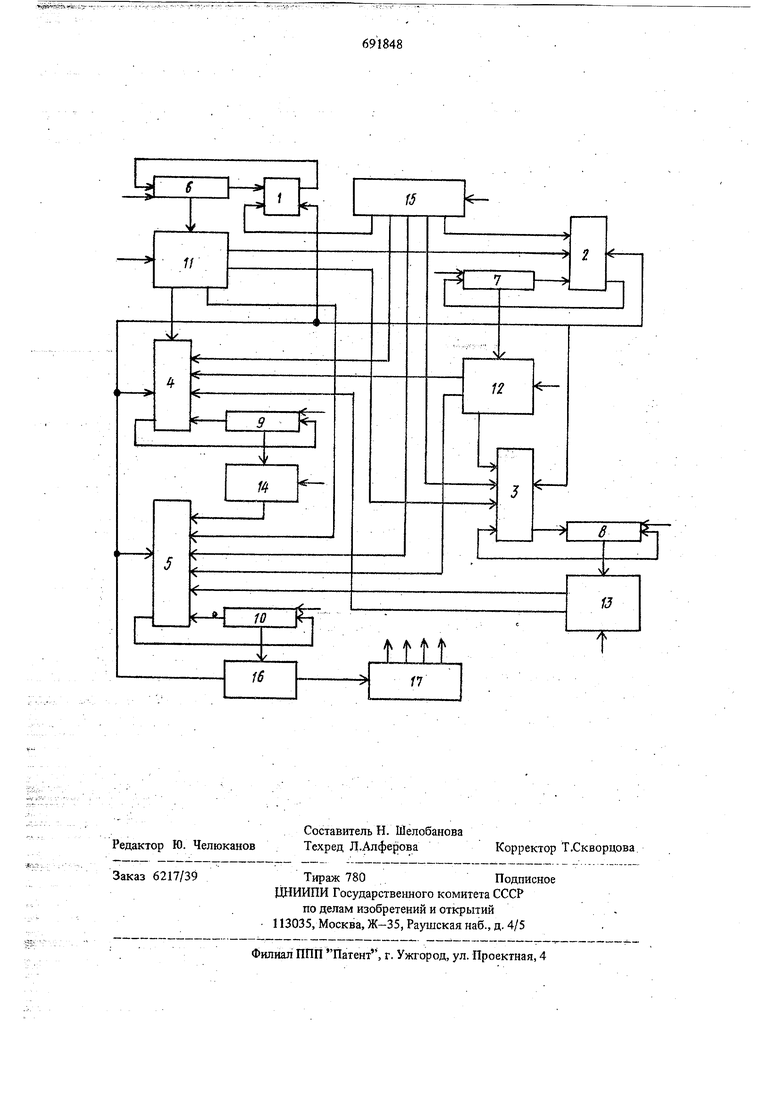

Для этого устройство содержит четыре блока умножения на коэффициенты, причем второй выход первого регистра сдвига соединен со входом первого блока умножения на коэффициенты, первый, второй, третий и четвертый выходы которого соединены соответственно с третьими входами второго третьего, четвертого и пятого сумматоров-вычитателей, второй выход второго регистра сдвига соединен со входом соответствующего блока умножения на коэффициенты, первый, второй и третий выходы которого подключены к четвертым входам соответственно третьего, четвертого и пятого сумматоров-вычитателей, второй выход |Третьего регистра сдвига соединен со входом третьего блока умножения на коэффициенты, первый и второй выходы которого соединены с пятыми входами четвертого и пятого сумматоров вычитателей соответственно, второй выход четвертого регистра сдвига подключен через четвертый блок умножения на коэффициенты к шестому входу пятого сумматоравычитателя, второй, третий, четвертый и пятый выходы блока формирования констант соединены соответственно с четвертым входом второго, с пятым входом третьего, с шесть1м входом четвертого и с седьмым входом пятого сумматоров-вычитателей, вторые входы бло ков умножения соединены с выходами блока управления. На чертеже представлено устройство для вычисления корня пятой степени, блок-схема. Устройство содержит сумматоры-вычитатели 1-5, регистры 6-10 сдвига, блоки 11-14 . 3%1Ножения на коэффициенты, блок 15 формирования констант, блок 16 сравнения и блок 17 управления. Входом устройства являются входы разрядов Сдвигающего регистра 10. Выходом устройства являются: для функции корня пятой степени из аргумента X - выходы разрядов сдвигающего регистра б, для функщги корня пятой степени из квадрата аргумента - выходы разрвдов сдвигающего регистра 7, для функции корня пятой степени из куба аргумента - выходы разрядов сдвигающего регистра 8, для функции корня пятой степени из четвертой сте пени аргумента - выходы разрядов сдвигающе го регистра 9. В основу вычисления функций положен принцип одновременного рещения в итерацион ном процессе системы разностно .итерационных рекурейтных соотношений: - - ..--. л г V. Z. ,Zj-9-jC9v5-2-- Cjio-2- 2). b.iO-2 Y;-5-r -, : J f . Qp5} nZi r l-i j-o,l,,.n; V,).-vj-г-г г- J . b;,bj c j Cj-3a4a -)v.. .(.-2-JWj-4-i- J) -(-Cj62 - u VF-. Особенностью данного алгоритма является то, что все соотношения обладают групповыми свойствами, т.е. зависят друг от друга. Вычисление указанных функций в предложенном устройстве осуществляется следующим образом. Первоначально в пятый регистр 10 заносится значение заданного аргумента X, а регистрьг 6-9 устанавливаются в нулевые состояния. В .любой j-й итерации с выходов блока 17 управления выдается серия тактовых импульсов, при помощи которых в блоках 11-14 умножения на постоянные коэффициенты вырабатываются соответствующие значения. Последние совместно с содержанием сдвигающих регистров 6-10 и константами из блока 15 продвигаются на входы сумматороввьйИтателей 1-5. Результаты алгебраического суммирования в сумматорах-вычитатёлях 1-5 с их -выходов записываются младшими разрядами вперед в освобождающиеся при сдвиге старшие разряды сдвигающих регистров 6-10 и продвигаются к их началу. После выполнения п тактов, где п - число разрядов аргумента, в сдвигающих регистрах 6-10 содержатся результаты j итерации. По знаку содержания пятого сдвигающего регистра 10 блок 16 сравнения выдает со своего первого выхода сигнал, определяющий сложение (при положительном знаке) в,сумматорах-вычитатёлях 1-5 на следующей итерации. Со второго выхода сдвигающего регистра 6 выдается значение vj в блок .11, с выходов которого вьщаются значения у;2-2 , у.-.3-2 yj4--2 и yj-52 на соответствующие входы сумматоров-вычитателей 2-5. Со второго выхода сдвигающего регистра 7 на вхрд блока 12 выдается ,значения .,. С выходов блока .12 вьодаются .знйенйй. Cj32, с-,6-2 и С:10 на соответствующие входь сумматоров-вычитателей 3-5. Со второго выхода сдвигающего регистра 8 на вход блока 13 вьгдается значение bs- С вь.гходов блока .13 выдаются значения bj4-2 H bj-102 на соответствующие входы сумматоров-вычитателей 4 и 5. Со второго выхода сдвигающего регистра 9 на вход блока 14 выдается значение а;, из которого формируется значение а-,,.,2 и подается на шестой вход сумматора-вычитатепя 5. С выходов блока 15 на (умматор-вы56читатель 1 выдается константа 2-. , на сумма тор-вычитатель 2 - константа 2 /, на сумматор-вьгЙ1татель 3 - константа 2, на сумматор-вычиуатель 4 - константа 2 и на сумматор-вычитатель 5 - константа 2 На следующей итерации вычисления произв дятся . аналогичнь1М образом. В конце каждой итерации со второго выхода сдвигающего регистра 10 на блок 16 сравнения подается очередное значение резуль тата Zj, которое сравнивается с нулем. Когда ZJ равно нулю (в пределах длин разрядной сетки), блок 16 сравне1шя выда;ет сигнал останова, в блок 17 управления, который прекращает выдавать тактовые импульсы на следующей итерации, так как процесс вычисления окончен. Каждая итерация выполняется за (n+m+ ) тактов, где m J log2n - число дополнительных защитных разрядов для компенсации погрешности усечения чисел при .сдвиге. Для сдвига и умножения промежуточных результатов необходимо от 1 до 5 тактов. Максимальное количество итераций равно (п+1). Максимальное время вычисления одновременно четырех указанных функций благодаря асинхронному режиму вычисления в тактах равно Ттах (п+1) (ntm+5) n(n+10)+9 Параллельно-последовательная структура предложенного устройства обладает простотой схемных рещений из стандартных щфровых элементов и может быть изготовлена в ввде одной БИС. Устройство совмещает требования максимал ной надежности, быстродействия, технологичности. Предложенное устройство обладает минимальными аппаратурными затратами для работы в реальном масштабе «ременИ. Информа ция вводится и выводится в одфровой-форме что позволяет легко сопрягать предложенное устройство с другими вьиислительными средствами. Предложенное устройство может быть использовано в качестве специализированного вычислительного блока в управляющих или вычислительных, системах, в настольных вычислителях и т.п. Формула изобретения Устройство для вычисления корня пятой степени, содержатдее первый, второй, третий, четвертый и пятый регистры сдвига, первые входы и первые выходы которых соединены с выходами и первыми входами соответствующих сумматоров-вычитателей, второй выход пятого регистра сдвига соединен со входом блока сравнения, один вьгход которого подключен ко вторым входам сумматоров-вычитателей, а другой - к входу блока управления, выходы которого соединены со сдвигающими входами регистров сдвига и входом блока формирования констант, первый выход котороге соединен с третьим входом первого сумматора-вьиитателя, отличающееся тем, что, с целью расширения класса решаемых задай за счет возможности вычисления корня пятой степени из аргумента и одновременно из квадрата, куба и четвертой степени аргумента, оно содержит четыре блока умножения на коэффициенты , причем второй выход первого регистра сдвига соединен со входом первого блока умножения на коэффициенты, первый, второй, третий и четвертый выходы которого соединены соответственно с третьими входами второго, третьего, четвертого и пятого сумматоров-вычитателей, второй выход второго регистра сдвига соединен со входом соответствующего блока умножения на коэффициенты, первый, второй и третий выходы которого подключены к четвертым входам соответственно третьего, четвертого и пятого сумматоров-вычитателей, второй выход третьего регистра сдвига соединен со входом третьего блока умножения на коэффищ1енты, первый и второй выходы которого соединены с пятыми входами четвертого и пятого сумматор оввычитателей соответствегшо, второй выход четвертого регистра сдвига подключен через четвертый блок умножения на коэффициенты к шестому входу пятого сумматора-вычитателя, второй, третий, четвертый и пятый, выходы блока формирования констант соединены соответственно с четвертым входом второго, с пятым входом третьего, с шестым входом четвертого и с седьмым входом пятого сумматороввычитателей, вторые входы блоков умножения на коэффициенты соединены с выходами блока управления. Источники 1шформации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N 491946, кл. G, 06 F 7/38, 1973. 2. Авторское свидетельство СССР по заявке. №2160803,07.08.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для вычисления корня -ой степени | 1977 |

|

SU742929A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU684551A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

Авторы

Даты

1979-10-15—Публикация

1976-09-03—Подача