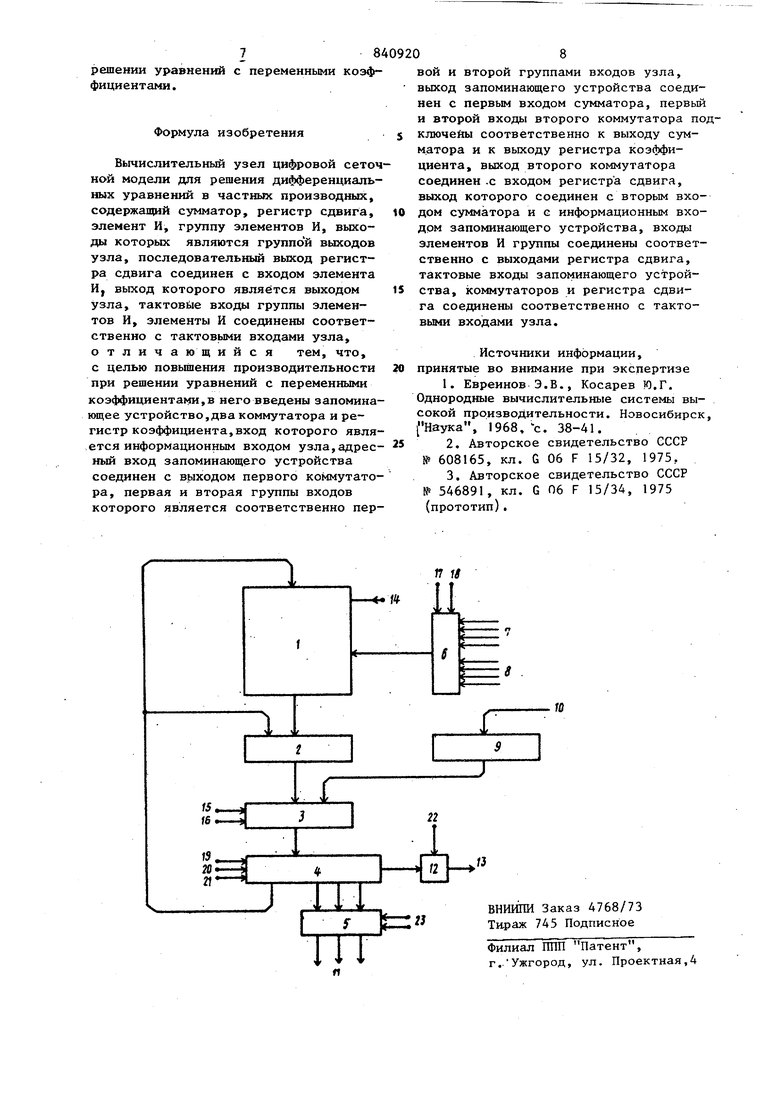

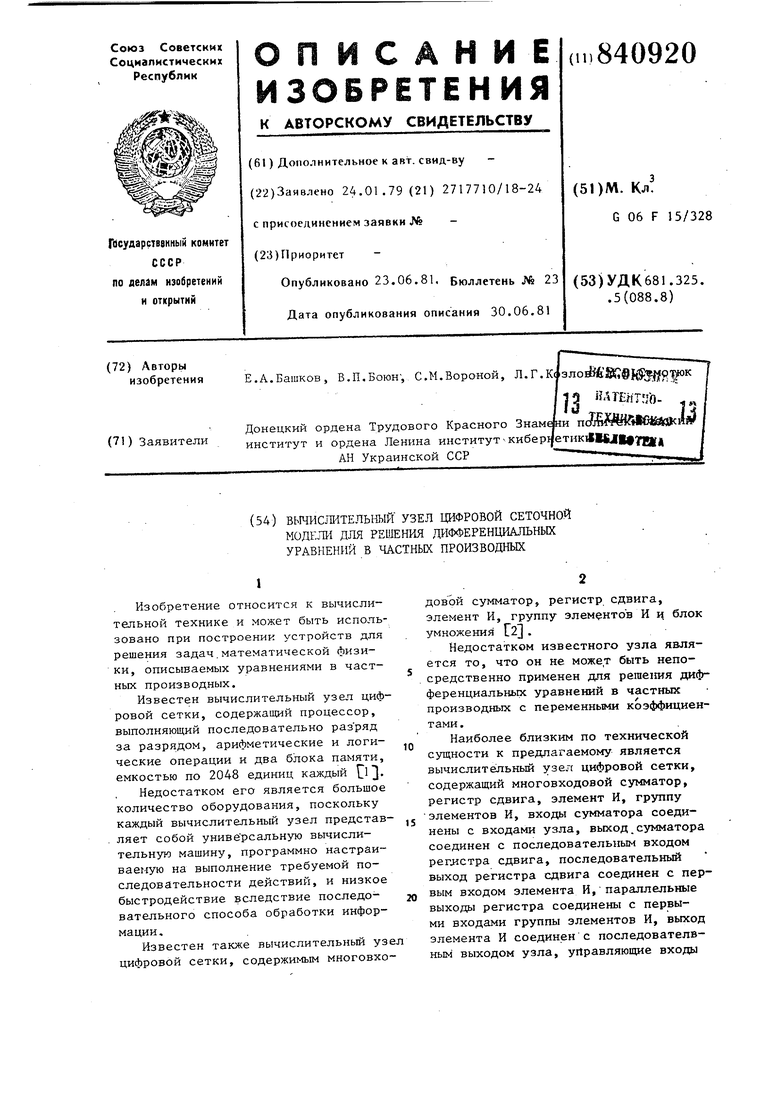

3 регистра и элементов И соединены с управляющими входами узла ГЗД. Однако известный узел не предназначен для непосредственного решения дифференциальных уравнений с переменнымии коэффициентами. Использование этого узла для решения такого класса задач требует применения двухступенчатых итерационных методов, суть которых состоит в том, что решение исходной дифференциальной задачи с переменными коэффициентами сводится к многократному решению соответствующих более простых дифференциальных задач с постоянными коэф фициентами. Время решения задачи при этом существенно увеличивается. Цель изобретения - повьш1ение производительности при решении уравнени с переменными коэффициентами. Поставленная цель достигается тем, что вычислительный узел цифрово сеточной модели для решения дифференциальных -уравнений в частшях производных, содержащий сумматор, регистр сдвига, элемент И, группу элементов И, выходы которых являются группой выходов узла, последовательный выход регистра сдвига соединен с. входом элемента И, выход которого является выходом узла, тактовь вхощл группы элементов И, элементы И соединены соответственно с тактовыми входами узла, введены запоминающие устройство, два коммутатора и регистр коэффициентаj вход которого является информационным входом уз ла, адресный вход запоминающего устройства соединен с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно первой и второй группами входов узла, выход запоминающего уст ройства соединен с первым входом су матора, первый и второй входы второго коммутатора подключены соответственно к выходу сумматора и к выход регистра коэффициента, выход второго коммутатора соединен с входом регистра сдвига, выход которого соединен с вторым входом сумматора и с ин формационным входом запоминающего устройства, входы элементов И группы соеденены соответственно с выходами регистра сдвига, тактовые входы запоминающего устройства, коммутаторов и регистра сдвига соединены соответственно с тактовыми входами узла. На чертеже представлена схема предлагаемого устройства. Оно содержит запоминающее устройство 1 , сумматор 2, коммутатор 3, регистр 4 сдвига, группу элементов И 5, коммутатор 6 с группами входов 7 и 8, регистр 9 коэффициента с информационным входом 10, выходы 11 узла, зле14ент И 12, выход 13 узла, тактовые входы 14-23 узла. Рассматриваемый узел предназначен для реализации зависимости . П 4., п( +Г llW -л П 4, li ,..b i-ii,,i к которой сводится решение дифференциальных уравнений с переменными коэффициентами методом простой итерации, где i, j - индексы строки и столбца сеточной области; . Ц-, С,-., d - , И соответственно приведенные коэффициенты и правая часть разностньпс уравнений; , , U.;. U/,,,значения исконной функции в соседних узлах на предыдущей итерации; и(новое приближение решения. Вычисление последующего приближения решения состоит из двух этапов в общем случае. На первом этапе в запоминающее устройство узла заносится сочетание сумм коэффициентов по О, 1, 2, 3, 4 членов. При этом соответствие между адресами ячеек запоминающего устройства и их содержимым устанавливается зависимостью Vi,,,.i т гдеГсА. oL/j двоичный адрес ячейки запоминающего устройства. При занесении информации в запоминающее устройство используются входы 8 для задания адреса запоминающего устройства узла и вход 10 для задания коэффициентов узла. Коэффициент заносится в регистр 9 коэффициента и по управляющему сигналу на тактовом входе 15 второго коммутатора 3 передается параллельным кодом в регистр 4 сдвига. На входы 8 узла подается адрес 0001, который коммутатором 6 подключается к адресному входу запот минающего устройства 1. На вход 14 подается сигнал записи в запоминающее устройство и коэффициент i j помещается в первую ячейку запоминающего устройства. В нулевой ячейке постоянно хранится код нудя. Далее выполняется два цикла формирования содержимого второй и третьей ячеек запоминающего устройства. в регистр У заносится коэффициент который по управляющему сигналу на входе 15 через коммутатор 3 передается в регистр 4. На входы 8 узла подается адрес 0000, который коммутатором 6 по управляющему сигналу на входе 18 узла подключается к адресному входу запоминающего устройства I. На вход 14 узла подается сигнал, чтение запоминающего устройства и коэффициент суммируется на сумматоре 2 с содержимым нулевой ячейки запоминающего устройства. Результат суммирования по управляющему сигналу на входе 16 узла через коммутатор 3 принимается в регистр 4 по сигналу на входе 19 узла. После этого на входе 8 узла подается адрес 0010, который коммутатором 6 по сигналу на входе 18 подключается адресному входу запоминающего устройства, на вход 14 узла подается сигнал записи в запоминающее устройство и содержимое старших разрядов регистра 4 помещается во вторую яче ку запоминающего устройства. В результате следующего цикла вновь про исходит занесение коэффициента C,j в регистр 4 через коммутатор 3, чтени из первой ячейки запоминающего уст ройства коэффициента ctj;,j, суммиров ние на сумматоре 2 содержимого реги стра 4 с данными запоминающего устройства, запоминание результата суммирования на регистре 4 сдвига и запись по адресу 0011 в запоминающее устройство. Далее в регистр 9 заносится коэффициент Ь и в течение последующих четырех цик лов; занесение коэффициента в регистр 4, чтение из запоминающего устройства, суммирование, запись в запоминающее устройство формируется содержимое ячеек 4-7 запоминающего устройства. При этом на входе 9 адреса должны подаваться в следующей последовательности: 0000, 0100, 000 0101, 0010, ОНО, ООП, 0111. После этого в регистр 9 заносится коэффициент а : и в течение 8 последующих циклов формируется содержимое ячеек 8-15. .Адреса на вход запоминающего устройства подаются в такой последо 04 вательности: 0000, 1000, 0001, 1001, ..., 0110, 1110, 0111, 1111. По окон-, чании формирования содержимого запоминающего устройства в регистр 9 заносится значение f - -. На втором этапе осуществляется вычисление нового приближения решения. По сигналу на входе 21 старшие разряды регистра 4 устанавливаются в ноль. Далее устройство работает по следующему циклическому алгоритму. На входы узла 7 подается последовательный код значений искомой функции на предыдущей итерации младшими разрядами вперед. Каждый разряд этих значений через коммутатор 6 по управляющему сигналу на входе 17 узла подается на адресный вход запоминающего устройства. На вход 14 подается сигнал чтения запоминающего устройства. Из ячейки запоминающего устройства, адрес которой определяется кодом, выбирается очередное, ранее подготовленное, частичное произведение, которое на сумматоре 2 складьшается с содержащий старщих разрядов регистра 4 сдвига. По сигналу, подаваемому на вход 16, сумма с выходов сумматора 2 принимается в старшие разряды регистра 4 по сигналу на входе 19, Под управлением сигнала, поступающему на вход 20, осуществляется.сдвиг содержимого регистра 4 на один разряд вправо, Код значения искомой функции, на предыдущей итерации, хранящийся в младших разрядах регистра 4 сдвига выдается на выход 13 узла через элемент И 12, который открывается сигналом, поступающим на вход 22,После прохождения п - тактов работы, где п - разрядность Ц-Л регистре 4 получается очередное приближение искомой функции, В течение последующих т+2 тактов (т - разрядность коэффициентов) старшие разряды найденного значения искомой функции сдвигаются в младшие разряды регистра 4 сдвига при этом элемент И 12 закрыт, Последуюпще итерации осуществляются аналогично и когда решение получено, на вход 23 поступает сигнал,который открывает группу элементов И 5, через которую результат выдается из младших разрядов регистра сдвига на группу выходов11 узла. Предлагаемое изобретение позволяет повысить производительность при решении уравнений с переменными коэффициентами. Формула изобретения Вычислительный узел цифровой сеточ иой модели для решения дифференциальных уравнений в частных производнык, содержащий сз мматор, регистр сдвига, элемент И, группу элементов И, выходы которых являются группой выходов узла, последовательный выход регистра сдвига соединен с входом элемента I выход которого является выходом узла, тактовйе входы группы элементов И, элементы И соединены соответственно с тактовыми входами узла, отличающийся тем, что, с целью повышения производительности при решении уравнений с переменными коэффициентами,в него введены запоминающее устройство,два коммутатора и регистр коэффициента, вход которого является информационным входом узла,адресный вход запоминающего устройства соединен с выходом первого коммутатора, первая и вторая группы входов которого является соответственно первой и второй группами входов узла, выход запоминающего устройства соединен с первым входом сумматора, первый и второй входы второго коммутатора подключейы соответственно к выходу сумматора и к выходу регистра коэффициента, выход второго коммутатора соединен .с входом регистра сдвига, выход которого соединен с вторым входом сумматора и с информационным входом запоминающего устройства, входы элементов И группы соединены соответственно с выходами регистра сдвига, тактовые входы запоминающего устройства, коммутаторов и регистра сдвига соединены соответственно с тактовыми входами узла. Источники информации, принятые во внимание при экспертизе 1.Евреинов Э.В., Косарев Ю.Г. Однородные вычислительные системы высокой производительности. Новосибирск, (Наука, 1968, с. 38-41. 2.Авторскоесвидетельство GCCP № 608165, кл. G06 F 15/32, 1975, 3.Авторскоесвидетельство СССР № 546891, кл. GП6 F 15/34, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Вычислительный узел цифровой сеточной модели для решения дифференциальных уравнений в частных производных | 1980 |

|

SU894717A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для решения систем ли-НЕйНыХ уРАВНЕНий | 1978 |

|

SU813446A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Вычислительное устройство для решения дифференциальных уравнений | 1985 |

|

SU1277134A1 |

| Устройство для решения интеграль-НыХ уРАВНЕНий | 1979 |

|

SU817726A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

Авторы

Даты

1981-06-23—Публикация

1979-01-24—Подача