(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1141454A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Резервированное запоминающее устройство | 1984 |

|

SU1239751A2 |

Изобретение относится к области вычислительной техники. Известно ЗУ с самоконтролем , содержащее два рабочих и один резерв ный блок памяти (в который заносится сумма по модулю два информации с одинаковыми с1дресс1ми на рабочих блоков памяти), коммутаторы и блоки контроля l. Недостатками этого устройства являются наличие большего количества нерезервированного оборудрвания (что снижает надежность устройства) и недостаточно быстродействие (информация из блоков памяти на выход устро ства проходит через большое количество, регистров и схем И и ИЛИ). Наиболее близким по технической сущности к изобретению явлйется резервированное ЗУ ,С41содержащее регистр адреса, рабочие и резервный блоки памяти, коммутаторы, сумматор регистр числа и дополнительный регистр. При парировании неисправност параллельно с записью числа из первого (второго) рабочего блока на регистр числа записывается сумма чисел из второго (первого) и резерв ного блоков на дополнительный регис Однако данное устройство обладает недостаточным быстродействием, поскольку информация на выход устройства поступает после промежуточного хранения на регистре числа или дополнительном регистре. Это сужает область применения устройства. Кроме того, устройство содержит сравнительно большое количество нерезервированного оборудования (регистр числа, дополнительный регистр), что снижает надежность устройства. Целью изобретения является повышенлсе быстродействия и надежности. Поставленная цель достигается тем, то в резервированное ЗУ,содержащее регистр адреса,выходы которого соединены со входс1ми двух рабочих и резервного блоков памяти,первый и второй коммутаторы, входы которых подключены к соответствующим выходам рабочих .блоков памяти, а управляющие входы к управляющему выходу регистра адреса, сумматор, первые входы которого подключены к выходам второго коммутатора, а вторые входы - к выходам резервного блока памяти, блок контроля, вход и выход которого подключены соответственно к первым входам и

управляющему входу третьего коммутатора, генератор-. тактовых импульсов, введены элементы И, первые входы которых подключены к выходам третьего коммутатора, вторые входы - к выходу генератора тактовых импульсов, авыход является выходом устройства.Выходы первого коммутатора подключены к входам блока контроля, а выход сумматора -ко вторым входам третьего коммутатора.

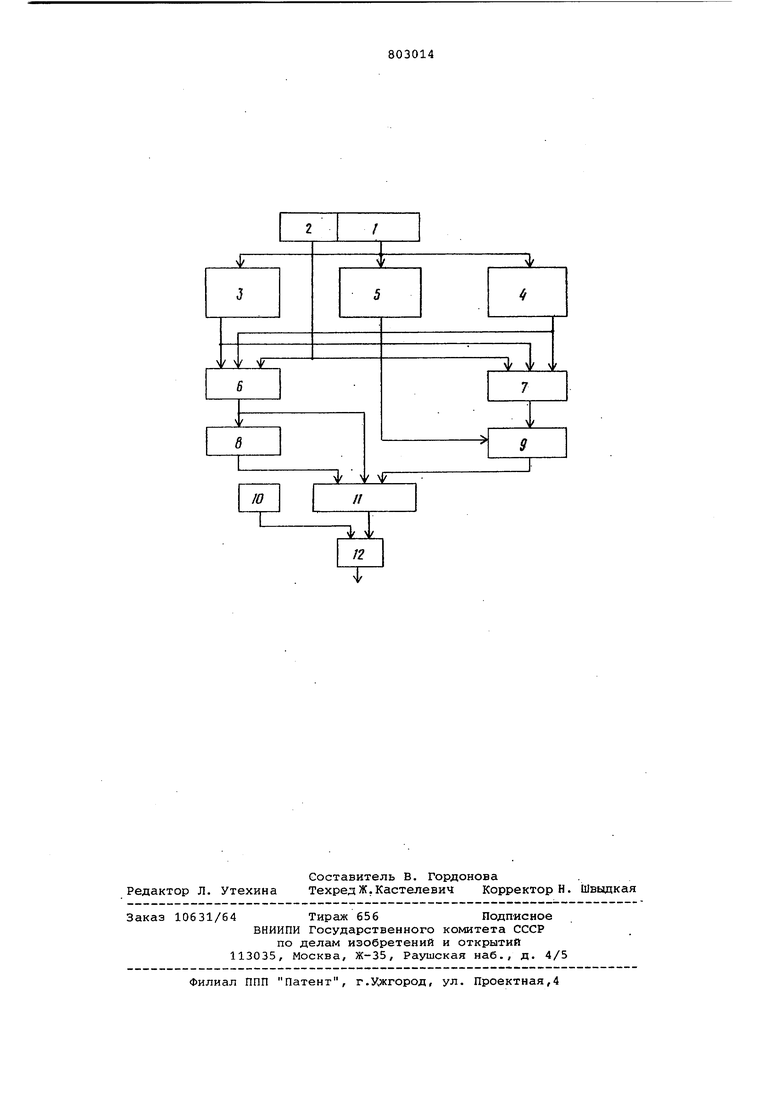

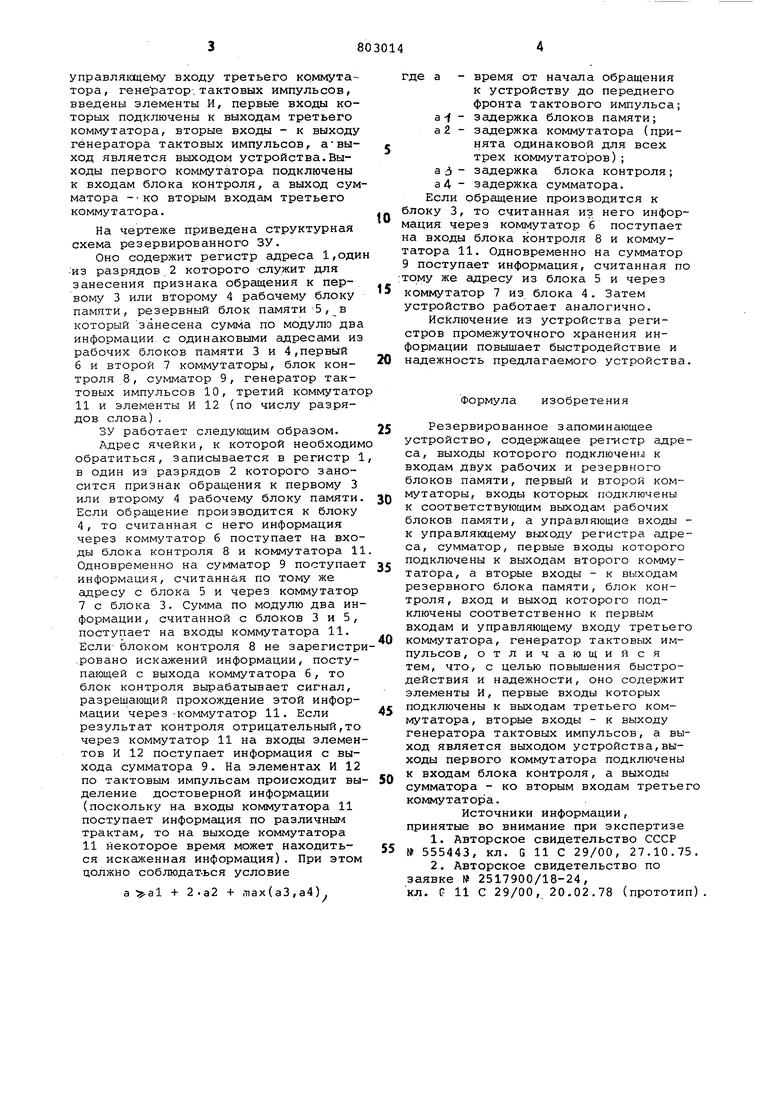

На чертеже приведена структурная схема резервированного ЗУ.

Оно содержит регистр адреса 1,оди из разрядов 2 которого служит для занесения признака обращения к первому 3 или второму 4 рабочему блоку памяти, резервный блок памяти -5,в который занесена сумма по модулю два информации, с одинаковыми адресами из рабочих блоков памяти 3 и 4,первый б и второй 7 коммутаторы, блок контроля 8, сумматор 9, генератор тактовых импульсов 10, третий коммутато 11 и элементы И 12 (по числу разрядов слова).

ЗУ работает следующим образом. Адрес ячейки, к которой необходим обратиться, записывается в регистр 1 в один из разрядов 2 которого заносится признак обращения к первому 3 или второму 4 рабочему блоку памяти. Если обращение производится к блоку 4, то считанная с него информация через коммутатор б поступает на входы блока контроля 8 и коммутатора 11 Одновременно на сумматор 9 поступает информация, считанная по тому же адресу с блока 5 и через коммутатор 7 с блока 3. Сумма по модулю два информации, считанной с блоков 3 и 5, поступает на входы коммутатора 11. Если блоком контроля 8 не зарегистри.ровано искажений информации, поступающей с выхода коммутатора б, то блок контроля вырабатывает сигнал, разрешающий прохождение этой информации через Коммутатор 11. Если результат контроля отрицательный,то через коммутатор 11 на входы элементов И 12 поступает информация с выхода сумматора 9. На элементах И 12 по тактовым импульсам происходит выделение достоверной информации (поскольку на входы коммутатора 11 поступает информация по различным трактам, то на выходе коммутатора 11 некоторое время может находиться искаженная информация). При этом должно соблюдат-ься условие

а al + 2-а2 + гпах(аЗ,а4)

где а - время от начала обращения к устройству до переднего фронта тактового импульса; а-f - задержка блоков памяти; а 2 - задержка коммутатора (принята одинаковой для всех трех коммутаторов); а 3 - задержка блока контроля; а4 - задержка сумматора. Если обращение производится к блоку 3, то считанная из него информация через коммутатор б поступает на входы блока контроля 8 и коммутатора 11. Одновременно на сумматор 9 поступает информация, считанная по тому же адресу из блока 5 и через коммутатор 7 из блока 4. Затем устройство работает анешогично.

Исключение из устройства регистров промежуточного хранения информации повышает быстродействие и надежность предлагаемого устройства.

Формула изобретения

Резервированное запоминающее устройство, содержащее рег-истр адреса, выходы которого подключены к входам двух рабочих и резервного блоков памяти, первый и второй коммутаторы, входы которых подключены к соответствующим выходам рабочих блоков памяти, а управляющие входы к управляющему выходу регистра адреса, сумматор, первые входы которого подключены к выходам второго коммутатора/ а вторые входы - к выходам резервного блока памяти, блок контроля , вход и выход которого подключены соответственно к первым входам и управляющему входу третьего коммутатора, генератор тактовых импульсов , отличающийся тем,, что, с целью повышения быстродействия и надежности, оно содержит элементы И, первые входы которых подключены к выходам третьего коммутатора, вторые входы - к выходу генератора тактовых импульсов, а выход является выходом устройства,выходы первого коммутатора подключены к входам блока контроля, а выходы сумматора - ко вторым входам третьег коммутатора.

Источники информации, принятые во внимание при экспертизе

555443, кл. G 11 С 29/00, 27.10.75

кл. G 11 С 29/00, 20.02.78 (прототип

Авторы

Даты

1981-02-07—Публикация

1978-12-07—Подача