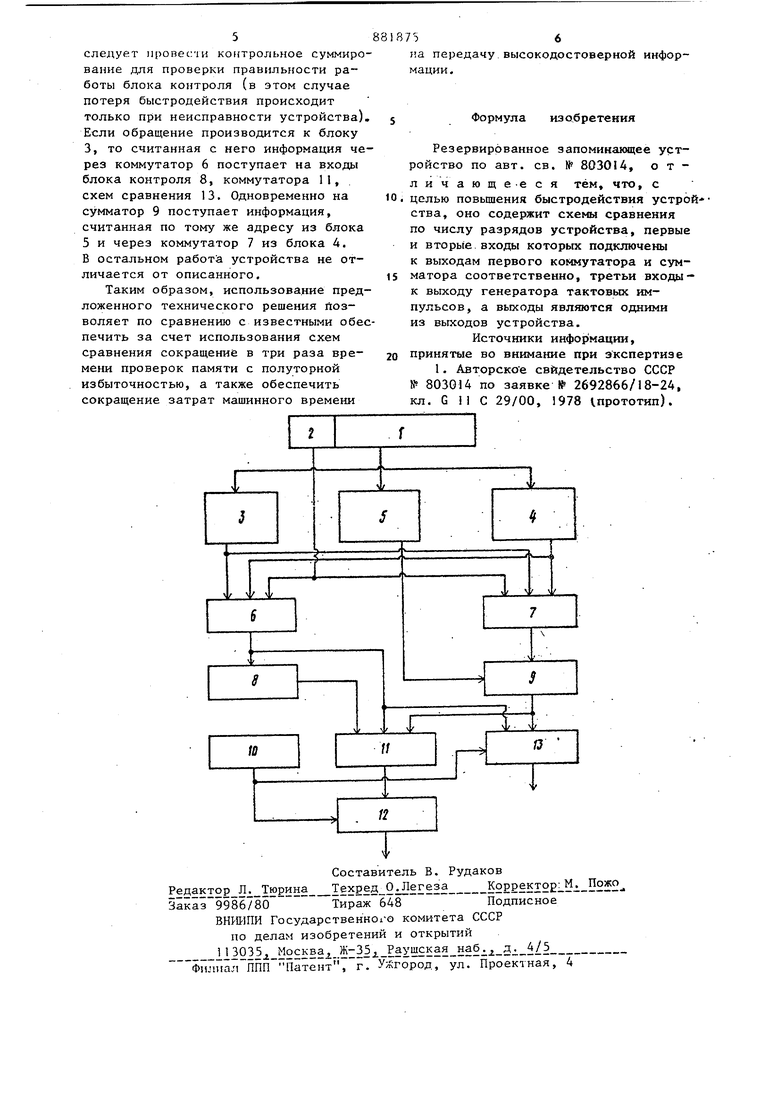

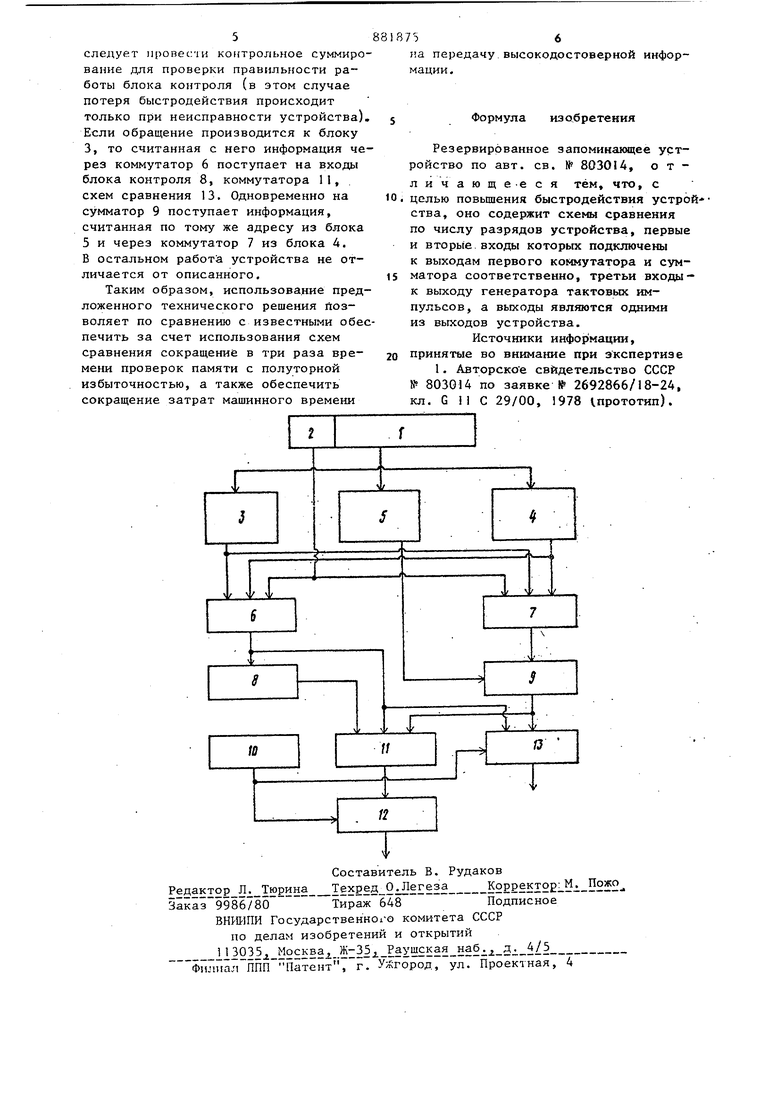

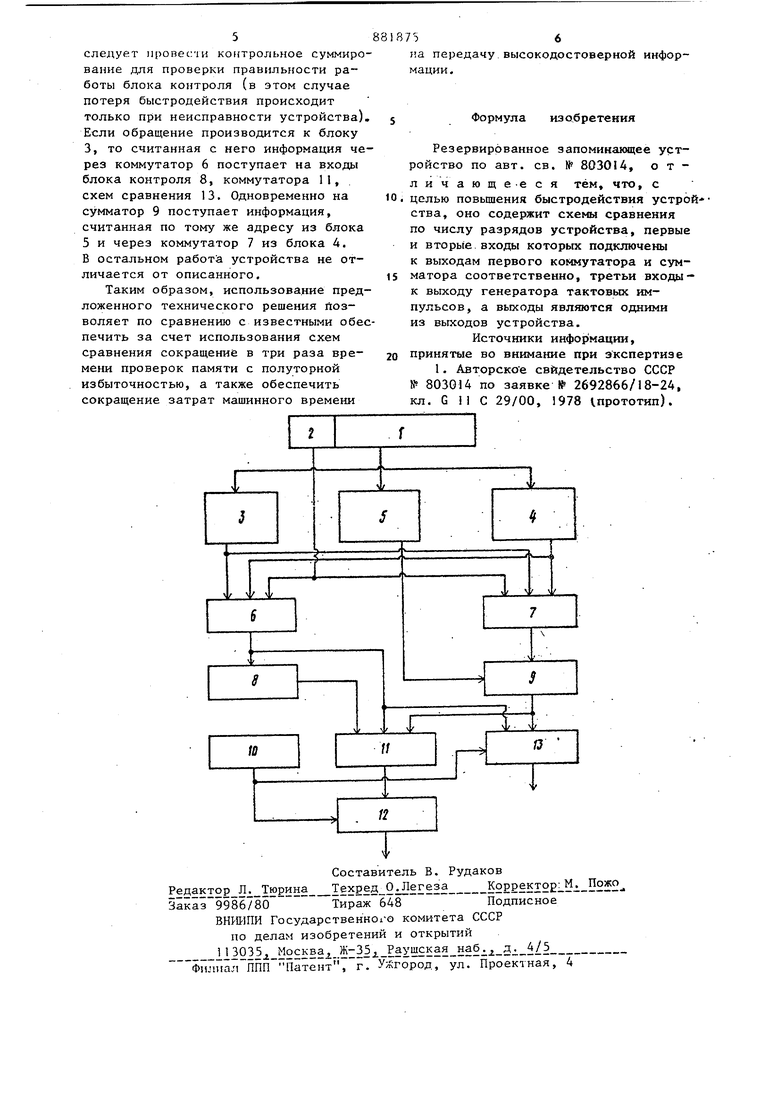

(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ Изобретение относится к запоминающим устройствам. Известно устройство по основному авт. св. № 803014, содержащее регист адреса, выходы которого подключены к входам двух рабочих и резервного блоков памяти, первый и второй комму таторы, входы которых подключены к соответствующим выходам рабочих блоков памяти, а управляющие входы - к управляющему выходу регистра адреса, сумматор, первые входы которого подключены к выходам второго коммутатора, а вторые входы - к выходам резер ного блока памяти, блок контроля, вход и выход которого подключены соответственно к первым входам и управляющему входу третьего коммутатора, генератор тактовых импульсов, элементы И, первые входы которых подключены к выходам третьего коммутатора, вторые входы - к выходу генератора тактовых импульсов, а выход УСТРОЙСТВО является выходом устройства, выходы первЬго коммутатора подключены к входам блока контроля, а выходы второго коммутатора - ко входам сумматора I . Недостатками этого устройства являются больщое время проверки устройства, так как проверка предполагает последовательное во времени суммирование каждого из трех блоков памяти, и большие временные затраты на контрольное суммирование массивов при передаче высокодостоверной информации. Эти временные затраты обусловлены тем, что в ряде типов памяти возможно при одной неисправности появление ошибок в нескольких разрядах информации одновременно (например, в жгутовой памяти), при этом на выходе устройства возможно появление неверной информации, вследствие ограниченной эффективности схемы контроля. Указанные недостатки снижают быстродействие устройства. Цель изобретения - повышение быс действия устройства. Поставленная цель достигается тем что в резервированное запоминающее устройство введены схемы сравнения по числу разрядов устройства, первые и вторые входы которых-подключены к выходам первого коммутатора и сумматора соответственно, третьи входы к выходу генератора тактовых импульсов , а выходы являются одними из выходов устройства. На чертеже приведена функциональная схема предложенного устройства. Устройство содержит регистр адреса 1, один из разрядов 2 которого служит для занесения признака обраще ния к первому 3 или второму А рабочим блокам памяти, резервный блок па мяти 5, в который занесена сумма по модулю два информации с одинаковыми адресами из рабочих блоков памяти 3 и 4, первый коммутатор 6, второй коммутатор 7, блок контроля 8, сумматор 9, генератор тактовых импульсов 10, третий коммутатор П, элементы И (по числу разрядов устройства) 12, схемы сравнения (по числу разрядов устройства) 13. Выходы блоков памяти 3 и 4 и один из выходов регистра 1 (являющийся разрядным выходом разряда 2 регистра l) подключены соответственно ко входам коммутаторов 6 и 7. Входы сумматора 9 подключены соответственно к выхода блока памяти 5 и коммутатора 7. Вход блока контроля 8 подключены к выход коммутатора 6. Входы коммутатора 1 1 подключены соответственно к выходам блока контроля 8, коммутатора 6 и сумматора 9. Входы элементов И 12 подключены к выходам генератора так товых импульсов 10 коммутатора. 11. Выходы элементов И 12 являются выходами устройства. Первые и вторые вхо схем сравнения 13 подключены к выходам первого коммутатора 6 и сумматор 9 соответственно. Третьи входы схем сравнения подключены к выходу генера тора тактовых импульсов 10. С выходов схем сравнения 13, являющихся одними из выходов устройства, снимаю ся сигналы неисправности. Работа запоминающего устройства происходит следующим образом. Адрес ячейки, к которой необходим обратиться, записывается в регистр 1, в один из разрядов 2 которого заносится признак обращения к первому 3 или второму 4 рабочему блоку памяти. Если обращение производится к блоку 4, то считанная с него информация через коммутатор 6 поступает на входы блока контроля 8, коммутатора 11 и схемы сравнения 13. Одновременно на сумматор 9 поступает информация, считанная по тому же адресу с блока 5 и через коммутатор 7 с блока 3. Сумма по модулю два информации, считанной с блоков 3 и 5, поступает на входы коммутатора 1 1 и схем сравнения 13. Если блоком контроля 8 не зарегистрировано искажений информации, поступающей с выхода коммутатора 6, то блок контроля вырабатывает сигнал, разрешающий прохождение этой информации через коммутатор I1. Если результат контроля отрицательный, то через коммутатор 11 на входы элементов И 12 поступает информация с выхода сумматора 9. На элементах И 12 тактовым импульсам происходит выделение считываемой информации. Одновременно с выделением информации на элементах И 12 по тактовым импульсам в схемах сравнения 13 сравнивается информация из блока 4, поступающая с выхода коммутатора 6, с суммой по модулюдва информации из блоков 3 и 5, поступающей с выхода сумматора, Таким образом, с высокой достоверностью производится одновременный контроль информации из всех трех блоков памяти 3-5. Это позволяет при считывании информации с Одного рабочего блока памяти (.при проверках) сделать заключение об исправности всего резервированного устройства. При этом время проверки сокращается более чем в три раза и упрощается алгоритм проверки не требуется суммирования информации). При исправности всех трех блоков памяти 3-5 с помощью схем сравнения можно сделать вывод о достоверности передаваемой информации также без суммирования, т.е. без дополнительных временных затрат. В известном устройстве суммирование в некоторых случаях необходимо (если возможны отказы большой кратности), поскольку достоверность обнаружения блоком контроля отказов большой кратности меньше.единицы. Если схемы сравнения зафиксировали неисправность одного из блоков памяти, то для повьш1еШ1Я достоверности передачи информации

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1141454A1 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

Авторы

Даты

1981-11-15—Публикация

1979-11-26—Подача