(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1141454A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

1

Изобретение относится к запоминающим устройствам.

Известно резервированное запоминающее устройство, содержащее рабочие и резервные блоки памяти, адресные регистры, коммутаторы, блоки контроля 1.

Недостатком этого устройства является ограниченная область применения, так как оно не парирует неисправности, возникщиге в ходе работы (неисправные ячейки в рабочих блоках этих устройств должны быть выявлены заранее и их содержимое должно быть занесено в резерные блоки памяти).

Наиболее близким по техническому рещению к предложенному является резервированное запоминающее устройство, содержащее регистр адреса, два рабочих и один резервный блоки памяти, три коммутатора, блок контроля, сумматор, генератор тактовых импульсов, элементы И 2.

Недостатком, данного устройства является ограниченное быстродействие вследствие выдачи на выход устройства информации только из одного (первого или второго) рабочих блоков за одно обращение к памяти, наличия дополнительных задержек при выдаче информации из памяти за прохождения информации через ряд логических устройств (коммутаторы, элементы И).

Существенное увеличение быстродействия памяти невозможно без увеличения разрядности блока памяти (формата слова).

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройст10во, содержащее регистр адреса, выходы которого соединены с входами рабочих и резервного блоков памяти, первый сумматор, одни из входов и выходы которого соединены соответственно с выходами резервного блока памяти и с одними из информационных вхо15дов первого коммутатора, управляющий вход которого соединен с выходом первого блока контроля, а выходы подключены к первым входам элементов И, вторые входы которых соединены с выходом генератора

20 Tai TOBbix импульсов, а выходы являются одними из выходов устройства, введены дополнительные элементы И и вторые коммутатор, блок контроляи сумматор, причем первые входы дополнительных элементов И

подключены к выходам второго коммутатора, вторые входы - к выходу генератора тактовых импульсов, а выходы являются другими выходами устройства, одни из входов второго сумматора подключены к выходам резервного блока памяти, другие - к выходам первого рабочего блока памяти, входам riepвого блока контроля и другим информационным входам первого коммутатора, выходы второго рабочего блока памяти соединены с другими входами первого сумматора, входами второго блока контроля и одними из информационных входов второго коммутатора, другие информационные входы которого подключены к выходам второго сумматора, а управляющий вход соединен с выходом второго блока контроля.

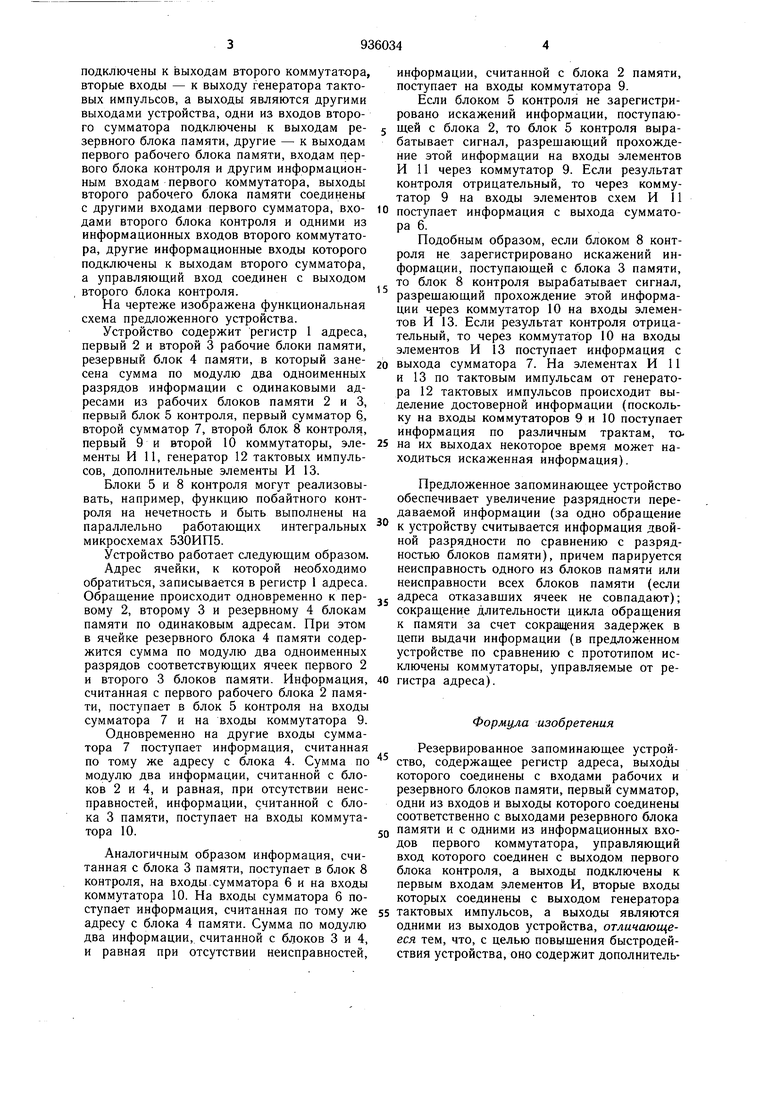

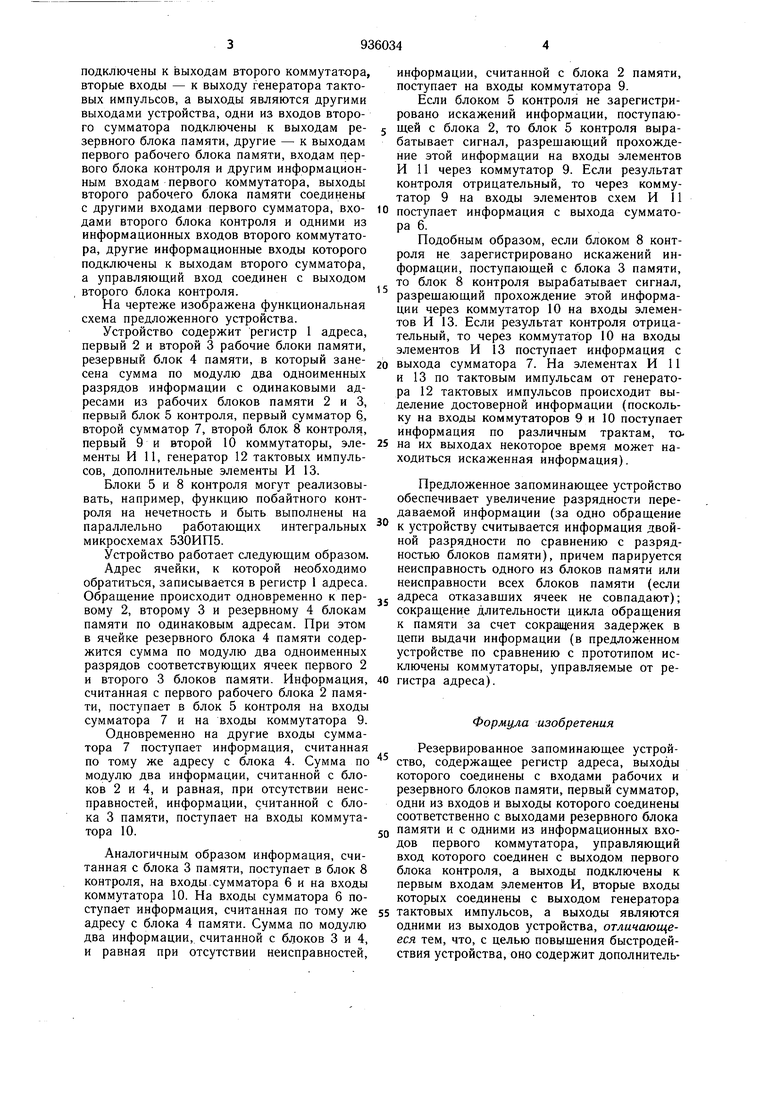

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит регистр 1 адреса, первый 2 и второй 3 рабочие блоки памяти, резервный блок 4 памяти, в который занесена сумма по модулю два одноименных разрядов информации с одинаковыми адресами из рабочих блоков памяти 2 и 3, первый блок 5 контроля, первый сумматор 6, второй сумматор 7, второй блок 8 контроля, первый 9 и второй 10 коммутаторы, элементы И 11, генератор 12 тактовых импульсов, дополнительные элементы И 13.

Блоки 5 и 8 контроля могут реализовывать, например, функцию побайтного контроля на нечетность и быть выполнены на параллельно работающих интегральных микросхемах 530ИП5.

Устройство работает следующим образом. Адрес ячейки, к которой необходимо обратиться, записывается в регистр 1 адреса. Обращение происходит одновременно к первому 2, второму 3 и резервному 4 блокам памяти по одинаковым адресам. При этом в ячейке резервного блока 4 памяти содержится сумма по модулю два одноименных разрядов соответствующих ячеек первого 2 и второго 3 блоков памяти. Информация, считанная с первого рабочего блока 2 памяти, поступает в блок 5 контроля на входы сумматора 7 и на входы коммутатора 9. Одновременно на другие входы сумматора 7 поступает информация, считанная по тому же адресу с блока 4. Сумма по модулю два информации, считанной с блоков 2 и 4, и равная, при отсутствии неисправностей, информации, считанной с блока 3 памяти, поступает на входы коммутатора 10.

Аналогичным образом информация, считанная с блока 3 памяти, поступает в блок 8 контроля, на входы.сумматора 6 и на входы коммутатора 10. На входы сумматора 6 поступает информация, считанная по тому же адресу с блока 4 памяти. Сумма по модулю два информации, считанной с блоков 3 и 4, и равная при отсутствии неисправностей.

информации, считанной с блока 2 памяти, поступает на входы коммутатора 9.

Если блоком 5 контроля не зарегистрировано искажений информации, поступающей с блока 2, то блок 5 контроля вырабатывает сигнал, разрещающий прохождение этой информации на входы элементов И 11 через коммутатор 9. Если результат контроля отрицательный, то через коммутатор 9 на входы элементов схем И 11

поступает информация с выхода сумматора 6.

Подобным образом, если блоком 8 контроля не зарегистрировано искажений информации, поступающей с блока 3 памяти, то блок 8 контроля вырабатывает сигнал, разрещающий прохождение этой информации через коммутатор 10 на входы элементов И 13. Если результат контроля отрицательный, то через коммутатор 10 на входы элементов И 13 поступает информация с

выхода сумматора 7. На элементах И 11 и 13 по тактовым импульсам от генератора 12 тактовых импульсов происходит выделение достоверной информации (поскольку на входы коммутаторов 9 и 10 поступает информация по различным трактам, тона их выходах некоторое время может находиться искаженная информация).

Предложенное запоминающее устройство обеспечивает увеличение разрядности передаваемой информации (за одно обращение

к устройству считывается информация двойной разрядности по сравнению с разрядностью блоков памяти), причем парируется неисправность одного из блоков памяти или неисправности всех блоков памяти (если

адреса отказавщих ячеек не совпадают); сокращение длительности цикла обращения к памяти за счет сокращения задержек в цепи выдачи информации (в предложенном устройстве по сравнению с прототипом исключены коммутаторы, управляемые от регистра адреса).

Формула изобретения

Резервированное запоминающее устройство, содержащее регистр адреса, выходы которого соединены с входами рабочих и резервного блоков памяти, первый сумматор, одни из входов и выходы которого соединены соответственно с выходами резервного блока

памяти и с одними из информационных входов первого коммутатора, управляющий вход которого соединен с выходом первого блока контроля, а выходы подключены к первым входам элементов И, вторые входы которых соединены с выходом генератора

тактовых импульсов, а выходы являются одними из выходов устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит дополнительные элементы И и вторые коммутатор, блок контроля и сумматор, причем первые входы дополнительных элементов И подключены к выходам второго коммутатора, вторые входы - к выходу генератора тактовых импульсов, а выходы являются другими выходами устройства, один из входов второго сумматора подключены к выходам резервного блока памяти, другие - к выходам первого рабочего блока памяти, входам первого блока контроля и другим информационным входам первого коммутатора, выходы второго рабочего блока памяти соединены

с другими входами первого сумматора, входами второго блока контроля и одними из информационных входов второго коммутатора, другие информационные входы которого подключены к выходам второго сумматора, а управляющий вход соединен с выходом второго блока контроля.

Источники .информации, принятые во внимание при экспертизе 1. Патент США № 3659275, кл. 340-172.5, опублик. 1977.

2 Авторское свидетельство СССР № 803014, кл. G 11 С 29/00, 1978 (прототип).

Авторы

Даты

1982-06-15—Публикация

1980-06-16—Подача