H;io6p( относится к вычислительnoii технике и может быть использовано при построении запоминающих уст)ойст).

Известно резервированное запоминающее устройство, содержащее блоки памяти, пени формирования адреса и коммутации информации. Парирование неисправностей в этом устройстве осуществляется путем целочисленного резервирования блоков памяти I.

Недостатком указанного устройства является большой объем резервного оборудования памяти.

Наиболее близким к пред;1агаемому является резервированное запоминающее устрорктво, содержащее регистр адреса, два рабочих блока памяти, резервный блок памяти (в который занесена поразрядная сумма по Л)дулю два информации ячеек с одинаковыми адресами рабочих блоков памяти), первый и второй коммутаторы, входы которых соединены с соответствующими выходами рабочих блоков памяти, .а управляющие входы -соединены с управляющими выходами регистра адреса, -сумматор, первые входы которого соединены с выходами второго коммутатора, а вторые входы соединены с выходами резервного блока памяти, блок контроля, третий коммутатор, генератор тактовых импульсов, элементы И 2.

Недостатком известного устройства является то, что при создании высоконадежною резервированного запоминающего устройства при меньшем, по сравнению с прототипом, резервном оборудовании памяти требуется большой объем оборудова |ия, общего для всех блоков памяти. Данный недостаток проявляется в значительном усложнении второго коммутатора при увеличении количества рабочих блоков памяти, приходящихся на один резервный блок, и в сниженли надежности устройства.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что резервированном запоминающем устройстве, содержащем регистр адреса, одни из выходов которого соединены с . входами рабочих и резервного блоков памяти, первый коммутатор, входы которого соединены с выходами рабочих блоков памяти, а управляющие входы .- с другими выходами регистра адреса, Сумматор, одни из входов которого соединены с выходами резервного блока памяти, а выходы подключены к одним из входов второго коммутатора, другие входы которого соединены с выходами первого коммутатора и входами блока контроля, выход которого соединен с управляющими входами второго коммутатора, элементы И, первые входы которых соединены с выходом генератора тактовых импульсов,-вторые входы - с .выхрдами второго коммутатора, а выходы являются

н),хплами устройства, , не ихолы сумматора соединены г вы.холами рабочих блокг)в памяти и первого коммутатора.

Исключение из речультатов суммироваНИИ информации резериирусмого в данный момептб.лока памятп дг)стиглется путем ее двойного суммпроваьия (информация на сумматор подается по двум входам - непосредственно с рабочею блока памяти и с гзы.хола первого коммутатора). В этом

случае поразрядная сумма по модулю два двух одинаковых двоичных чисел равна «О, так как в каждом разряде чисел суммируется либо «О с «О, лпбо «1 с «I (О f О -- О, 1 -f 1 10, перенос отбрасывается и остается 0), при этом не имеет значения, правильная или неправильная информация поступает из рабочего блока памяти.

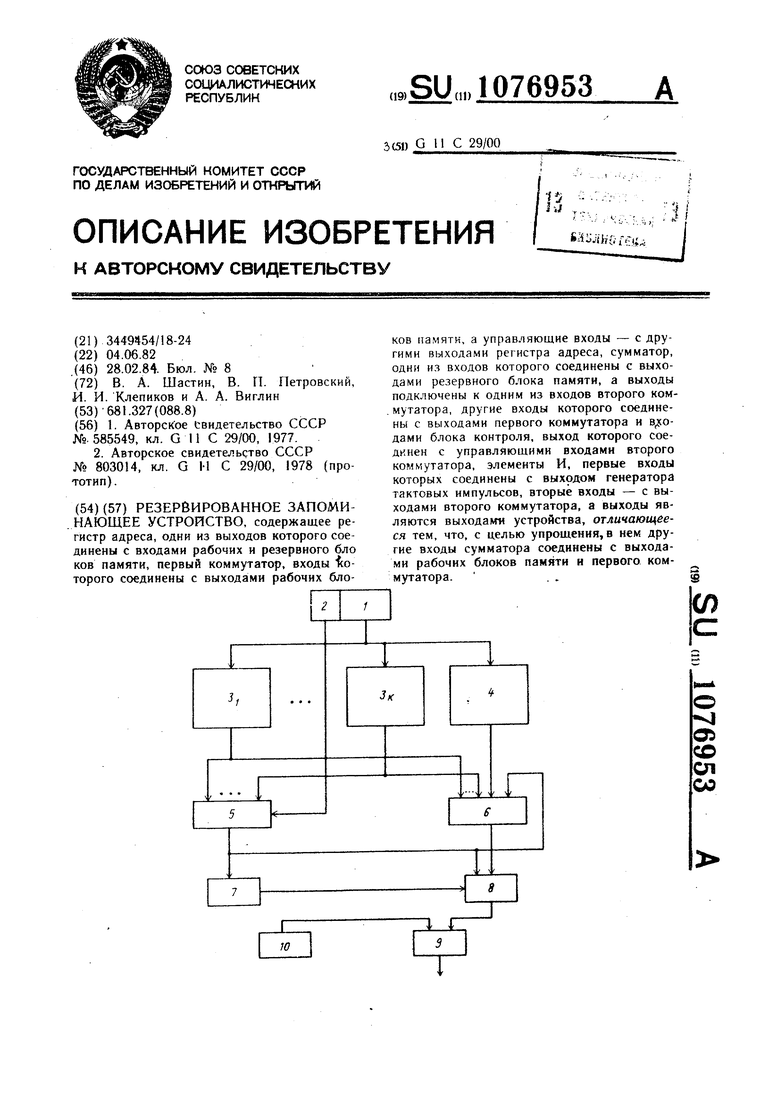

На чертеже приведена структурная схема резервированного запоминаюпгегс устройства.

0 Устройство содержит регистр 1 адреса, часть 2 из разрядов которого слу.жит для управления считыванием информации из одного из рабочих блоков 3...3 памяти, резервный блок 4 г1амяти, в который занесена сумма по модулю два информации

5 с одинаковыми адресами из рабочих блоков памяти, первый ко.ммутатор 5, предназначенный для передачи на выходы информации одного (выбранного) рабочего блока памяти, сумматор 6, предназначенный для формирования резервной информации из информации резервного блока 4 памяти и информации рабочих блоков 3...3 памяти, блок 7 контроля, например по модулю, второй коммутатор 8, предназначенный для выдачи на его выходы инфорг мации с выходов первого ко.ммутатора 5 или выходов сумматора 6, элементы И 9 (по числу разрядов выдаваемой информации), .предназначенные для выдачи на выходы устройства достоверной информации по тактовым импульсам генератора 0

актовых импульсов.

Тервый 5 и второй 8 коммутаторы выполнены, например, на коммутаторах со встроенной дешифрацией сигналов управления (на элементах 533КГ Н, 533КП13, 533П15 и т. д.). . Сумматор б выполнен,

например, на элементах 533ЛП5.

Блок 7 контроля выполнен на элементах контроля четности 133ИП2.

Устройство работает следующим образом.

Q Адрес ячейки, к которой необходимо обратиться, записывается я регистр I, в часть 2 разрь о.- которого заносится признак обращения к одном) из к ,: блоков 3,...3к памяти. Если обр.ященке iipd-. изводится к блоку 3j, го считанная из него

5 информация через первь1Й коммутатор 5 поступает на . входы 6j;oKa 7 f-онтроля, первые входы второго коммутатора 8, к + 2-е входы сумматора 6. Одяовре.мечно на к -f I входов сумматора 6 поступает информация, считанная по тому же адресу из соответствующих рабочих 3)...3„ и резервного 4 блоков памяти. Сумматор 6 реализует функцию поразрядного суммирования по шулулю два поданной на его (к-f 2) входов информации. При этом информация с выходов первого рабочего блока 3j памяти просуммируется два)(ды (по первым и к + 2-м входам сумматора 6). Так как поразрядная сумма по модулю два одинаковых двоичных чисел равна «О, то на выходы сумматора 6 поступит информация, равная поразрядной сумме по модулю два информации, считанной из всех блоков памяти, кроме первого. При этом при отсутствии неисправностей на вторые входы второго коммутатора 8 подаётся информация, равная информации, считанной из первого рабочего блока 3i памя/и (резервная информация). Если блоком 7 контроля не зарегистрировано искажение информации, поступающей с выходов .первого коммутатора 5, то блок 7 вырабатывает сигнал, разрешающий прохождение этой информации через второй коммутатор 8 на входы элементов И 9. Если результат контроля отрицательный, то на выходы второго коммутатора 8 поступает информация с выходов сумматора 6. На элементах И 9 по тактовым импульсам генератора 10 происходит выделение достоверной информации. Аналогично происходит считывание информации и из других рабочих блоков памяти. Предлагаемое техническое решение, по сравнению с прототипом, позволяет исключить из состава оборудования, общего для всех блоков памяти, коммутатор (используемый при формировании резервной информации) путем увеличения количества входов сумматора, что упрощает устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU983752A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1141454A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1354250A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИ. НАЮЩЕЕ УСТРОЙСТВО, содержащее регистр адреса, одни из выходов которого соединены с входами рабочих и резервного бло ков памяти, первый коммутатор, входы Которого соединены с выходами рабочих блоков памяти, а управляющие входы - с другими выходами регистра адреса, сумматор, одни из входов которого соединены с выходами резервного блока памяти, а выходы подключены к одним из входов второго ком. мутатора, другие входы которого соединены с выходами первого коммутатора и в одами блока контроля, выход которого соединен с управляющими входами второго коммутатора, элементы И, первые входы которых соединены с выходом генератора тактовых импульсов, вторые входы - с выходами второго коммутатора, а выходы являются выходами устройства, отличающееся тем, что, с целью упрощения, в нем другие входы сумматора соединены с выходами рабочих блоков памяти н первого коммутатора. . . S (Л

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-02-28—Публикация

1982-06-04—Подача