1

Изобретение относится к вычислительной технике и может быть исполь зёвано при построении запоминающих- устройств высоконадежных вычисли-- тельных систем.

23

Цель изобретения - повышение надежности устройства.

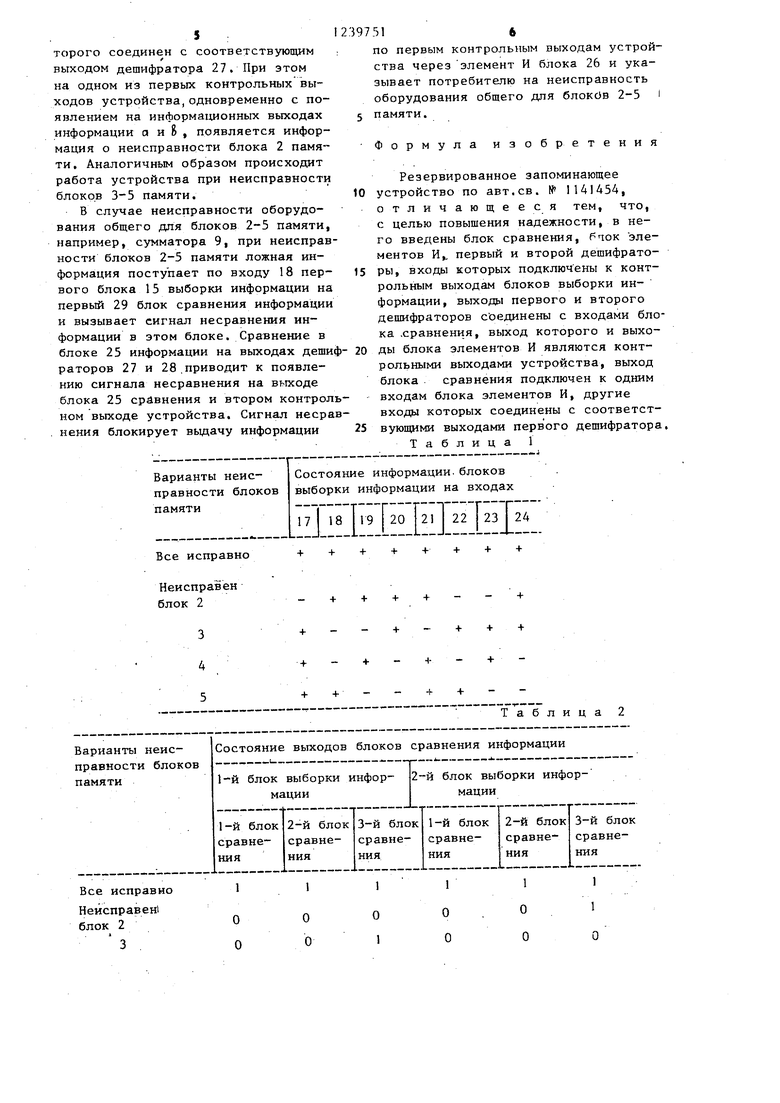

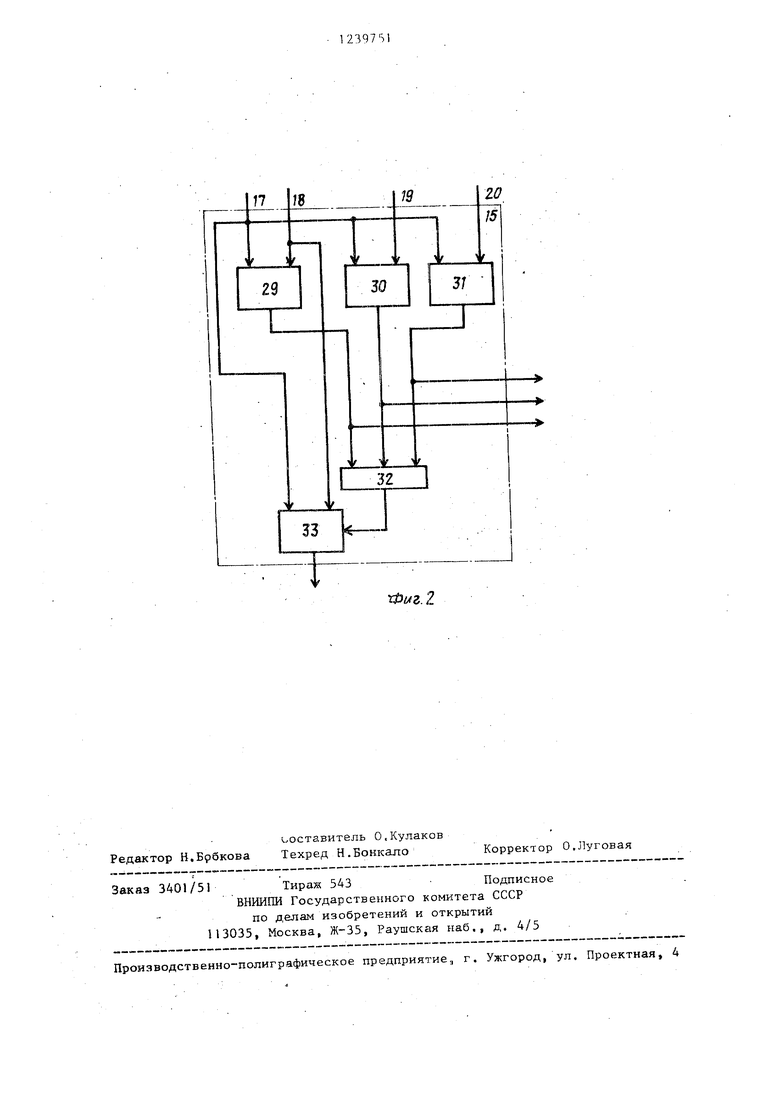

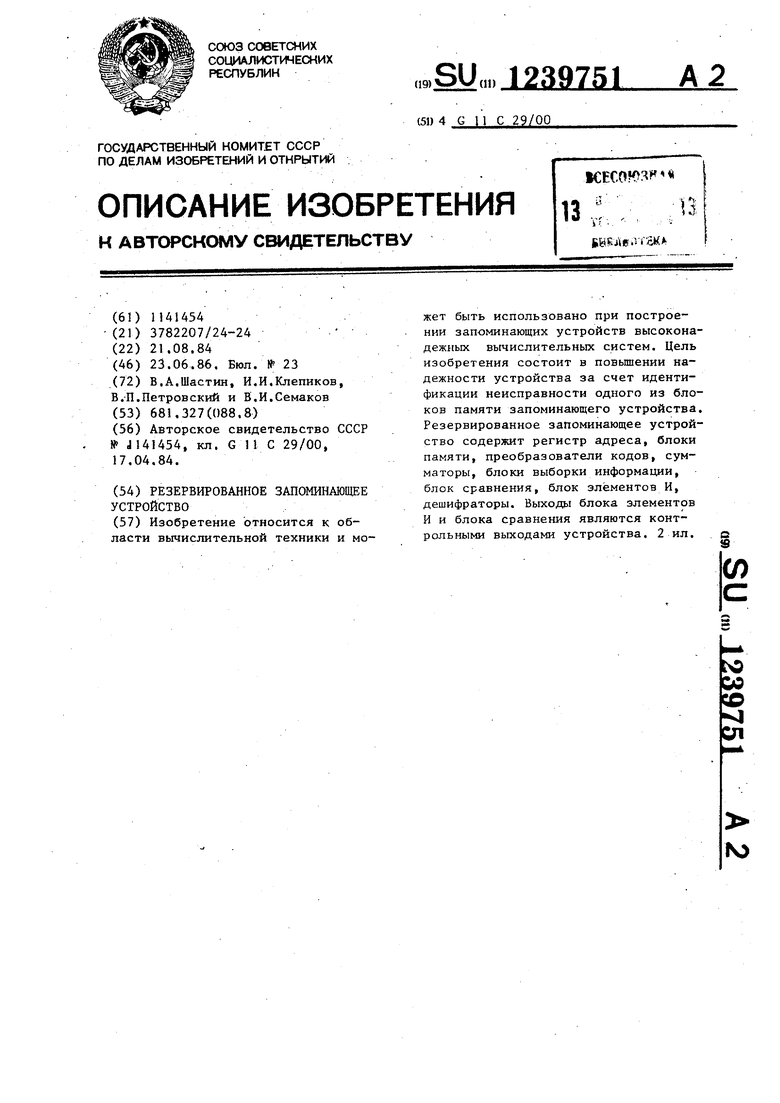

На фиг, 1 изображена функциональная схема устройства; на фиг, 2 - функциональная схема блока выборки информации.

Устройство содержит регистр 1 адреса, выходы которого соединены с адресными входами первого 2, второго 3 рабочих блоков памяти, первого резервного блока 4 памяти, в ячейки которого занесена информация, равная сумме кодов, содержащихся в одноименных ячейках первого 2 и второго 3 рабочих блоков памяти, второго резервного блока 5 памяти, в ячейки которого занесена информация, равная разности кодов, содержащихся в одноименных ячейках первого 2 и второго 3,рабочих блоков памяти, первый 6, второй 7, третий 8 преобразователи кода, первый 9, второй 10, третий 11, четвертый 12, пятый 13 и шестой 14 сумматоры, первый 15 и второй 16 блоки выборки информации с входами 17-24 соответственно, блок 25 сравнения, блок 26 элементов И, дешифраторы 27 и 28, входы которых соединены с контрольными выходами первого и второго блоков выборки ин- формации, а выходы - с соответствующими входами блока 25 сравнения. Выходы элементов И являются первыми Iконтрольными выходами устройства, ВЫХОД блока 25 сравнения является вторым контрольньм выходом устройства. Блоки 16 и 15 выборки информации (фиг, 2) содержат блоки «29-31 сравнения, выходы которых являются контрольными выходами блока выборки информации, элемент ИЛИ 32, входы которого соединены с соответствующими выходами блоков 29-31 сравнения информации, а выход соединен с управляющим входом коммутатора 33, первый информационный вход которого соединен с первыми входами блоков 29-31 сравнения информации и с первым входом 17 блока выборки информа10

го является информационным выходом блока выборки информации, третий 19 и четвертый 20 входы которого соеди нены соответственно с вторыми входа ми второго 30 и третьего 31 блокоь сравнения информации.

Разрядность каждого из рабочих блоков 2 и 3 памяти равна половине разрядности кодов хранимой в устрой стве информации. Разрядность каждого из резервных блоков 4 и 5 памяти на один разряд больше в связи с хра нением в первом резервном блоке 4 памяти суммы кодов и хранением во 15 втором резервном блоке 5 памяти раз ности кодов. Разрядность первого 6 и третьего 8 преобразователей кода равна разрядности рабочих блоков па , мяти, разрядность второго преобразо вателя 7 кода, разрядность сумматоров 9-14 равна разрядности резервного блока памяти. Разрядность блоков 29-31 сравнения информации, ком мутатора 33 равна разрядности рабочего блока памяти. Количество входов дешифраторов. 27 и 28 равно количеству блоков 29-31 сравнения в блоке выборки информации. Количеств выходов дешифраторов 27 и 28, разрядность блока 25 сравнения равно

20

25

30

35

40

45

50

2 , где N - количество входов дешиф раторов 27 и 28, Количество элементов И в блоке 26 равно количеству блоков 2-5 памяти в устройстве. Пре образователи 6-8 кода выполняют опе рацию инвертирования поступающей на них информации.

Устройство работает следующим об разом.

Адрес ячейки, к которой необходимо обратиться, записывается в регистр 1 адреса, По этому адресу про .исходит обращение к блокам 2-5 памя ти одновременно. Обозначают информацию, считываемую с первого рабочего блока 2 памяти, через а, с вто рого рабочего блока 3 - & не перво го резервного блока 4 -а +6, с второго 5 ;-а -&, Считанная информация поступает на сумматоры 9-14 через преобразователи 6-8 кода (выполняю- шие операцию инвертирования), На входах первого сумматора 9 имеют и , на входах второго сумматора

ции, второй вход 18 которого соединен 55 Ю -6 ист-о, на входах третьего с вторым входом блока 29 сравнения сумматора 11 -а-Б и а +&, на вхо- информации и с вторым информационным входом коммутатора 33, выход которо-,

дах четвертого сумматора 12 -а +Ь и -а, на входах пятого сумматора

10

39751I

го является информационным выходом блока выборки информации, третий 19 и четвертый 20 входы которого соединены соответственно с вторыми входами второго 30 и третьего 31 блокоь сравнения информации.

Разрядность каждого из рабочих блоков 2 и 3 памяти равна половине разрядности кодов хранимой в устройстве информации. Разрядность каждого из резервных блоков 4 и 5 памяти на один разряд больше в связи с хранением в первом резервном блоке 4 памяти суммы кодов и хранением во 15 втором резервном блоке 5 памяти разности кодов. Разрядность первого 6 и третьего 8 преобразователей кода равна разрядности рабочих блоков па- , мяти, разрядность второго преобразователя 7 кода, разрядность сумматоров 9-14 равна разрядности резервного блока памяти. Разрядность блоков 29-31 сравнения информации, коммутатора 33 равна разрядности рабочего блока памяти. Количество входов дешифраторов. 27 и 28 равно количеству блоков 29-31 сравнения в блоке выборки информации. Количество выходов дешифраторов 27 и 28, разрядность блока 25 сравнения равно

20

25

30

5

0

5

0

2 , где N - количество входов дешифраторов 27 и 28, Количество элементов И в блоке 26 равно количеству блоков 2-5 памяти в устройстве. Преобразователи 6-8 кода выполняют операцию инвертирования поступающей на них информации.

Устройство работает следующим образом.

Адрес ячейки, к которой необходимо обратиться, записывается в регистр 1 адреса, По этому адресу про- .исходит обращение к блокам 2-5 памяти одновременно. Обозначают информацию, считываемую с первого рабочего блока 2 памяти, через а, с второго рабочего блока 3 - & не первого резервного блока 4 -а +6, с второго 5 ;-а -&, Считанная информация поступает на сумматоры 9-14 через преобразователи 6-8 кода (выполняю- шие операцию инвертирования), На входах первого сумматора 9 имеют и , на входах второго сумматора

Ю -6 ист-о, на входах третьего сумматора 11 -а-Б и а +&, на вхо-

дах четвертого сумматора 12 -а +Ь и -а, на входах пятого сумматора

13- q и -(a-E), на входах шестого сумматора 14 -(а-Ь),и а+Ь. Таким образом, с выходов сумматоров 9-11 на входы 18-20 первого блока 15 выборки информации поступает информация а , а с выходов сумматоров 1214на входы 22-24 второго блока 16 выборки информации поступает информция Ь , причем с третьего 11 и шестого 14 сумматоров поступает информация с второго и последующих разрядо (исключается младший), т.е. деленна на два.

В случае сравнения информации, поступающей в первый блок 5 выборк информации по входу 17, с информацией по любому из других входов она считается достоверной и выдается через коммутатор 33 по управляющему сигналу с выхода элемента ИЛИ 32 на первый информационный выход устройства. В случае несравнения информации, поступающей по входу 17 первого блока 15 выборки информации, с информацией, поступающей по другим входам, с выхода элемента ИЛИ 32 на управляющий вход коммутатора 33 поступает сигнал, производящий переключение коммутатора 33. При этом на информационный выход устройства поступает восстановленная информация. Второй блок выборки информации работает параллельно с первым и на информационных выходах устройства одновременно появляется информация а и Ь .

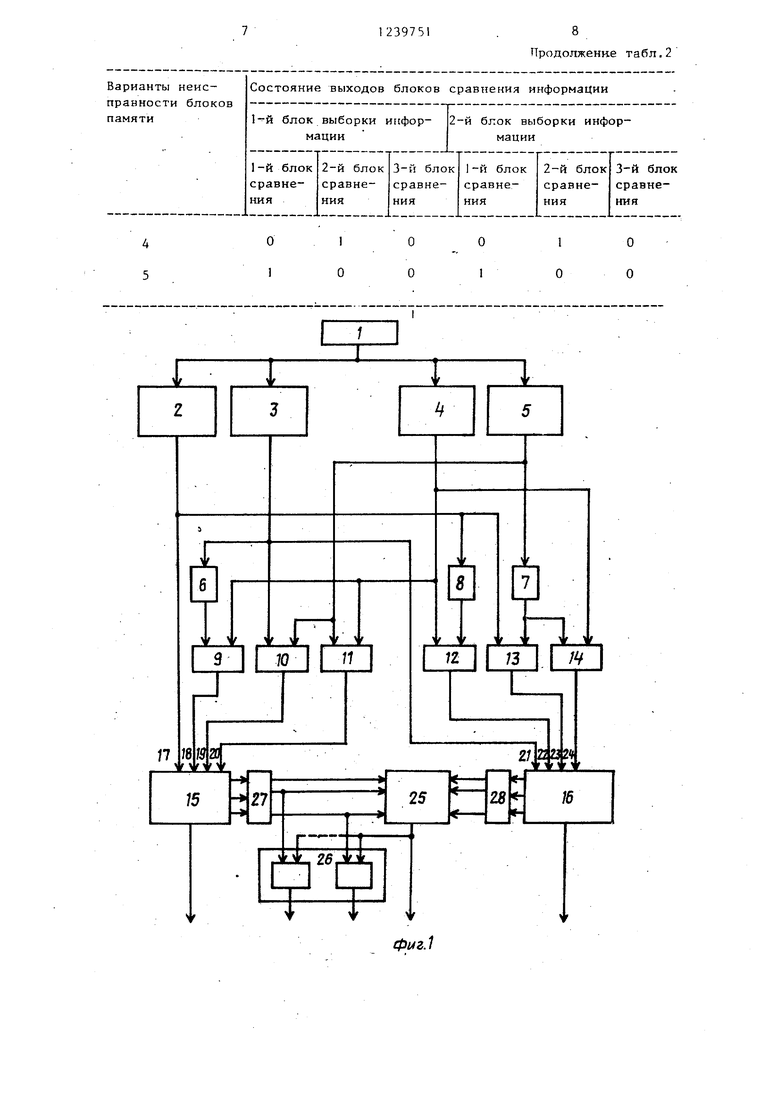

В табл. 1 отражено состояние информации, поступающей на входы блоков 15 и 16 выборки информации, для случаев нормальной работы устройства или неисправности одного из блоков памяти. Истинная информация обозначена знаком +, ложная - знаком (

Рассмотрим, например, случай неисправности блока 2 памяти. Считываемая из этого блока информация, поступающая на вход 17, ложная,инвертирование данной информации преобразователем 8 кода с последуюкщм суммированием с информацией d + 6 из исправного блока 4 памяти сумматора 12 приводит к поступлению на вход 22 блока 16 выборки информации ложной информации. Аналогично ложен результат суммирования сумматором 13| поступающий на вход 23 второго блока 16 выборки информации. Ложная инфор39751

мадия вызывает в первом .блоке 15 (фиг, 2) выборки информации несрав- нение в первом 29, втором 30 и третьем 31 блоках сравнения информа- J ции, а во втором блоке 16 выборки информации несравнение в первом и втором блоках сравнения.

Результаты сравнения информации, поступающей на входы 17-24 бло- 10 ков 15-и 16 выборки информации, блоками сравнения информации приведены в табл. 2, причем 1 соответствует сравнению информации, а О - несрав-. нению-.

J5 Из-табл, 2 следует, что неисправность одного из блоков 2-5 памяти вызывает установку выходов блоков сравнения в блоках 15 и 16 выборки информации в состояние, указывающее 20 на неисправность соответствующего блока памяти.

Дешифрация состояний контрольных выходов соответствующих блоков сравнения производится дешифраторами 25 27 и 28 независимо для каждого из блоков 15 и 16 выборки информации. Результат дешифрации выдается на соответствующие входы блока 25 сравнения.,

, Сравнение информации на соответствующих выходах дешифратора 27 первого блока 13 выборки информации с информацией на соответствуюш;их выхо- . дах дешифратора 28 второго блока 16 выборки информации в блоке 25 срав- нения позволяет при неисправности ЗУ с высокой степенью вероятности идентифицировать неисправность одного из блоков 2-5 памяти. Несравнение данной информации указывает на неисправность оборудования, общего для блоков 2-5 памяти (сумматоров, преобразователей кодов и др,).

Из табл. 2 следует, что при неисправности блока 2 памяти на входы дешифратора 27 поступит код 000, что приводит к появлению сигнала на одном из выходов дешифратора 27. На входы аналогичного дешифратора 28 второго блока 16 выборки информации поступает код 001 и устанавливается сигнал на соответствующем выходе этого дешифратора. Сравнение сигналов этих дешифраторов в блоке 25 срав- .нения приводит к появлению сигнала 5 сравнения на выходе блока 25 срав- нения, что влечет за собой появление сигнала на выходе соответствующего элемента IT блока 26, первый вход ко-.

0

торого соединен с соответствующим выходом дешифратора 27. При этом на одном из первых контрольных выходов устройства,одновременно с появлением на информационных выходах информации а и В , появляется информация о неисправности блока 2 памяти. Аналогичным образом происходит работа устройства при неисправности блоков 3-5 памяти.

В случае неисправности оборудования общего для блоков 2-5 памяти, например, сумматора 9, при неисправности блоков 2-5 памяти ложная информация поступает по входу 18 первого блока 15 выборки информации на первый 29 блок сравнения информации и вызывает сигнал несравнения информации в этом блоке. Сравнение в

блоке 25 информации на выходах дешиф- 20 ды блока элементов И являются контраторов 27 и 28.приводит к появлению сигнала несравнения на выходе блока 25 сравнения и втором контрольном выходе устройства. Сигнал несравнения блокирует выдачу информации

Состояние информации, блоков выборки информации на входах

17 I 18 1г9 I 20 |21 I 22 | 23 24

Все исправно

Неисправен блок 2

+ + + 4

Варианты неисСостояние выходов блоков сравнения информации

О О

о о

12397516

; ПО первым контрольным выходам устройства через элемент И блока 26 и указывает потребителю на неисправность

оборудования общего для блоков 2-5 i памяти.

Формула изобретения

Резервированное запоминающее устройство по авт.св. № 1141454, отличающееся тем, что, с целью повышения надежности, в него введены блок сравнения, Рчок элементов И,, первый и второй дешифрато- ры, входы которых подключ ены к контрольным выходам блоков выборки информации, выходы первого и второго дешифраторов соединены с входами блока .сравнения, выход которого и выхорольными выходами устройства, выход блока сравнения подключен к одним входам блока элементов И, другие входы которых соединены с соответст- вующлыя выходами перв ого дещифратора. Таблица 1

Таблица 2

1

о о

Редактор Н.Б9бкова

составитель О.Кулаков Техред Н.Боккало

Заказ 3401/51 Тираж 543 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

w3.2

Корректор О,Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1141454A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1510012A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1984 |

|

SU1234885A2 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ | 1990 |

|

RU2020566C1 |

| Многоканальное мажоритарно-резервированное запоминающее устройство | 1985 |

|

SU1317483A1 |

| Постоянное запоминающее устройство | 1989 |

|

SU1624527A2 |

Изобретеиие относится к области вычислительной техники и может быть использовано при построении запоминающих устройств высоконадежных вычислительных систем. Цель изобретения состоит в повьшении надежности устройства за счет идентификации неисправности одного из блоков памяти запоминающего устройства. Резервированное запоминающее устройство содержит регистр адреса, блоки памяти, преобразователи кодов, сумматоры, блоки выборки информации, блок сравнения, блок элементов И, дешифраторы. Выходы блока элементов И и блока сравнения являются контрольными выходами устройства. 2 ил. О «9 д :о СП

| Двутельная жаровня | 1959 |

|

SU141454A1 |

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1986-06-23—Публикация

1984-08-21—Подача