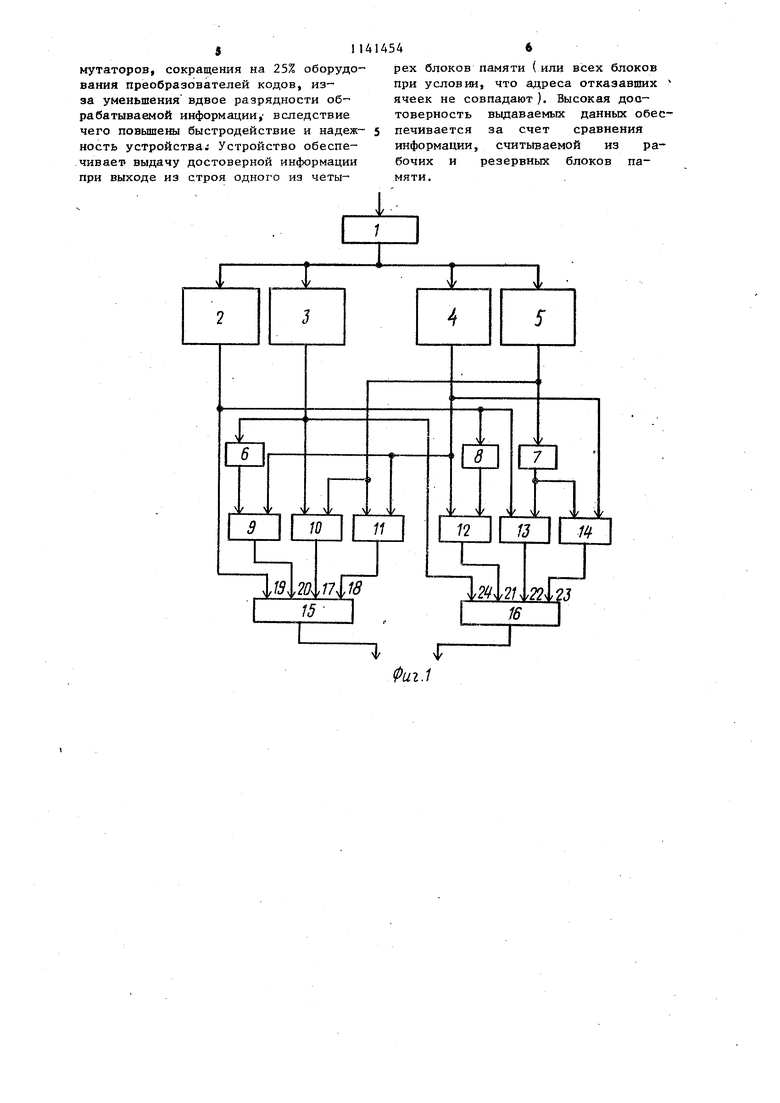

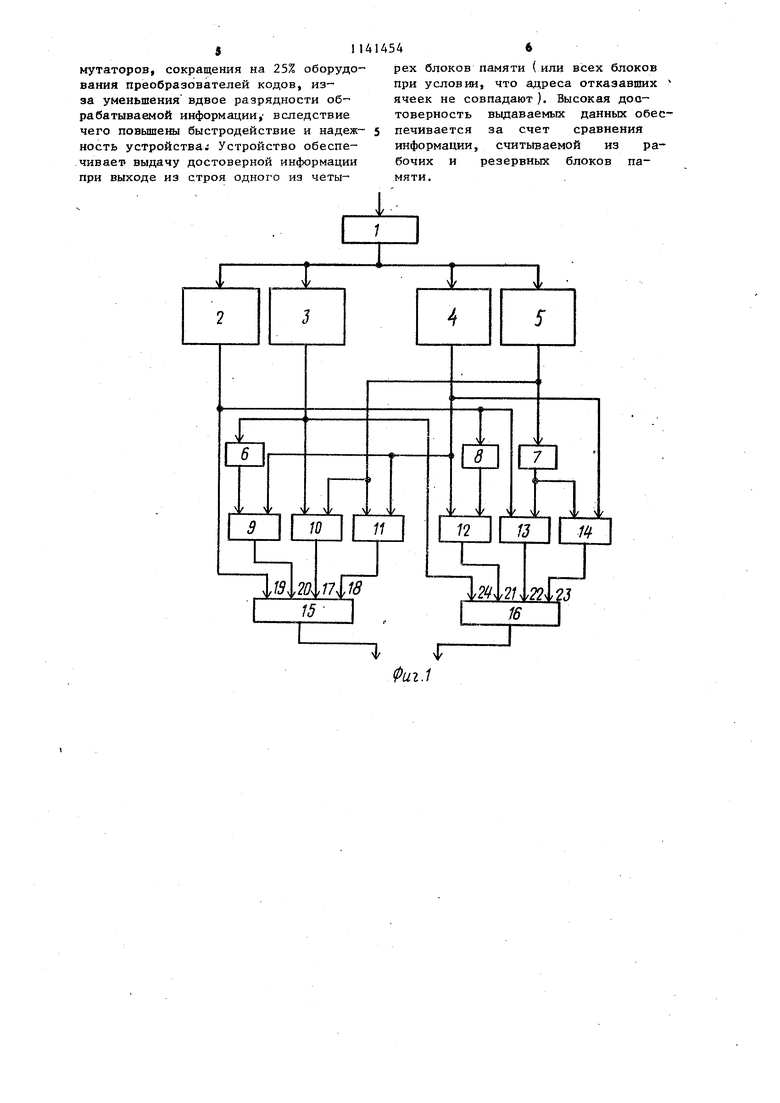

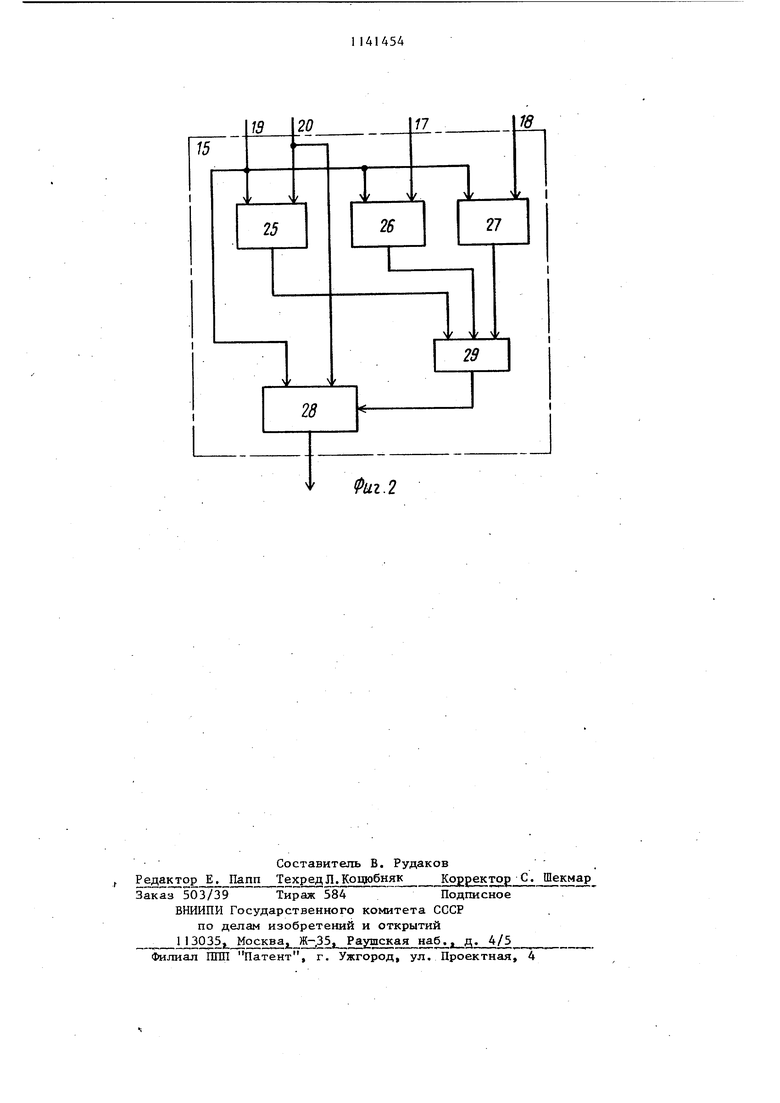

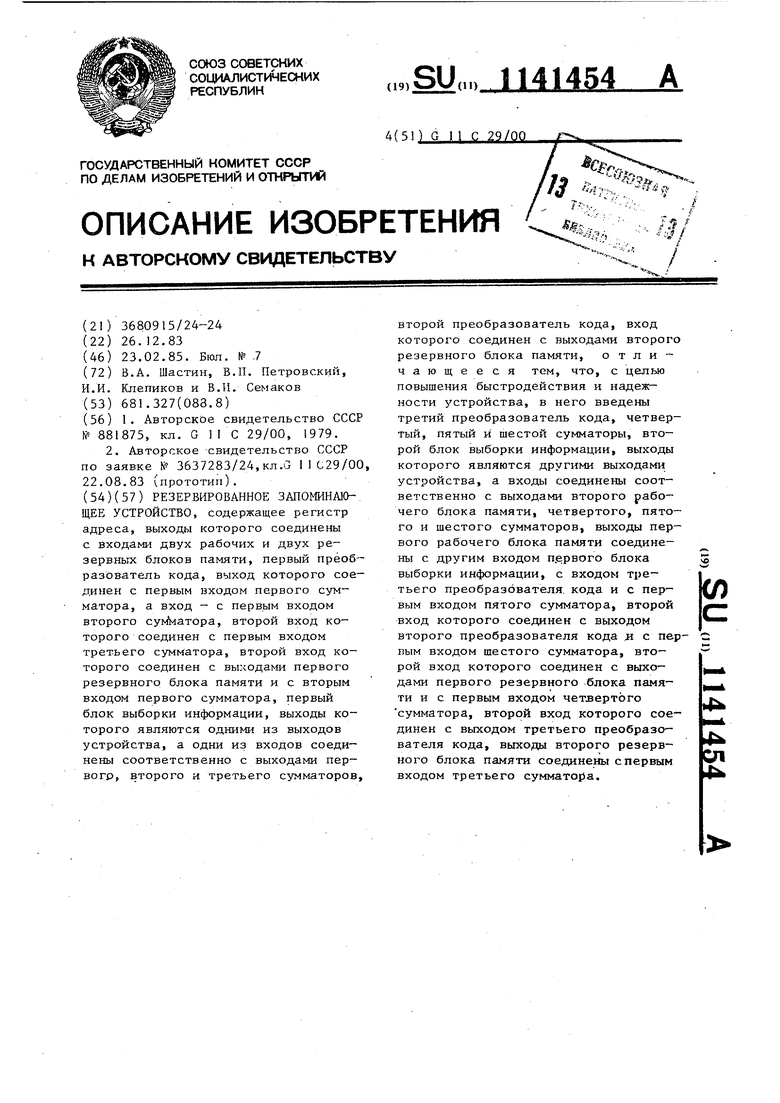

- Изобретение относится к вычислительной .технике и может быть использовгно при построении запоминающих устройств высоконадежных вычислительных систем. Известно устройство, содержащее регистр адреса, два рабочих и один резервный блок памяти, в который занесена сумма по модулю два .информаци с одинаковыми адресами из рабочих блоков памяти, коммутаторы, блок контроля по модулю, поразд)ядный сумматор, генератор тактовых импульсов, блок сравнения, группу элементов И fl Недостатком данного устройства яв ляется выдача потребителю недостоверной -информациипри неисправности: одного из рабочих блоков памяти (s случае необнаруженил неисправности блоком аппаратурного контроля по модулю) ,что снижает надежность устройства Наиболее близким техническим решением к изобретению является резервированное запоминающее устройство, содержащее регистр адреса, один из разрядов которого служит для занесения признака обращения к первому или второму рабочему блоку памяти, первы резервный блок памяти, в который занесена информация, равная сумме кодов, содержащихся в одноименных ячей ках первого и второго рабочих блоков памяти, второй резервный блок памяти в который занесена информация, равная разности кодов, содержащихся в одноименных ячейках первого и второго рабочих блоков памяти, первый, второй и третий коммутаторы, первый и второй преобразователи кодов, первый, второй и третий сумматоры, выходы которых являются соответственно вторыми, третьими и четвертыми . входами блока выборки информации, пе вые входы которого соединены с выходом первого коммутатора, а выходы являются выходами устройства (23. К недостаткам известного устройства следует отнести значительные аппаратурные затраты нареализацию коммутаторов и преобразователей кодо что приводит к снижению быстродейст- ВИЯ вследствие задержек сигналов при прохождении через коммутаторы и снижению надежности устройства. Цель изобретения - повышение быст родействия и надежности устройства. Поставленная цель достигается тем, что в резервированное запоминаю щее устройство, содержащее регистр адреса, выходы которого соединены с входами двух рабочих и двух резервных блоков памяти, первый преобразователь кода, выход которого соединен с первым входом первого сумматора, а вход - с первым входом второго сумматора, второй вход которого соединен с первым входом третьего сумматора, второй вход которого соединен с выхода- . ми первого резервного блока памяти и с вторым входом первого сумматора, первый блок выборки информации, выходы которого являются одними из выходов устройства, а одни из входов соединены соответственно с выходами первого, второго и третьего сумма.торов, второй преобразователь кода, вход которого соединен с выходами второго резервного блока памяти, введены третий преобразователь кода, четвертый,пятый и шестой сумматоры,второй блок выборки информации, выходы которого являются другими выходами устройства, а входа соединены соответсивенло с выходами второго рабочего блока памяти, четвертого, пятого и шестого сумматоров, выходы первого рабочего блока памяти соединены с другим входом первого блока выборки информации, с входом третьего преобразователя кода и с первым входом пятого сумматора, второй вход которого соединен с выходом второго преобразователя кода и с первым входом шестого сумматора, второй вход которого соединен с выходами первого резервного блока памяти и с первым входом четвертого сумматора, второй вход которого соединен с выходом третьего .преобразователя кода,выходы второго резервного блока памяти соединены с пер вым входом третьего сумматора. На фиг. и 2 изображены функциональные схемы предлагаемого устройства и блока выборки информации соответственно. Устройство (фиг, 1) содержит регистр 1 адреса, выходы которого соединены с адресными входами первого 2, второго 3 рабочих блоков памя- ТЛ; первого резервного блока 4 па- мяти, в ячейки которого занесена информация, равная сумме кодов, содержащихся с одноименных ячейках первого 2 и. второго 3 рабочих блоков памяти, второго резервного блока 5 памяти, в ячейках которого занесена информация, равная разности кодов, соаеожапшхся в одноименных ячейках первого 2 и второго 3 рабо- чих блоков памяти, первый 6, второй 7 и третий 8 преобразователи кода, (первый 9, второй 10, третий 11, четвертый 12, пятый 13 и шестой 14 сумматоры, первый 15 и второй 16 блоки выборки информации. Блок 15 имеет входы 17-20, блок 16 - входы 2124. Разрядность каждого из рабочих блоков 2 и 3 памяти равна половине разрядности кодов хранимой в устройстве информации. Разрядность каждого из резервных блоков 4 и 5 памяти на один разряд больше в связи с хранени ем в первом резервном блоке 4 памяти суммы кодов и хранением во втором ре зервном блоке 5 разности кодов. . Разрядность первого 6 и третьего 8 преобразователей кода равна разрядности рабочих блоков памяти, разрядность второго преобразователя 7, кода равна разрядности резервных блоков 4 и 5 памяти, равно как и разрядность всех сумматоров 9-14. Разрядность входов блоков 15 и 16 выборки информации равна разрядности рабочих блоков 4 и 5 памяти. Первый 15 и второй 16 блоки выбор ки информации аналогичны друг другу. Например, первый блок 15 выборки информации (фиг. 2 ) содержит блоки 25-27 сравнения, коммутатор 28, элемент ИЛИ 29., Устройство работает следующим об- разом.. Адрес ячейкиJ к которой необходим обратиться, записывается в регистр |1 адреса. По зтому адресу происходит обращение ко всем блокам 2-5 памяти одновременно. Обозначим информацию, считываемую с первого рабочего блока 2, буквой о, с второго рабочего блок 3- Ъ, с первого 4 резервного блока 4и+Ъ, с второго 5 - а-Ъ. Считанная информация поступает на сумматоры 9-14 через преобразователи 6 и 7 кода, выполняющие операцию инвертирова ния, и непосредственно на входах пер вого сумматора 9 имеем (-Ь)и а+Ъ, на входах второго сумматора 10 Ъ и а-fe, на входах третьего сумматора 11 а-Ь и d( + b, на входах четвертого сумматора 12 -о+Ь и f-dj, на входах пятого сумматора 13 -cs и C-Coi-b), на входах шестого сумматора 14 С-(о(-Ъ)и м+Ъ,с выходов первого сумматора 9 на вход 20 первого блока 15 выборки информации поступит ин- 1 4 формация, равная (« +b)+(-Ь) а. С выходов второго сумматора 10 на вход 17 первого блока 15 выборки информации поступит информация, равная Ь+ +(. На вход 18 первого блока 15 выборки информации с выходов третьего сумматора 11 поступит информация с второго и последующих разрядов, т.е. результат суммирования (d-)) (, деленный на два и равный а. На вход 19 первого блока 15 выборки информации поступает информация, .равная «, непосредственно с первого рабочего : блока 2 памяти. Таким образом, на все входы первого блока 15 выборки информации поступает информация, равная сх , С выходов четвертого сумматора 12 на вход 21 второго блока 16 выборки информации поступит информация, равная (о + t )+(-«) Ь. С выходов пятого сумматора 13 на вход 22 ,второго блока 16 выборки информации поступит информация, равная Л +f-( и т.д. Таким образом, на входы первого блока 15 выборки информации поступает информация м, на входы второго блока 16 выборки информации - информация Ь. Поскольку оба блока 15 и 16 работают одинаково, их работу рассмот. РИМ на примере первого блока I5 выборки информации, В случае сравнения информации,, поступающей в первый блок 15 выборки информации по входу.19, с информацией, поступающей по любому из других входов, она считается достоверной и выдается через коммутатор 28 по управляющему сигналу с выхода элемента ИЛИ 29 на выход устройства. В случае несравнения информации, поступающей по входу 19 первого блока 15 выборки инфо1Я4ации, с информацией, поступающей по другим входам, с выхода элемента ИЛИ 29 на управляющий вход коммутатора 28 поступает сигнал, производящий переключение коммутатора 28. При .этом на выходы устрой ства поступает восстановленная информация. Второй блок 16 выборки информации работает параллельно с первым 15, и на выходах устройств одновременно появляется информация и и Ъ. Таким образом, предлагаемое техническое решение позволяет сокра тить аппаратурные затраты на устрой- ство в целом за счет исключения ком- мутаторов, сокращения на 25% оборудования преобразователей кодов, изза уменьшения вдвое разрядности обрабатываемой информации, вследствие чего повышены быстродействие и надеж- ность устройства; Устройство обеспечивает выдачу достоверной информации при выходе из строя одного из четыП4 рех блоков памяти (или всех блоков при условии, что адреса отказавших ячеек не совпадают ). Высокая достоверность выдаваемых данных обеспечивается за счет сравнения информации, считьгеаемой из рабочих и резервных блоков памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1984 |

|

SU1239751A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1129658A1 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее регистр адреса, выходы которого соединены с входами двух рабочих и двух резервных блоков памяти, первый преобразователь кода, выход которого соединен с первым входом первого сумматора, а вход - с первым входом второго cyi-ftyiaTOpa, второй вход которого соединен с первым входом третьего сумматора, второй вход которого соединен с выходами первого резервного блока памяти и с вторым входом первого сумматора, первый блок выборки информации, выходы которого являются одними из выходов устройства, а одни из входов соединены соответственно с выходами пер- вогр, второго и третьего сумматоров. второй преобразователь кода, вход которого соединен с выходами второго резервного блока памяти, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, в него введены третий преобразователь кода, четвертый, пятый и шестой сумматоры, второй блок выборки информации, выходы которого являются другими выходами устройства, а входы соединены соответственно с выходами второго рабочего блока памяти, четвертого, пятого и шестого сумматоров, выходы первого рабочего блока памяти соединены с другим входом п.ервого блока выборки информации, с входом тре(Л тьего Преобразователя, кода и с первым входом пятого сумматора, второй вход которого соединен с выходом второго преобразователя кода JH с первым входом шестого сумматора, второй вход которого соединен с выходами первого резервного блока памяти и с первым входом четвертого сумматора, второй вход которого соединен с выходом третьего преобразо4; сд вателя кода, выходы второго резервного блока памяти соединены с первым входом третьего сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3637283/24,кл.й I 1 С29/00, 22.08.83 (прототип). | |||

Авторы

Даты

1985-02-23—Публикация

1983-12-26—Подача