(54) УСТРОЙСТВО ДЛЯ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропрограммногоупРАВлЕНия | 1979 |

|

SU809184A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство микропрограммногоупРАВлЕНия | 1979 |

|

SU811253A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления самого различного назначения, в частности, в устройствах управления со страничной организацией постоянных запоминающих, устройств .

Известно микропрограммное устройство для управления, использующее постоянное запоминакхчее устройство со страничной организацией, в котором различают команды передачи управления внутри страницы и команды межстраничной передачи управления 1

Однако это устройство характеризуется- значительным объемом оборудования.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство для управления, содержащее, первый и второй блоки постоянной памяти, счетчик гщреса, регистр -страниц, буферный регистр, блок формирования микрокоманд, элементы И, триггеры, блок ввода-вывода, коммутационное поле, причем гщресные входы регистра страниц и установочные входы счетчика адреса являются адресн лми входами устройства.

выходы младших разрядов регистра страниц соединены со входами адреса страниц первого и второго блоков постоянной памяти, выходы счетчика адреса соединены с адресными входами первого и второго блоков постоянной памяти, входы буферного регистра соединены с выходами регистра стра:ниц, а выходы - с адресными входами счет0чика адреса 2 .

Недостатком известного устройства является значительный расход оборудования при увеличении объема блока

5 постоянной памяти.

Цель изобретения - уменьшение объема оборудования при увеличении числа блоков постоянной патляти.

Поставленная цель достигается тем, что в устройстве счетный вход триг- гера переключения соединен с выходом блока формирования микроопераций, вход соединен с выходом старшего разряда буферного регистра, а выход соединен с установочным входом старшего разряда регистра страниц, выход стардего разряда регистра страниц соединен со входами страниц первого

и второго блоков постоянной памяти.

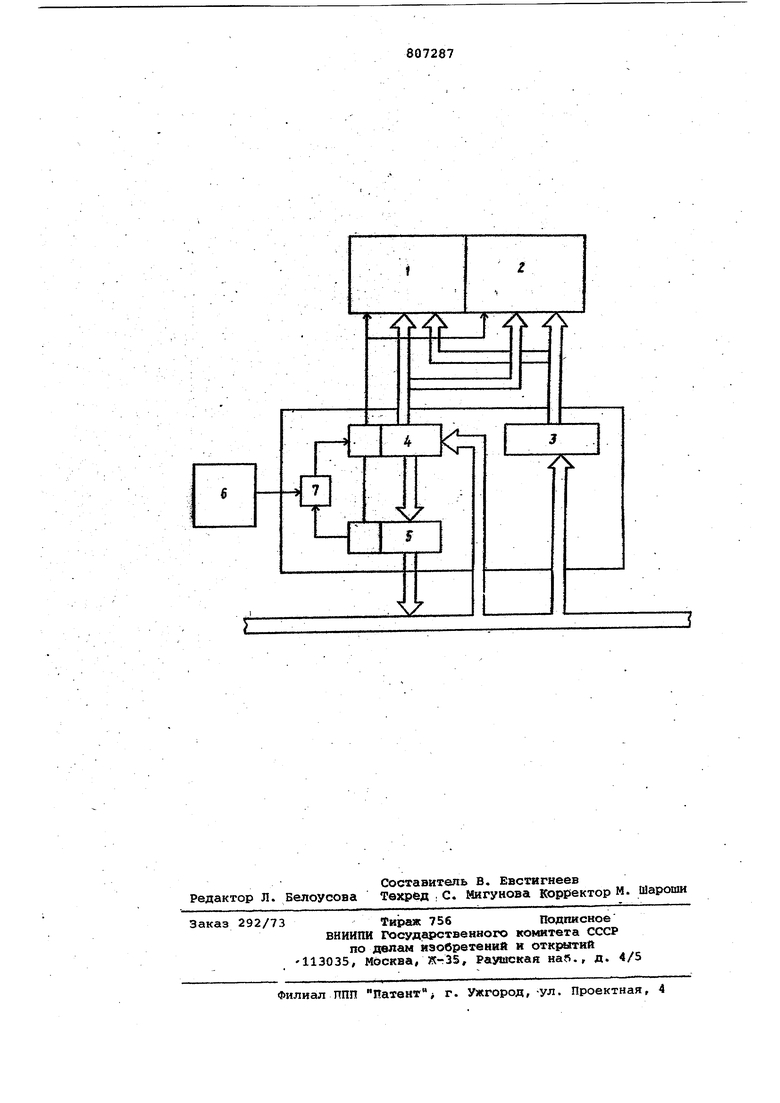

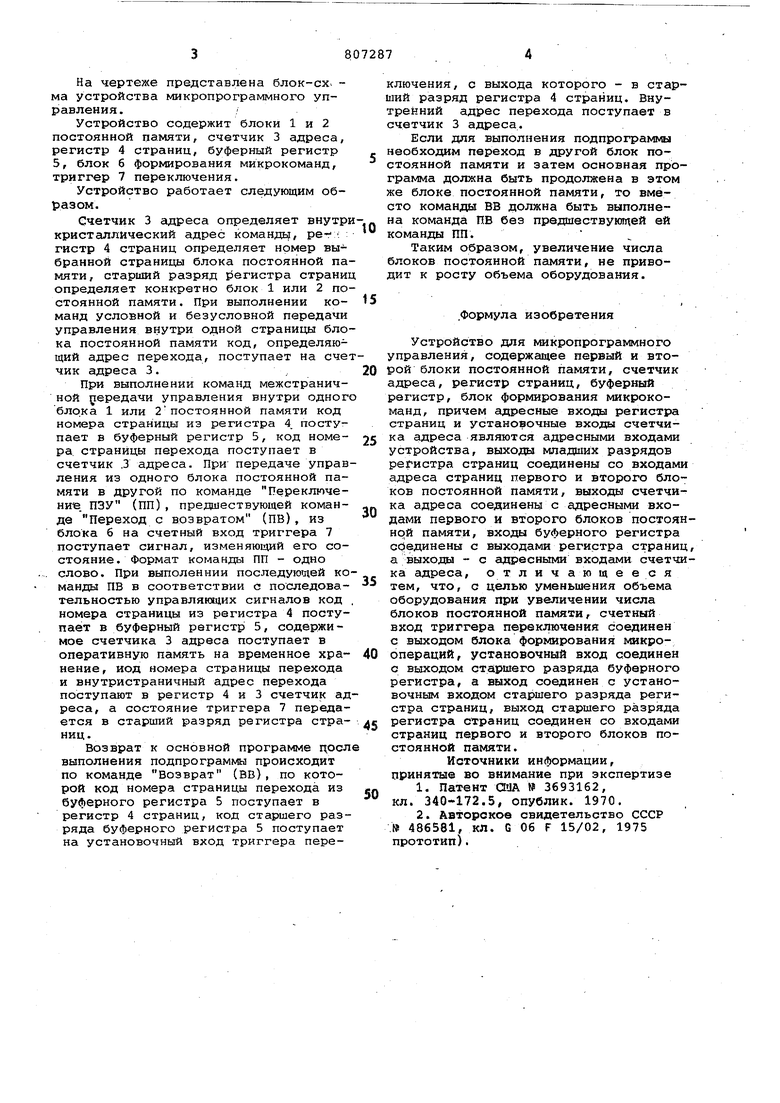

На чертеже представлена блок-сх- ма устройства микропрограммного управления.

Устройство содержит блоки 1 и 2 постоянной памяти, счетчик 3 адреса, регистр 4 страниц, буферный регистр 5, блок 6 формирования микрокоманд, триггер 7 переключения.

Устройство работает следующим образом.

Счетчик 3 адреса определяет внутркристаллический адрес командь, ре- : гистр 4 страниц определяет номер выбранной страницы блока постоянной памяти, старший разряд эегистра страни определяет конкретно блок 1 или 2 постоянной памяти. При выполнении команд условной и безусловной передачи управления внутри одной страницы блока постоянной памяти код, определяющий адрес перехода, поступает на счечик адреса 3.

При выполнении команд межстраничной передачи управления внутри одног блока 1 или 2постоянной памяти код номера страницы из регистра 4. поступает в буферный регистр 5, код номера, страницы перехода поступает в счетчик .3 адреса. При передаче управления из одного блока постоянной памяти в другой по команде Переключение ПЗУ (ПП), предшествующей команде Переход с возвратом (ПВ) , из блока б на счетный вход триггера 7 поступает сигнал, изменяющий его состояние . Формат команды ПП - одно слово. При выполеннии последующей команды ПВ в соответствии с последовательностью управляющих сигналов код номера страницы из регистра 4 поступает в буферный регистр 5, содержимое счетчика 3 адреса поступает в оперативную память на временное хранение, иод номера страницы перехода и внутристраничный адрес перехода поступают в регистр 4 и 3 счетчик адреса, а состояние триггера 7 передается в старший разряд регистра страниц.

Возврат к основной программе цосл выполнения подпрограммы происходит по команде Возврат (ВВ), по которой код номера страницы перехода из буферного регистра 5 поступает в регистр 4 страниц, код старшего разряда буферного регистра 5 поступает на установочный вход триггера переключения, с выхода которого - в старший разряд регистра 4 страниц. Внутренний адрес перехода поступает в счетчик 3 адреса.

Если для выполнения подпрограммы необходим переход в другой блок постоянной памяти и затем основная программа должна быть продолжена в этом же блоке постоянной памяти, то вместо команды ВВ должна быть выполнена команда ПВ без предшествующей ей команды ПП.

Таким образом, увеличение числа блоков постоянной памяти, не приводит к росту объема оборудования.

.Формула изобретения

Устройство для лшкропрограммного управления, содержащее первый и второй блоки постоянной памяти, счетчик адреса, регистр страниц, буферный регистр, блок формирования микрокоманд, причем адресные входы регистра страниц и установочные входы счетчика адреса являются адресными входами устройства, выходы младших разрядов регистра страниц соединены со входам адреса страниц первого и второго блоков постоянной памяти, выходы счетчика адреса соединены с адресными входами первого и второго блоков постояной памяти, входы буферного регистра соединены с выходами регистра страни а выходы - с адресными входами счетчка адреса, отличающееся тем, что, о целью уменьшения объема оборудования при увеличении числа блоков постоянной памяти, счетный вход триггера переключения соединен с выходом блока формирования юткроопараций, установочный вход соединен с выходом старшего разряда буферного регистра, а выход соединен с установочным входом старшего разряда регистра страниц, выход старшего разряда регистра ст раниц соединен со входами страниц первого и второго блоков постоянной памяти.

Источники информации, принятые во внимание при экспертизе

i

1

л л

I

4

7

7

Авторы

Даты

1981-02-23—Публикация

1978-02-08—Подача