(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Конвейерный аналого-цифровой преобразователь | 1986 |

|

SU1381706A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197078A1 |

Изобретение относится к вычислительной технике. Известен аналого-цифровой преобра зователь по методу сравнения и вычитания, содёжахций измерительные блок (каскады) по числу разрядов кода, ка дый из которых предназначен для опре деления значения цифры в соответствующем разряде кода путем сравнения преобразуемой аналоговой величины с эталонной величиной, размер которой пропорционален весу соответствунадего разряда кода, и выходы которых являются выходами аналого-цифрового преобразователя, с которых снимается кодовый результат аналого-цифрового преобразования ij. . HejfocTaTKOM устройства является сложность метрологического контроля Известен также аналого-цифровой преобразователь, содержащий измерительные блоки по числу разрядов кода, которые содержат cpaвнивaIk ий элемент, управлянмций выход которого соединен с управляющим входом вычитающего злемента, входы сравнивающего элемента и вычктакяцего элемента соединены с измерительной входной ши ной измерительного блока, выход вы}читакяцего элемента соединен с измерительной выходной шиной измерительного блока, выход сравнивакхдего элемента соединен с выходной шиной измерительного блока, а измерительная входная шина каждого измерительного блока соединена с измерительной выходной шиной каждого предыдущего излюрительного блока 2J. Недостатками устройства являются сложность метрологического контроля и ограниченные функциональные возможности устройства. Цель изобретения - упрощение метрологического контроля и расширение функциональньос возможностей. Указанная цель достигается тем, что в аналого-цифровой преобразователь , содержащий измерительные блоки, введено устройство для выделения кода погрешности преобразования, входные шины которого соединены с выхс5дными шинами измерительных блоков, а размеры эталонных величин в каждом измерительном блоке соответственно выбраны пропорциональными либо соответствующим р-числам Фибоначчи, либо соответствуккцим степеням золотой

р-пропорции, являющейся положительным корнем уравне.ния

Pt4

- X - 1 О,

X

где р-задэнное натуральное число; устройство для выделения кода погреш ности преобразования при содержит функциональные блоки, каждый из которых Соответствует определенному разряду кода, за исключением двух старших разрядов, -и из которых содержит первый элемен И, входы которого соединены соответственно с +3-й и входными шинами, элемент ИЛИ, первый вход которого соединен с выходом первого элемента И,второй элемент И, первый вход которого соединен с выходом элемента ИЛИ, а второй вход которого соединен с .fe-й входной шиной, второй вход элемента ИЛИ -.-го функционального бло Ъоединен с выходом элемента ИЛИ +1-го функционального блока; устройство для вьаделения кода погрешности преобразования при содержит первый элемент ИЛИ, выход которого является контрольным выходом устройства для выделения кода погрешности преобразования, и функциональные блоки, каддый из которых соответствует определенному разряду кода, за исключением трех старших разрядов, -т из которых содержит первый элемент И, входы которого соединены соответственно с . н-З-й и входной шинами, второй элемент И, входы которого соединены соответственно с -и+3-й и f+2-й входной шинами, а выход которого соединен с соответствующим входом первого элемента ИЛИ, второй элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, третий элемент И, первый которогоссоединен с выходом второго элемента ИЛИ, а второй вход которого: соединен с входной шиной и выход которого является -fc-м информационным выходом устройства даш выделения кода погрешности преобразования, причем третий вход второго элемента ИЛИ функционального блока соединен с выходом второго элемента ИЛИ +i-ro функци9 яального блока. Устройство для ввделения кода погрешности преобразования при р 3 содержит первый элемент ИЛИ, выход которого является контрольным выходом устройства для выделения кода погрешности преобразования, и функциональные блоки, каждый из которых соответствует определенному разряду кода, за исключением р+1 старших разрядов, из которых содержит первый элемент И, входы которого соединены соответственно с - + р+1-й и + 1-й входной шинами,

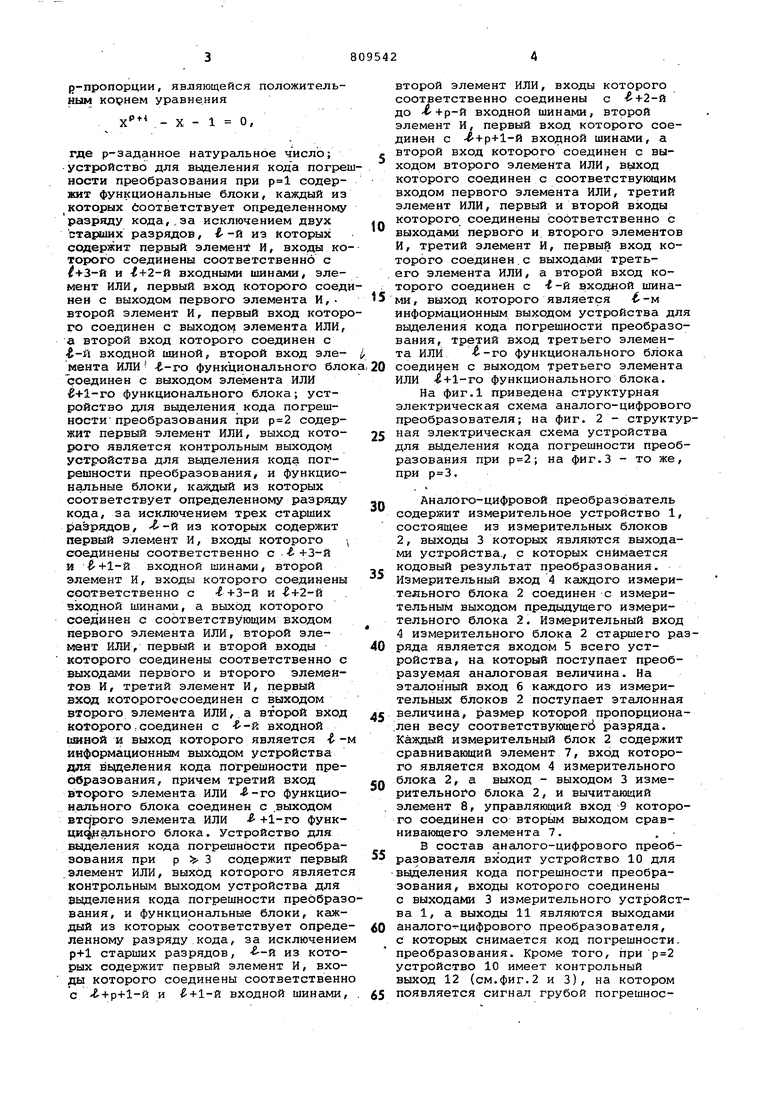

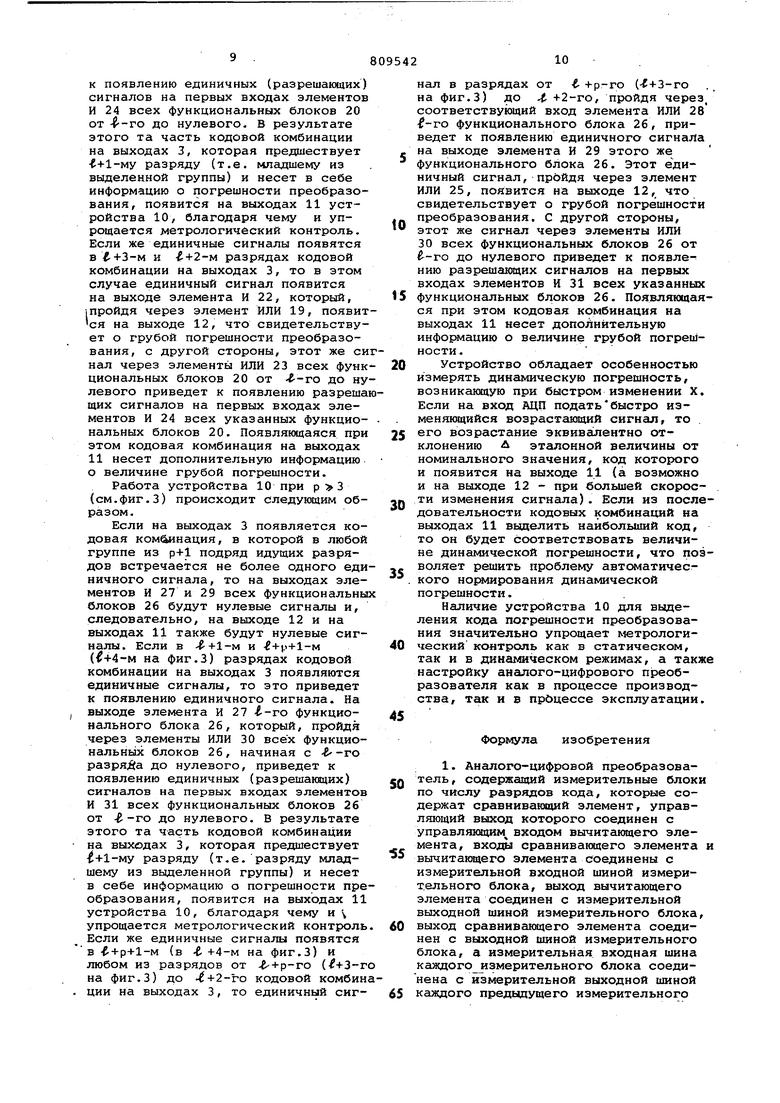

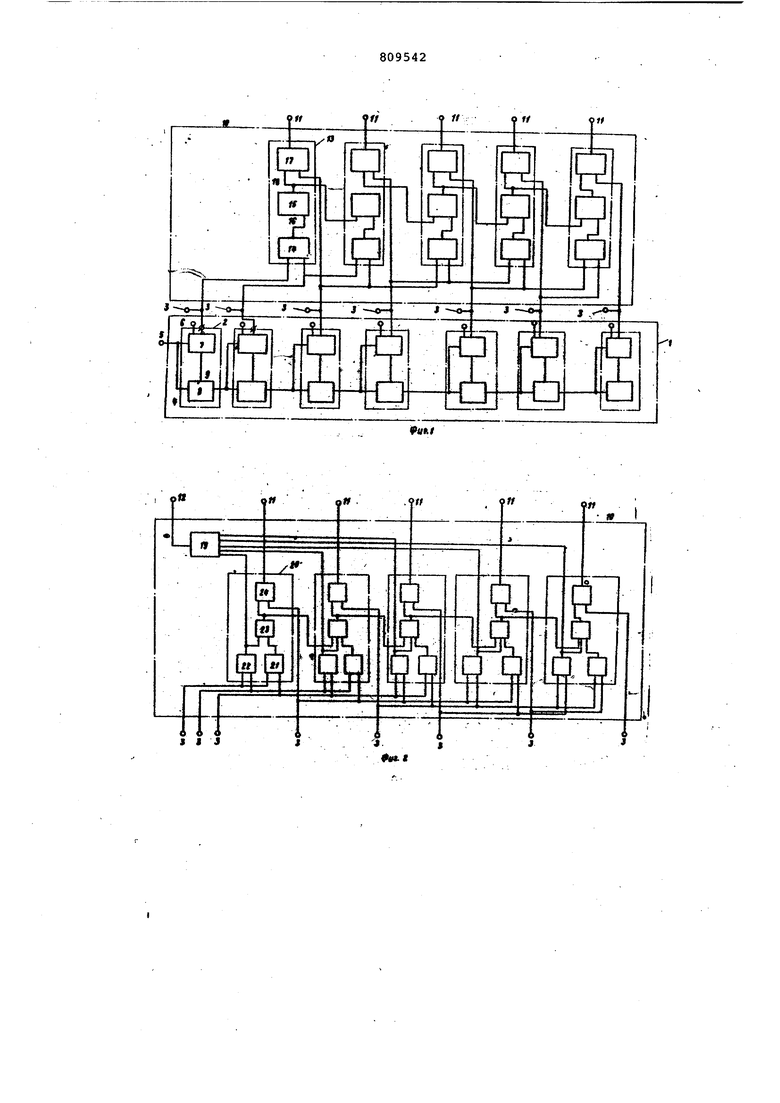

второй элемент ИЛИ, входы которого соответственно соединены с до t+p-й входной шинами, второй элемент И, первый вход которого соединен с - +р+1-й входной шинами, а второй вход которого соединен с выходом второго элемента ИЛИ, выход которого соединен с соответствующим входом первого элемента ИЛИ, третий элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и. второго элементов И, третий элемент И, первый вход которого соединен.с выходами третьего элемента ИЛИ, а второй вход которого соединен с - -и входной шинами , выход которого является t -м информационным выходом устройства дл выделения кода погрешности преобразования, третий вход третьего элемента ИЛИ функционального блока соединен с выходом третьего элемента ИЛИ +1-го функционального блока. На фиг.1 приведена структурная электрическая схема аналого-цифровог преобразователя; на фиг. 2 - структуная электрическая схема устройства для выделения кода погрешности преобразования при на фиг.З - то же, при .

Аналоххэ-цифровой преобразователь содержит измерительное устройство 1, состоящее из измерительных блоков 2, выходы 3 которых являются выходами устройства., с которых снимается кодовый результат преобразования, измерительный вход 4 каждого измерительного блока 2 соединен с измерительным выходом предыдущего измерительного блока 2. Измерительный вход 4 измерительного блока 2 старшего раряда является входом 5 всего устройства, на который поступает преобразуемая аналоговая величина. На эталонный вход 6 каждого из измерительных блоков 2 поступает эталонная величина, размер которой пропорциона лен весу соответствукадегб разряда. Каждый измерительный блок 2 содержит сравнивающий элемент 7, вход которого является входом 4 измерительного блока 2, а выход - выходом 3 измерительно1 о блока 2, и вычитающий элемент 8, управляющий вход 9 которого соединен со вторым выходом сравнивающего элемента 7..

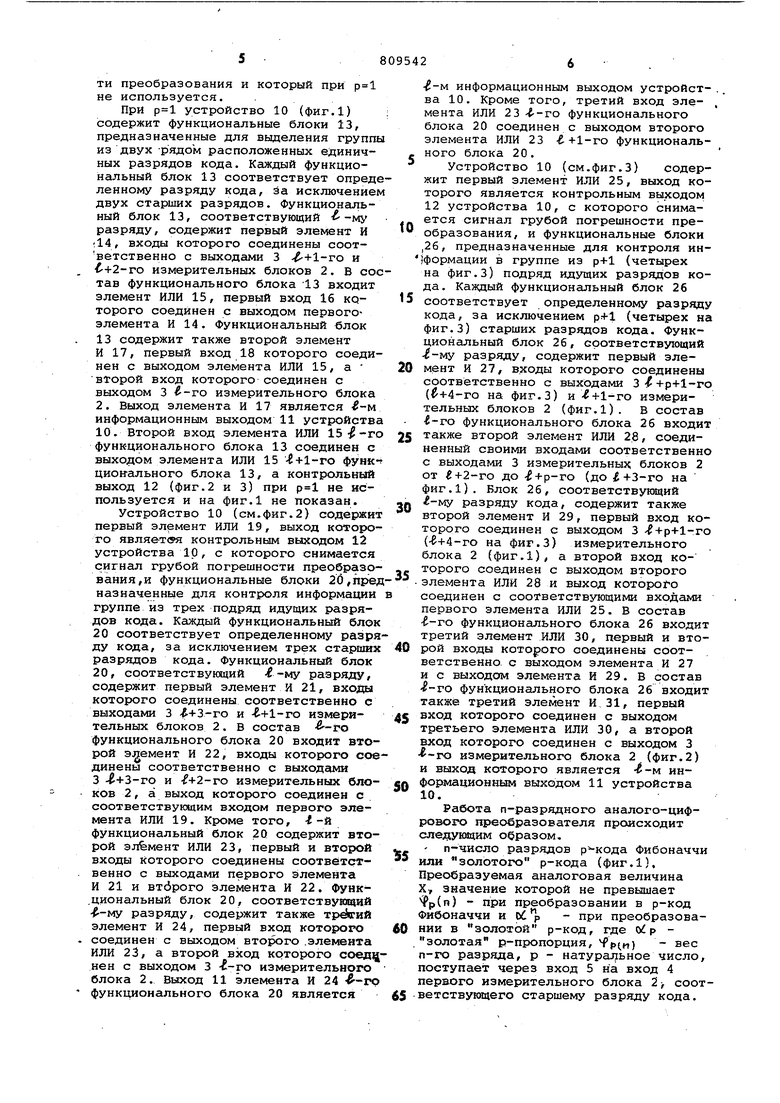

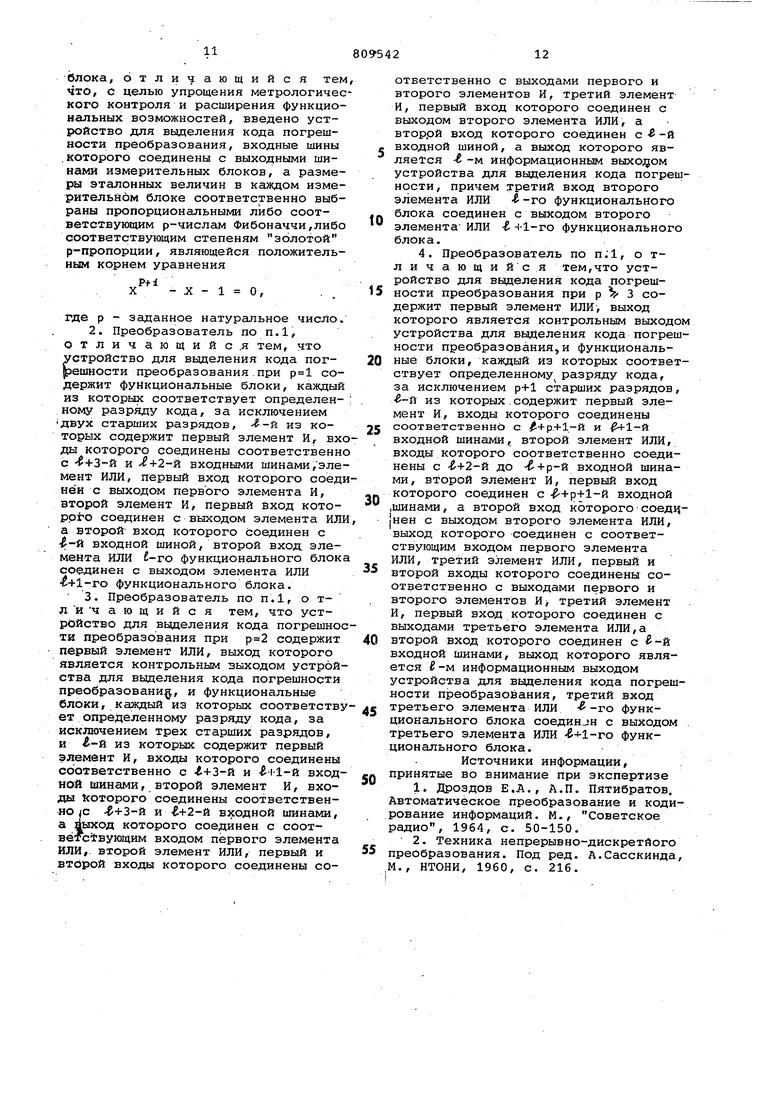

В состав аналого-цифрового преобразователя входит устройство 10 для вьаделения кода погрешности преобразования, входы которого соединены с выходами 3 измерительного устройства 1, а выходы 11 являются выходами аналого- цифрового преобразователя, с которых снимается код погрешности, преобразования. Кроме того, при устройство 10 имеет контрольный выход 12 (см.фиг.2 и 3), на котором появляется сигнал грубой погрешности преобразования и который при не используется.

При устройство 10 (фИГ.1)

содержит функциональные блоки 13, предназначенные для выделения группы из двух -рядом расположенных единичных разрядов кода. Каждый функциональный блок 13 соответствует определенному разряду кода, за исключением двух старших разрядов. Функциональный блок 13, соответствующий -f--му разряду, содержит первый элемент И 14, входы которого соединены соответственно с выходами 3 +1-го и 1-+2-ГО измерительных блоков 2. В состав функционального блока 13 входит элемент ИЛИ 15, первый вход 16 которого соединен с выходом первогоэлемента И 14. Функциональный блок 13 содержит также второй элемент И 17, первый вход 18 которого соединен с выходом элемента ИЛИ 15, а второй вход которого соединен с выходом 3 -го измерительного блока 2. Выход элемента И 17 является -м информационным выходом 11 устройства 10. Второй вход элемента ИЛИ функционального блока 13 соединен с выходом элемента ИЛИ 15 - +1-го функ-т цион-ального блока 13, а контрольный выход 12 (фиг.2 и 3) при не используется и на фиг.1 не показан.

Устройство 10 (см.фиг.2) содержит первый элемент ИЛИ 19, выход которого являетв я контрольным выходом 12 устройства 10, с которого снимается сигнал грубой погрешности преобразования,и функциональные блоки 20,предназначенные для контроля информации группе из трех подряд идущих разрядов кода. Каждый функциональный блок 20 соответствует определенному разряду кода, за исключением трех старших разрядов кода. Функциональный блок 20, соответствующий разряду, содержит первый элемент и 21, входа которого соединены соответственно с выходами 3 4+3-го и -С +1-го измерительных блоков 2. в состав -го функционального блока 20 входит второй элемент и 22, входы которого соединены соответственно с выходами 3 - +3-го и +2-го измерительных блоков 2, а выход которого соединен с соответствующим входом первого элемента ИЛИ 19. Кроме того, -и функциональный блок 20 содержит второй элемент ИЛИ 23, первый и второй входы которого соединены соответственно с выходами первого элемента И 21 и втброго элемента И 22. Функ.циональный блок 20, соответствующий разряду, содержит также элемент И 24, первый вход которого соединен с выходом второго .элемента. ИЛИ 23, а второй вход которого coeflijнен с выходом 3 -t-ro измерительного блока 2. Выход 11 элемента И 24 S-ro функционального блока 20 является

информационным выходом устройст- .. ва 10. Кроме того, третий вход эле- , мента ИЛИ 23 -t-ro функционального блока 20 соединен с выходом второго элемента ИЛИ 23 +1-го функционального блока 20.

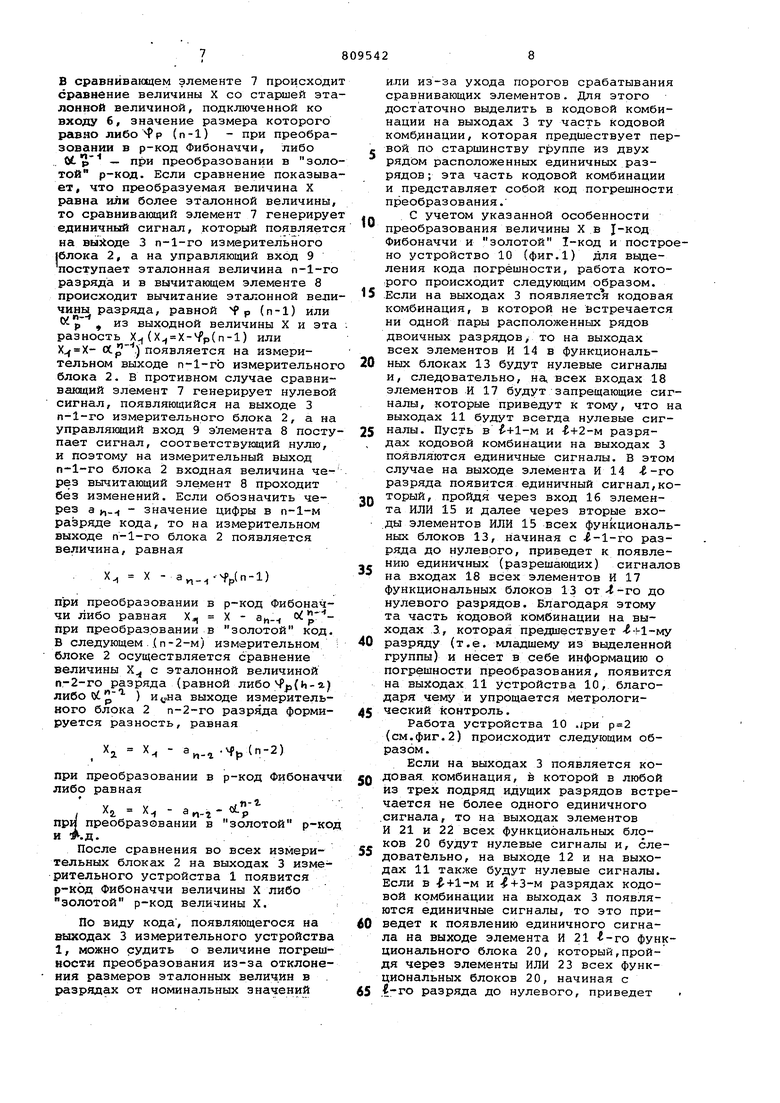

Устройство 10 (см.фиг.3) содержит первый элемент ИЛИ 25, выход которого является контрольным выходом 12 устройства 10, с которого снимается сигнал грубой погрешности преoобразования, и функциональные блоки ,26, предназначенные для контроля ин|формации в группе из р+1 (четырех на фиг.З) подряд идущих разрядов кода. Каждый функциональный блок 26

5 соответствует определенному разряду кода, за исключением р4-1 (четырех на фиг.З) старших разрядов кода. Функциональный блок 26, соответствующий разряду, содержит первый эле0мент И 27, входы которого соединены соответственно с выходами 3 / +р+1-го (+4-го на фиг.З) и - H-l-ro измерительных блоков 2 (фиг.1). В состав i-ro функционального блока 26 входит также второй элемент ИЛИ 28, соеди5ненный своими входами соответственно с выходами 3 измерительных блоков 2 от +2-го до +р-го (до f+3-ГО на фиг.1). Блок 26, соответствующий -му разряду кода, содержит также

0 второй элемент И 29, первый вход которого соединен с выходом 3 - +р+1-го (4+4-го на фиг.З) измерительного блока 2 (фиг.1), а второй вход которого соединен с выходом второго

5 элемента ИЛИ 28 и выход KOTOpoi o соединен с соответствующими входами первого элемента ИЛИ 25. В состав -f-ro функционального блока 26 входит третий элемент ИЛИ 30, первый и вто0рой входы которого соединены соответственно, с выходом элемента И 27 и с выходом элемента И 29. В состав функционального блока 26 входит также третий элемент И,31, первый вход которого соединен с выходом

S третьего элемента ИЛИ 30, а второй вход которого соединен с выходом 3 измерительного блока 2 (фиг.2) и выход которого является (-м информационным выходом 11 устройства

O 10.

Работа п-разрядного аналого-цифрового преобразователя происходит следующим образом,

п-число разрядов Фибоначчи

5 или золотого р-кода (фиг.1), Преобразуемая аналоговая величина X, значение которой не превышает NPp(n) - при преобразовании в р-код Фибоначчи и Od р - при преобразова0нии в золотой р-код, где Oi р золотая р-пропорция, ff(H) вес п-го разряда, р - натурал ьное число, поступает через вход 5 на вход 4 первого измерительного блока 2 соот5ветствующего старшему разряду кода.

В сравнивающем элементе 7 происходит сравнение величины X со старшей эталонной величиной, подключенной ко входу б, значение размера которого равно либо Ч р (п-1) - при преобразовании в р-код Фибоначчи, либо Ot р - при преобразовании в золотой р-код. Если сравнение показывает, что преобразуемая величина X равна или более эталонной величины, то срайнивающий элемент 7 генерирует единичный сигнал, который появляется на выз4оде 3 п-1-го измерительного (блока 2, а на управляющий вход 9 поступает эталонная величина п-1-го разряда и в вычитающем элементе 8 происходит вычитание эталонной величины разряда, равной S р (п-1) или Oip из выходной величины X и эта разность Х, (Х (п-1) или Лр) появляется на измерительном выходе п-1-го измерительного блока 2. В противном случае сравнивагаций элемент 7 генерирует нулевой сигнал, появляющийся на выходе 3 п-1-го измерительного блока 2, а на управлякадий вход 9 злемента 8 поступает сигнал, соответствукядий нулю, и поэтому на измерительный выход п-1-го блока 2 входная величина через вычитающий элемент 8 проходит без изменений. Если обозначить через а л - значение цифры в п-1-м разряде кода, то на измерительном выходе п-1-го блока 2 появляется величина, равная

Х X - (n-l) при преобразовании в р-код Фибонач ичи либо равная Х X - а.

при преобразовании в золотой код. В следующем . .(п-2-м) измерительном блоке 2 осуществляется сравнение величины Х с эталонной величиной П-2-ГО разряда (равной либоЧр{Ь-г) либообр ) Иуна выходе измерительного блока 2 П-2-ГО разряда формируется разность, равная

.4f,(n-2)

- а

п-г

при преобразовании в р-код Фибоначчи либо равная

Xj. Х - a.j - oLp

при преобразовании в золотой р-код и р-.д.

После сравнения во всех измерительных блоках 2 на выходах 3 измерительного устройства 1 появится р-код Фибоначчи величины X либо золотой р-код величины X.

По виду кода , появляющегося на выходах 3 измерительного устройства 1, можно судить о величине погрешности преобразования из-за отклонения размеров эталонных величин в разрядах от номинальных значений

или из-за ухода порогов срабатывания сравнивающих элементов. Для этого достаточно выделить в кодовой комбинации на выходах 3 ту часть кодовой комбд1нации, которая предшествует первой по старшинству группе из двух рядом расположенных единичных разрядов ; эта часть кодовой комбинации и представляет собой код погрешности преобразования.

С учетом указанной особенности преобразования величины X в 1-код Фибоначчи и золотой 1-код и построно устройство 10 (фиг.1) для выделения кода погрешности, работа которого происходит следующим образом. .Если на выходах 3 появляется кодовая комбинация, в которой не встречается ни одной пары расположенных рядов двоичных разрядов, то на выходах всех элементов И 14 в функциональных блоках 13 будут нулевые сигналы и, следовательно, на, всех входах 18 элементов И 17 будут запрещающие сигналы, которые приведут к тому, что н выходах 11 будут всегда нулевые сигналы. Пусть в -t+l-M и t+2-M разрядах кодовой комбинации на выходах 3 появляются единичные сигналы. В этом случае на выходе элемента И 14 -{-го разряда появится единичный сигнал,который, пройдя через вход 16 элемента ИЛИ 15 и далее через вторые входы элементов ИЛИ 15 всех функциональных блоков 13, начиная с -1-го разряда до нулевого, приведет к появлению единичных (разрешающих) сигнало на входах 18 всех элементов И 17 функциональных блоков 13 от -t -го до нулевого разрядов. Благодаря этому та часть кодовой комбинации на выходах 3, которая предшествует - -н1-му разряду (т.е. младшему из выделенной группы) и несет в себе информацию о погрешности преобразования, появится на выходах 11 устройства 10, благодаря чему и упрощается метрологический контроль.

Работа устройства 10 лри (см.фиг.2) происходит следующим образом.

Если на выходах 3 появляется кодовая комбинация, в которой в любой из трех подряд идущих разрядов встречается не более одного единичного .сигнала, то на выходах элементов И 21 и 22 всех функциональных блоков 20 будут нулевые сигналы и, следовательно, на выходе 12 и на выходах 11 также будут нулевые сигналы. Если в и i+3-м разрядах кодовой комбинации на выходах 3 появляются единичные сигналы, то это приведет к появлению единичного сигнала на выходе элемента И 21 -8-го функционального блока 20, который,пройдя через элементы ИЛИ 23 всех функциональных блоков 20, начиная с Е-го разряда до нулевого, приведет

к появлению единичных (разрешающих) сигналов на первых входах элементов И 24 всех функциональных блоков 20 от 4--ГО до нулевого. В результате этого та часть кодовой комбинации на выходах 3, которая предшествует С+1-му разряду (т.е. младшему из выделенной группы) и несет в себе информацию о погрешности преобразования, появится на выходах 11 устройства 10, благодаря чему и упрощается метрологический контроль. Если же единичные сигналы появятся и +2-м разрядах кодовой комбинации на выходах 3, то в этом случае единичный сигнал появится на выходе элемента И 22, который, Пройдя через элемент ИЛИ 19, появится на выходе 12, что свидетельствует о грубой погрешности преобразования, с другой стороны, этот же сигнал через элементы ИЛИ 23 всех функциональных блоков 20 от -t-TQ до нулевого приведет к появлению разрешающих сигналов на первых входах элементов И 24 всех указанных функцио- нальных блоков 20. Появляющаяся при этом кодовая комбинация на выходах 11 несет дополнительную информацию о величине грубой погрешности.

Работа устройства 10 при (см.фиг.З) происходит следующим образом.

Если на выходах 3 появляется коовая комбинация, в которой в любой группе из р+1 подряд идущих разряов встречается не более одного единичного сигнала, то на выходах элементов И 27 и 29 всех функциональных блоков 26 будут нулевые сигналы и, следовательно, на выходе 12 и на выходах 11 также будут нулевые сигналы. Если в и + 1.1 + 1-М

(+4-м на фиг.З) разрядах кодовой комбинации на выходах 3 появляются единичные сигналы, то это приведет к появлению единичного сигнала. На выходе элемента И 27 t-ro функционального блока 26, который, пройдя через элементы ИЛИ 30 всех функциональнь1х блоков 26, начиная с разряда до нулевого, приведет к появлению единичных (разрешающих) сигналов на первых входах элементов И 31 всех функциональных блоков 26 от до нулевого. В результате этого та часть кодовой комбинации на выходах 3, которая предшествует +1-му разряду (т.е. разряду младшему из выделенной группы) и несет в себе информацию о погрешности преобразования, появится на выходах 11 устройства 10, благодаря чему и упрощается метрологический контрол ь. Если же единичные сигналы появятся в -t+p+l-M (в -t+4-М на фиг.З) и любом из разрядов от -t + p-ro (+3-го на фиг.З) до +2-го кодовой комбинации на выходах 3, то единичный сигнал в разрядах от t- +р-го (- + 3-го на фиг.З) до 4 +2-го, пройдя через соответствукадий вход элемента ИЛИ 28 t-ro функционального блока 26, приведет к появлению единичного сигнала на выходе элемента И 29 этого же функционального блока 26. Этот единичный сигнал, прбйдя через элемент ИЛИ 25, появится на выходе 12, что свидетельствует о грубой погрешности преобразования. С другой стороны, этот же сигнал через элементы ИЛИ 30 всех функциональных блоков 26 от -го до нулевого приведет к появлению разрешающих сигналов на первых входах элементов И 31 всех указанных функциональных блоков 26. Появляющаяся при этом кодовая комбинация на выходах 11 несет дополнительную информацию о величине грубой погрешности.

Устройство обладает особенностью измерять диншническую погрешность, возникающую при быстром изменении X. Если на вход АЦП податьбыстро изменянлцийся возрастающий сигнал, то его возрастание эквивалентно отклонению & эталонной величины от номинального значения, код которого и появится на выходе 11 (а возможно и на выходе 12 - при большей скорости изменения сигнала). Если из последовательности кодовых комбинаций на выходах 11 вьщелить наибольший код, то он будет соответствовать величине динамической погрешности, что позволяет решить проблему автоматического нормирования динамической погрешности.

Наличие устройства 10 для вьаделения кода погрешности преобразования зн;ачительно упрощает метрологический контроль как в статическом, так и в динакшческом режимах, а такж настройку аналого-цифрового преобразователя как в процессе производства, так и в процессе эксплуатации.

Формула изобретения

блока, отличающийся тем что, с целью упрощения метрологического контроля и расширения функциональных возможностей, введено устройство для выделения кода погрешности преобразования, входные шины .которого соединены с выходными шинами измерительных блоков, а размеры эталонных величин в каждом измерительйом блоке соответственно выбраны пропорциональными либо соответствующим р-числам Фибоначчи,либо соответствующим степеням золотой р-пропорции, являющейся положительным корнем уравнения

V V 1 - П

X -л-1 0, ,

где р - заданное натуральное число.

Источники информации, принятые во внимание при экспертизе

.М., НТОНИ, I960, с. 216. -Р r-l1 I I I- 3

Авторы

Даты

1981-02-28—Публикация

1977-05-16—Подача