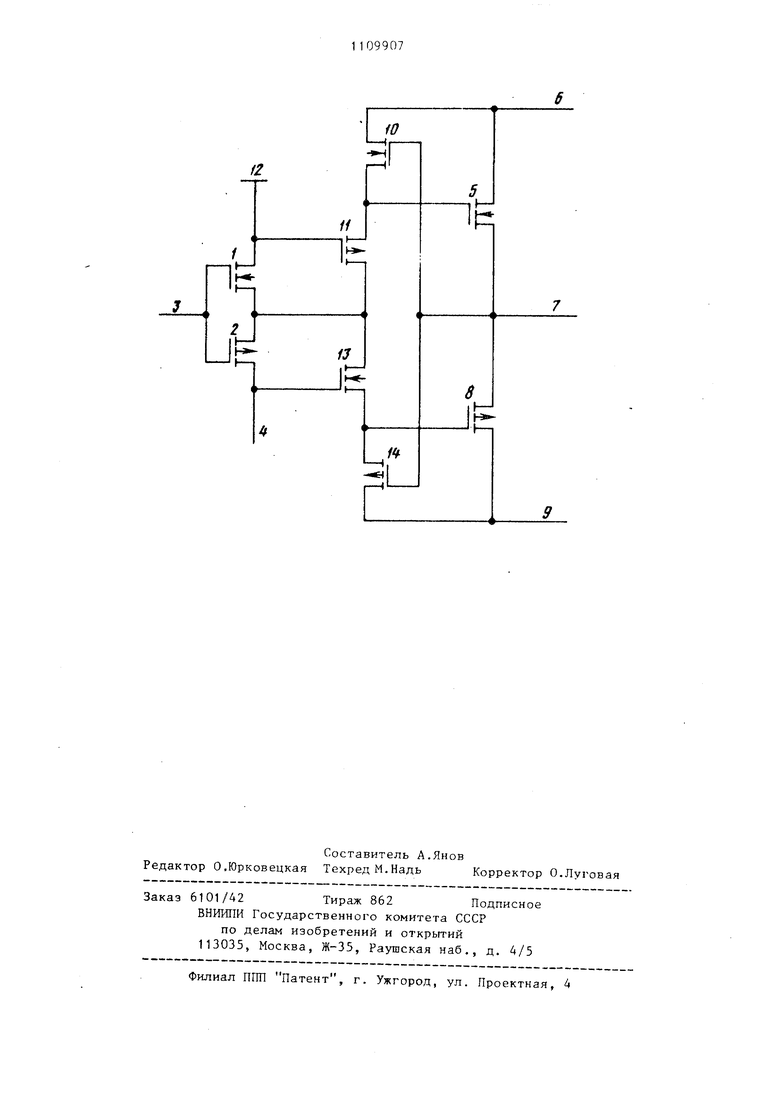

Изобретение относится к электронике и импульсной технике и предназначено для преобразования уровней напряженьл. Известно устройство преобразования уровней напряжения, выполненн на дополняющих ВДП-транзисторах и содержащее входной транзистор, первый инвертор и триггер с несимметричными плечами 1 1 Недостатком устройства является невозможность использования его для преобразования уровней ТТЛ ИС в управляющие напряжения МДП-схем на дополняющих транзисторах, питающихс от разнополярных источников напряже ния, так как при логическом О на входе устройства не обеспечивается режим закрывания п-канальных транзи торов, подключенных истоком к шине источника отрицательного напряжения питания. Наиболее близким по технической сущности к предложенному является устройство согл-асования ТТЛ схем с МДП-интегральньми схемами, выполненное на МДП-транзисторах, содержащее первый транзистор с каналом гл-типа сток которого подключен к стоку второго транзистора с каналом р -типа, затвор которого подключен к входУ устройства, а исток- к щине первого источника положительного.напряжения третий транзистор с каналом п-типа,ис ток которого подключен к шине отрица тельного источника напряжения, сток к выходу устройства и стоку четверто транзистора с каналом р-типа, исток которого подключен к шине второго источника положительного напряжения исток пятого транзистора с каналом h-типа подключен к шине отрицательного источника напряжения, затвор шестого транзистора с каналом р-типа к шине нулевого потенциала, сток к стоку седьмого транзистора с каналом п-типа, затвор восьмого транзистора с каналом р-типа подключен к выходу устройства, сток - к затвору четвертого транзистора, а исток к шине второго источника положительного напряжения, сток девятого транзистора подключен к затвору второго транзистора и истоку шестого транзистора, затвор третьего транзистора подключен к стоку первого транзистора и затвору седьмого транзистора исток которого подключен к шине отрицательного источника напряжения, сток седьмого транзистора подключен к затворам первого и пятого Tpai зисторов . Недостатком известного устройства является низкое быстродействие, связанное с ограничивающими ток первым, третьим и пятым тоанзисторами. Цель изобретения - увеличение быстродействия. Поставленная цель достигается тем, что в устройстве преобразования уровней напряжения, выполненном на МДЛ-транзисторах, содержащем первый транзистор с каналом ti -типа, сток которого подключен к стоку второго транзистора с каналом р-типа, затвор которого подключен к входу устройства, а исток - к, шине первого источника положительного напряжения, третий транзистор с каналом п-типа, исток которого подключен к шине отрица ельного источника напряжения, сток - к выходу устройства и стоку четвертого транзистора с каналом р-типа, исток которого подключен к шине второго источника положительного напряжения, исток пятого транзистора с каналом м -типа подключен к шине отрицательного источника напряжения, затвор шестого транзистора с каналом р-типа подключен к шинр нулевого потенциала, сток - к стоку седьмого транзистора с каналом h-типа, затвор восьмого транзистора с каналом р-типа подключен к выходу устройства, сток - к затвору четвертого транзистора, а исток - к шине второго источника положительного напряжения, затвор первого транзистора подключен к входу устройства, исток - к шине нулевого потенциала, сток - к стоку седьмого транзистора, затвор которого подключен к истоку второго транзистора, а исток - к стоку восьмого транзистора, затвор которого подключен к затвору пятого транзистора, сток которого подключен к истоку шестого транзистора и затвору третьего транзистора. На чертеже представлена принципиальная электрическая схема устройства преобразования уровней напряжения. Устройство содержит первый транзистор 1 с каналом п-типа, сток которого подключен к стоюу второго транзистора 2 с каналом р-типа, затвор которого подключен к входу 3 устройства, а исток - к шине первог источника 4 положительного напряжения, третий транзистор 5 с каналом п-типа, исток которого подключен к шине отрицательного источника 6 напряжения, сток - к выходу 7 устро ства и стоку четвертого транзистора 8, исток которого подключен к шине второго источника 9 положительного напряжения, исток пятого транзистора 10 с каналом п-типа подключен к шине отрицательного источника 6 напряжения, затвор шестого транзистора 1 1 с каналом р-типа - к шине 12 нулевого потенциала, сток - к стоку седьмого транзистора 13 с каналом h-типа, затвор восьмого транзистора 14 с каналом р-типа подключен к Bi-rx ду 7 устройства, сток - к затвору четвертого транзистора 8, а исток к шине второго источника 9 положительного напряжения, затвор первого транзистора 1 подключен к входу 3 устройства, исток - к шине 12 нулево потенциала, сток - к стоку седьмого транзистора 13, затвор которого подключен к истоку второго транзистора 2, а исток - к стоку восьмого транзистора 14, затвор которого подключе к затвору пятого транзистора 10, сток которого подключен к истоку шестого транзистора 11 и затвору тре тьего транзистора 5. Устройство работает следующим образом. Пусть в исходном состоянии уровен напряжения на входе 3 устройства соответствует логическому О. При этом первый транзистор 1 закрыт, а второй транзистор 2 открыт. На стоках первого и второго транзисторов 1 и 2 устанавливается значение напряжения, близкое к напряжению на шине первого источника А положительного напряжения. Через открытый шестой транзистор 11 положительное напряжение прикладывается к затвору третьего транзистора 5, который открывается под действием суммы напряжения отрицательного и первого положительного источников. На выходе 7 устройства устанавливается напряжение, близкое к напряжению на шине отрицательного источника 6 напряже ния. По мере нарастания отрицательного напряжения на вькоде 7 устройства пятый транзистор 10 закрывается, а восьмой транзистор Ii открывается. При этом положительные напряжения в узлах на стоке пятого транзистора 10 и восьмого транзистора 14 увеличиваются, обеспечивая тем самым открывание третьего транзистора 5 и закрывание четвертого транзистора 8, Этот процесс протекает лавинообразно до тех пор, пока напряжение на вькоде 7 устройства не установится близким к напряжению на шине отрицательного источника 6 напряжения. При поступлении на вход 3 устройства логической 1 на стоках первого и второго транзисторов 1 и 2 через открытый первый транзистор 1 устанавливается напряжение, близкое к нулевому значению. Через открытый седьмой транзистор 13 это напряжение прикладывается к затвору четвертого транзистора 8, который открывается под действием суммы напряжений, приложенных между затвором и истоком. На выходе 7 устройства устанавливается напряжение, близкое к напряжению второго источника 9 положительного напряжения. По мере нарастания положительного напряжения на выходе 7 устройства пятый транзистор 10 открывается, а восьмой транзистор 14 закрывается. При этом отрицательное напряжение на стоке пятого транзистора 10 увеличивается, обеспечивая закрывание третьего транзистора 5. Технико-экономический эффект изобретения заключается в увеличении быстродействия устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Дешифратор для запоминающего устройства | 1981 |

|

SU980160A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Дешифратор адреса | 1981 |

|

SU966905A1 |

| Формирователь импульсов для блоков памяти | 1985 |

|

SU1278973A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ УРОВНЕЙ НАПРЯЖЕНИЯ, выполненное на МДП-транзистррах, содержащее первый транзистор с каналом -типа, сток которого подключен к стоку второго транзистора с каналом р-типа, затвор которого подключен к входу устройства, а исток - к шине первого источника положительного напряжения, третий транзистор с каналом п -типа, исток которого подключен к шине отрицательного источника напряжения, сток - к выходу устройства и стоку четвертого транзистора с каналом р-типа, исток которого подключен к шине второго источника положительного напряжения, исток пятого транзистора с каналом h-типа подключен к шине отрицательного источника напряжения, затвор шестого транзистора с каналом р-типа подключен к шине нулевого потенциала, сток к стоку седьмого транзистора с каналом -типа, затвор восьмого транзистора с каналом р-типа подключен к выходу устройства, сток к затвору четвертого транзистора, а исток - к шине второго источника положительного напряжения, от§ личающееся тем, что, с целью увеличения быстродействия, (Л затвор первого транзистора подключен к входу устройства, исток - к шине нулевого потенциала, сток - к стоку седьмого транзистора, затвор которого подключен к истоку второго транзистора, а исток - к стоку восьмого транзистора,затвор которого подключен к затвору пятого транзистора, с) сток которого подключен к истоку СО шестого транзистора и затвору третьего транзистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство преобразования уровней напряжения | 1976 |

|

SU558400A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство согласования ттл-схемС Мдп-иНТЕгРАльНыМи СХЕМАМи | 1979 |

|

SU818015A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-08-23—Публикация

1983-02-04—Подача