Изобретение относится к вычислительной технике и предназначено для вычисления кратного интеграла от одномерной решетчатой функции с постоянным шагом дискретизации, в частности, может быть использовано в качестве блока в устройствах идентификации или имитации линейных стандартных объектов.

Целью изобретения является повышение точности.

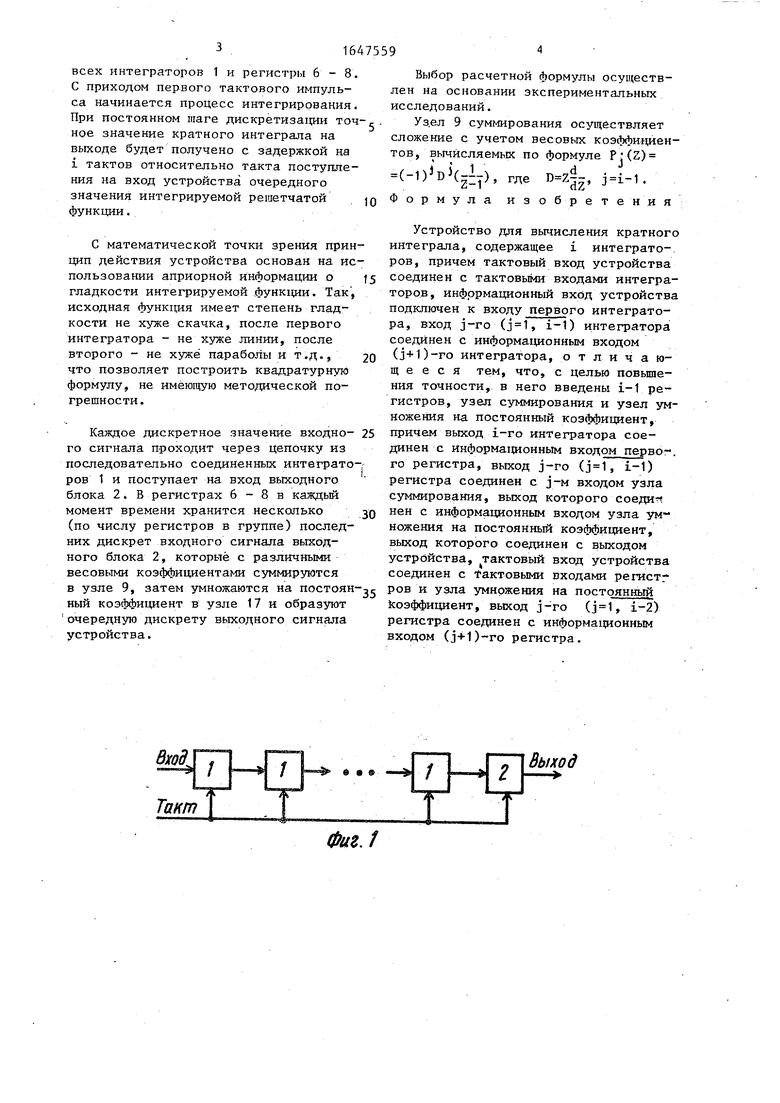

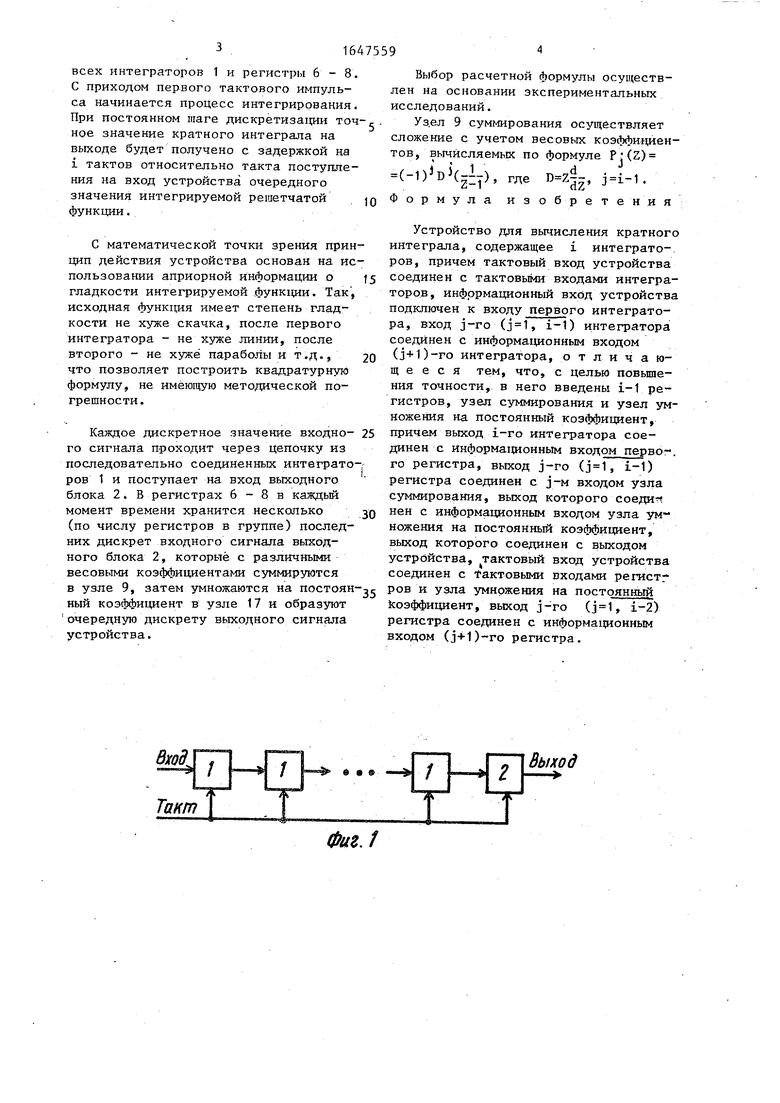

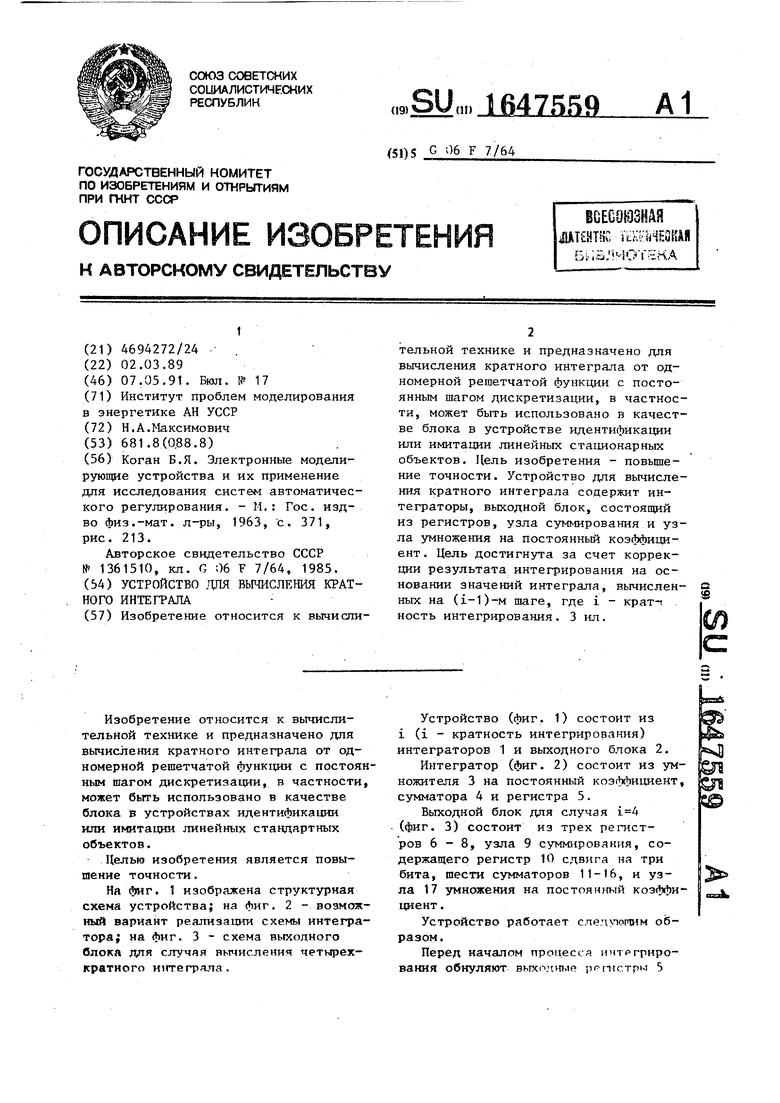

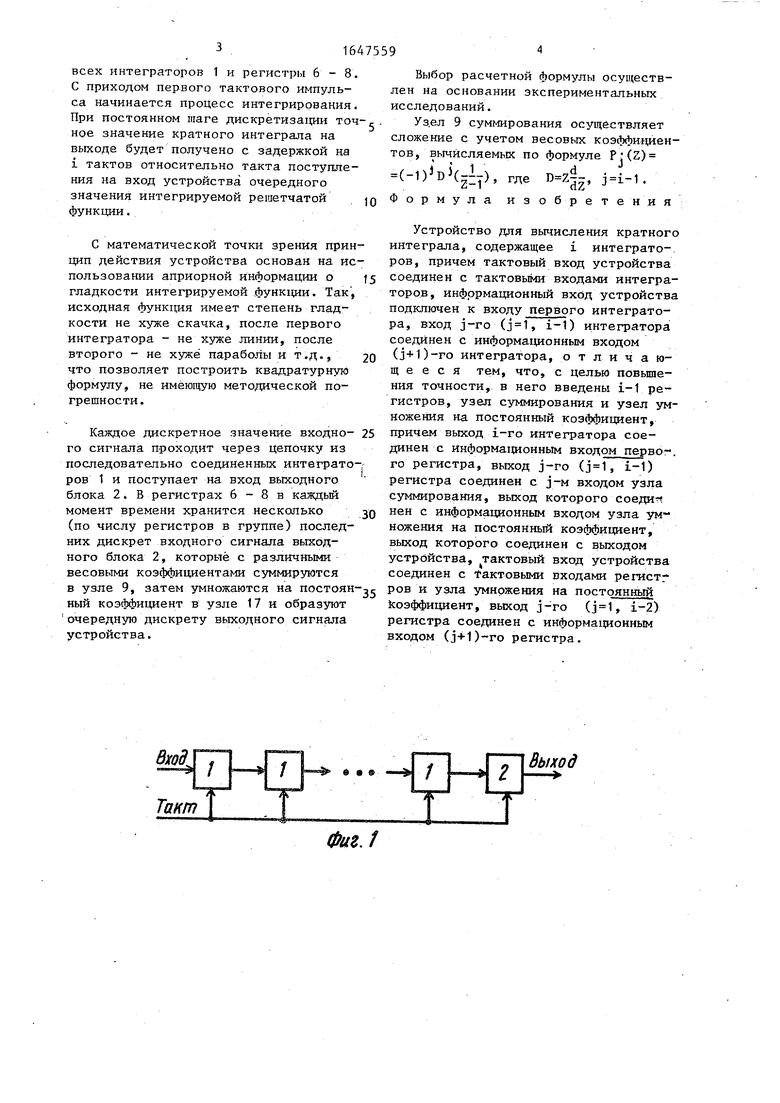

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - возможный вариант реализации схемы интегратора; на фиг. 3 - схема выходного блока для случая вычисления четырехкратного интеграла.

Устройство (фиг. 1) состоит из i (i - кратность интегрирования) интеграторов 1 и выходного блока 2.

Интегратор (фиг. 2) состоит из умножителя 3 на постоянный коэффициент, сумматора 4 и регистра 5.

Выходной блок для случая (фиг. 3) состоит из трех регистров 6-8, узла 9 суммирования, содержащего регистр 10 сдвига на три бита, шести сумматоров 11-16, и узла 17 умножения на постоянный коэффициент.

Устройство работает с л ел утопим образом.

Перед началом пронесся интегрирования обнуляют выхпднме регистры 5

всех интеграторов 1 и регистры 6-8. С приходом первого тактового импульса начинается процесс интегрирования. При постоянном шаге дискретизации точ ное значение кратного интеграла на выходе будет получено с задержкой на i тактов относительно такта поступления на вход устройства очередного значения интегрируемой решетчатой функции.

С математической точки зрения принцип действия устройства основан на использовании априорной информации о гладкости интегрируемой функции. Так, исходная функция имеет степень гладкости не хуже скачка, после первого интегратора - не хуже линии, после второго - не хуже параболы и т.д., что позволяет построить квадратурную формулу, не имеющую методической погрешности .

Каждое дискретное значение входно- го сигнала проходит через цепочку из последовательно соединенных интеграторов 1 и поступает на вход выходного блока 2. В регистрах 6 - 8 в каждый момент времени хранится несколько (по числу регистров в группе) последних дискрет входного сигнала выходного блока 2, которые с различными весовыми коэффициентами суммируются в узле 9, затем умножаются на постоян ный коэффициент в узле 17 и образуют очередную дискрету выходного сигнала устройства.

Выбор расчетной формулы осуществлен на основании экспериментальных исследований.

Уз.ел 9 суммирования осуществляет сложение с учетом весовых коэффициентов, вычисляемых по формуле P:(Z)

(-1)JD(-iT), где , . Формула изобретения

Устройство для вычисления кратного интеграла, содержащее i интеграторов, причем тактовый вход устройства соединен с тактовыми входами интеграторов, информационный вход устройства подключен к входу первого интегратора, вход j-го (, i-1) интегратора соединен с информационным входом (j+l)-ro интегратора, отличающееся тем, что, с целью повышения точности, в него введены i-1 регистров, узел суммирования и узел умножения на постоянный коэффициент, причем выход 1-го интегратора соединен с информационным входом перво- го регистра, выход j-го (, i-1) регистра соединен с j-м входом узла суммирования, выход которого соеди- нен с информационным входом узла умножения на постоянный коэффициент, выход которого соединен с выходом устройства, тактовый вход устройства соединен с тактовыми входами регистг ров и узла умножения на постоянный коэффициент, выход j-ro (j-1 i-2) регистра соединен с информационным входом (j+1)-ro регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Устройство для интегрирования | 1979 |

|

SU822194A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1278886A1 |

| Процессор аппроксимационной обработки информации | 1988 |

|

SU1501089A1 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ | 2005 |

|

RU2292642C1 |

| Цифровой интегратор | 1980 |

|

SU879586A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления кратного интеграла от одномерной решетчатой функции с постоянным шагом дискретизации, в частности, может быть использовано в качестве блока в устройстве идентификации или имитации линейных стационарных объектов. Цель изобретения - повышение точности. Устройство для вычисления кратного интеграла содержит интеграторы, выходной блок, состоящий из регистров, узла суммирования и узла умножения на постоянный коэффициент. Цель достигнута за счет коррекции результата интегрирования на основании значений интеграла, вычисленных на (1-1)-м шаге, где i - крат-t ность интегрирования. 3 ил. с S

Фиг./

Выход

L..

food

Токт

J

фиг. 2

Вшод

Фиг.З

| Коган Б.Я | |||

| Электронные моделирующие устройства и их применение для исследования систем автоматического регулирования | |||

| - М.: Гос | |||

| изд- во физ.-мат | |||

| л-ры, 1963, с | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Кулиса для фотографических трансформаторов и увеличительных аппаратов | 1921 |

|

SU213A1 |

| Устройство для идентификации линейных стационарных объектов | 1985 |

|

SU1361510A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-07—Публикация

1989-03-02—Подача