I

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства содержащие регистр адрес,-., дешифратор адреса, накопитель, информационные регистры, блок контроля, производящий контроль записываемой и считываемой информации на соответствие информационных и контрольных разрядов и восстановление информации в случае сбоя в адресном тракте .

Недостатком этих устройств ярляется то, что.в них разрешается запись и считывание информации из любой ячейки.

Наиболее близким по технической сущности к изобретению является запоминающее устройство с расширенными функциональными возможностями, содержащее регистр и дешифратор адреса, накопитель, блок усилителей записи - считывании, дополнителный регистр слова, блок кон-троля, схемы НЕ, И lim 2 .

Недостатком данного устройства является низкое быстродействие при осуществлении контроля считываемой и записываемой информации.

Цель изобретения - увеличение быстродействия оперативного запоминающего устройства.

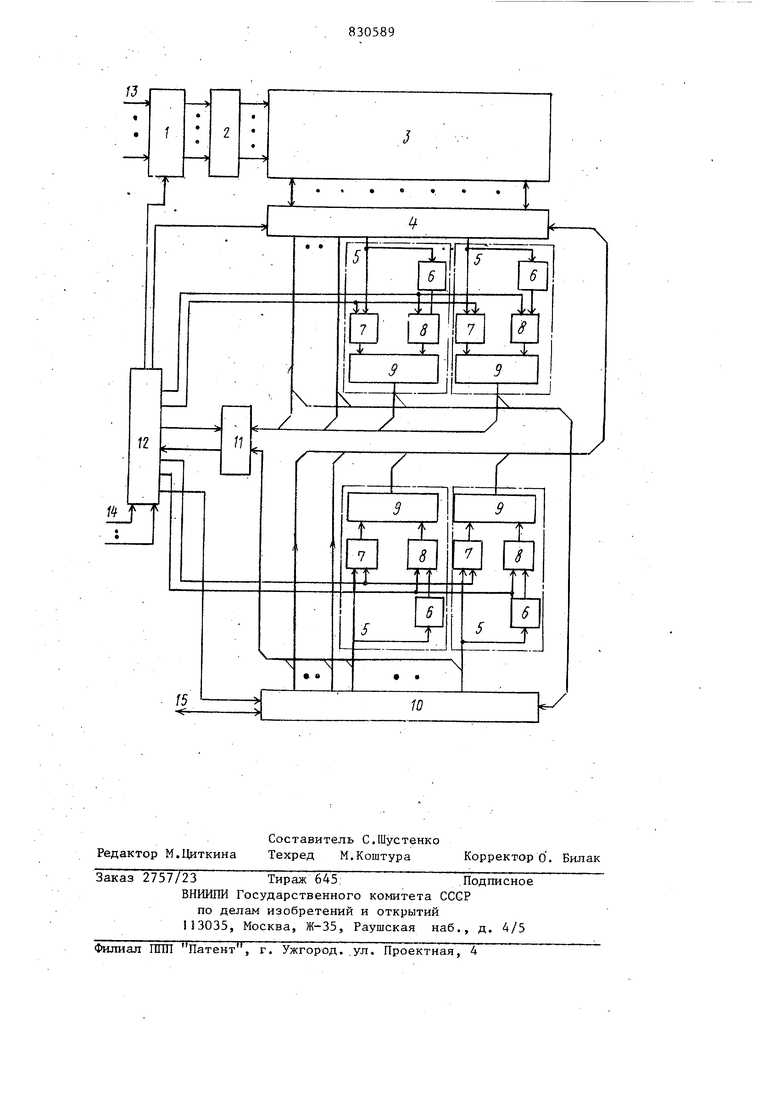

Поставленная цель достигается тем, что в оперативное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к выходам дешифратора, а его информационные входы - выходы - к входам-выходам блока усилителей,.входы адресного дешифратора подключены к выходам адресного регистра, вторые входы усилителей подключены к соответствующим выходам информационного регистра и к выхода инверторов, блок управления, выходы которрго подключены к управлякнци.м входам адресного регистра, усилителей, инверторов и блока контроля, выход блока контроля подключен ко входу блока управления, введены дополнительные инверторы, входы которых подключены к соответствующим выходам блока усилителей, одни входы блока контроля подключен к соответствующим выходам блока усилителей, к выходам дополнительных инверторов и ко входам информационного регистра, управляющие входы дополнительных инверторов подключены к соответствующим выходам блока управления. На чертеже приведена структурная схема устройства. Устройство содержит адресный регистр 1, дешифратор 2, накопитель 3 блок 4 усилителей, инверторы 5, эле менты НЕ 6, первые элементы И 7, вт рые элементы И 8, элементы ИЛИ.9, и формационный регистр 10, блок 11 ко троля, блок 12 управления, адресные шины 13, управляющие шины 14 и информационные шины 15 Устройство работает в следующих Запись, Запись с инверсие режимах: .«гиш-о , , Запись с пров контрольных разрядов Считьшание с и кой, Считывание, II версией контрольнь1х разрядов В режимах Запись, ЗапиСь версией контрольных разрядов и пись с проверкой адрес ячейки, находящийся на шинах 13, и записываемое слово, находящееся на щинах 15, фиксируются соответственно на адресном регистре I и на информацио ндм регистре 10, и производится подключение выходов информационного регистра 10 к блоку 11 контроля, который контролирует записываемую информацию. В случае появления на выходе блока 1I контроля сбоя инфор мация в накопитель не записывается. При отсутствии сигнала ошибки на вы ходе блока 11 контроля и работе в режиме записи информационные разряды напрямую, а контрольные - проходя с помощью управляющих сигналов через элементы И 7 и ИЛИ 9 - поступают на блок усилителей и с его выходов записываются в накопитель. Режим Запись с инверсией контро ных разрядов отличается от режима Запись тем, что их значения инвер тируются с помощью элементов НЕ 6. этом случае в ячейку записывается 94 слов.о с инвертированными контрольными разрядами. В режиме Считывание происходит считывание информации из накопителя в соответствии с адресом, хранимым в адресном регистре 1. Считанная информация появляется на выходах блока усилителей. Информационные разряды напрямую, а контрольные через элемент И 7 и через элемент ИЛИ 9 поступают на блок I1 контроля и информационный регистр 10. Появление сигнала ошибки на выходе блока 11 контроля свидетельствует о несоответствии информационных и контрольных разрядов. При отсутствии сигнала ошибки на выходе блока 11 контроля информация записьгоается в информационный регистр 10 и выдается на шины 15. Работа в р.ежиме Считывание с инверсией контрольных разрядов отличается от режима Считывание тем, что на выходах элементов ИЛИ 9 появляются контрольные разряды, инвертированные элементами НЕ 6. Отсутствие сигнала ошибки на выходе блока 1 1 контроля свидетельствует о прагвильной работе устройства. При работе устройства в режиме Запись с проверкой сразу же начинается считывание слова по адресу, хранимому в адресном регистре 1, и контроль записываемого слова. Это возможно, так как считывание слова является более инерционным процессом и моменты контроля записываемого и считываемого слова можно разнести во времени. Если на выходе блока 11 контроля сигнал ошибки не появляется, то осуществляется запись слова через блок 4 усилителей в накопитель 3. Таким образом, устройство вьщает сигнал ошибки в следующих случаях: при сбое входной информации, при попытке записи данных в режиме Запись с проверкой в ячейки, в которые данные при начальной загрузке были записаны в режиме Запись с инверсией контрольных разрядов, при попытке считывания данных в режиме Считывание из ячеек, в которые данные при начальной загрузке были записаны в режиме. Запись с инверсией контрольных разрядов. Выигрыш в быстродействии получен за счет отсутствия такта записи считанной из накопителя информации в допо нительный регистр в режимах Считывание и Считывание с инверсией контрольных разрядов и за счет сов мещения начала моментов считьшания из накопителя и контроля записываемой информации в режиме Запись с проверкой. Формула изобретения Оперативное запомииающее устройство, содержащее накопитель, адресные входы которого подключены к выходам дешифратора, а его информационные входы - выходы - к входам-в ходам блок.а усилителей, входы дешифратора подключены к выходам адресного регистра, вторые входы блока усилителей подключены к соответству ющим выходам информационного регист ра и к выходам инверторов, блок управления, выходы которого подключен к управляющим входам адресного ре.гистра, блока усилителей, инверторов и блока контроля, выход блока контроля подключен ко входу блока управления, отличающееся тем,, что,, с целью повьппения быстродействия устройства, в него введены дополнительные инверторы, входы которых подключены к соответствующим выходам блока усилителей, одни входы блока контроля подключены к соответствующим выходам блока усилителей, к выходам дополнительных инверторов и ко входам информационного регистра,управляющие входы дополнительных инверторов подключены к соответствующим выходам блока управления . Источники информации, .принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 528614, кл. G 11 С 29/00, 26.07.74. 2.Авторское свидетелвство СССР . по заявке № 2571643/J8-24, кл. G П С 29/00, 18.0J. 79 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1978 |

|

SU739659A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1986 |

|

SU1439679A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU847377A1 |

| Запоминающее устройство | 1986 |

|

SU1361636A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с исправлением ошибок | 1982 |

|

SU1128294A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

Авторы

Даты

1981-05-15—Публикация

1979-08-22—Подача