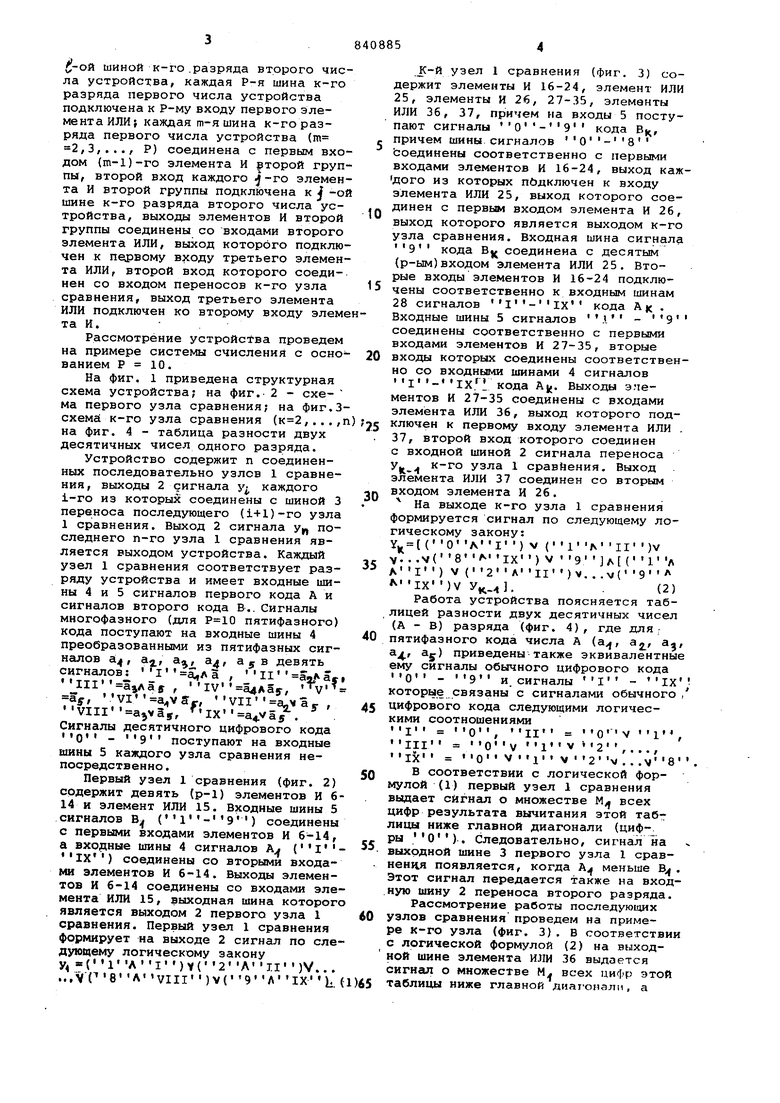

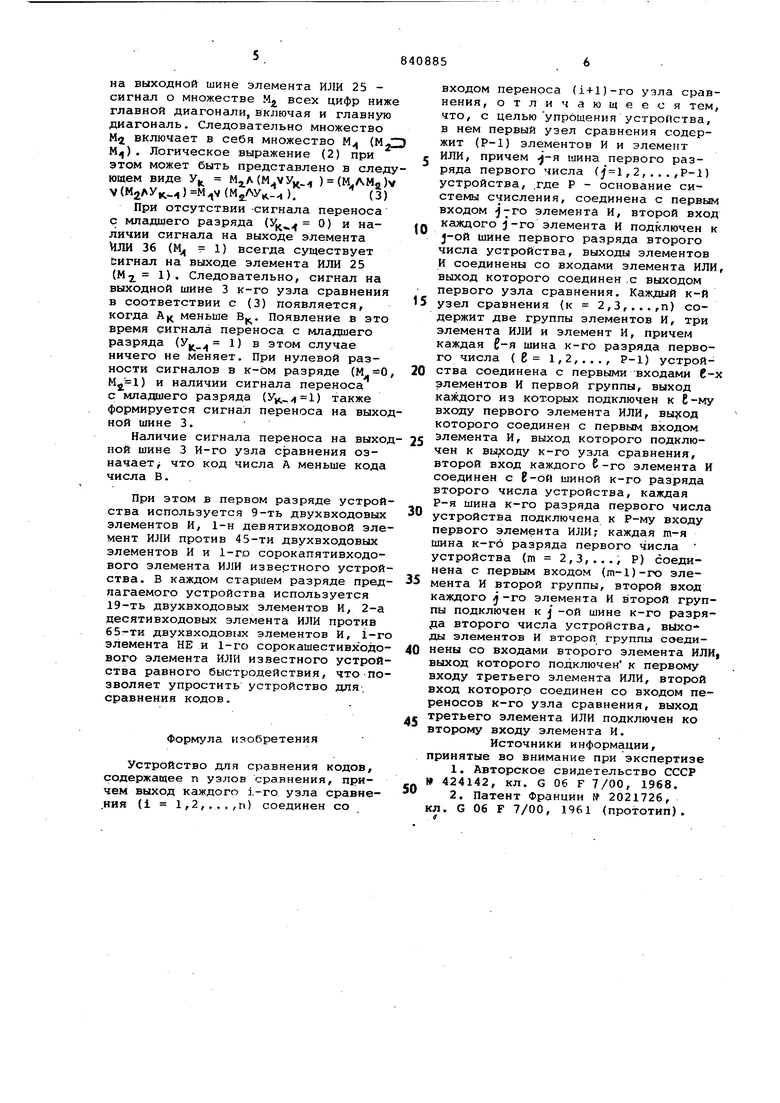

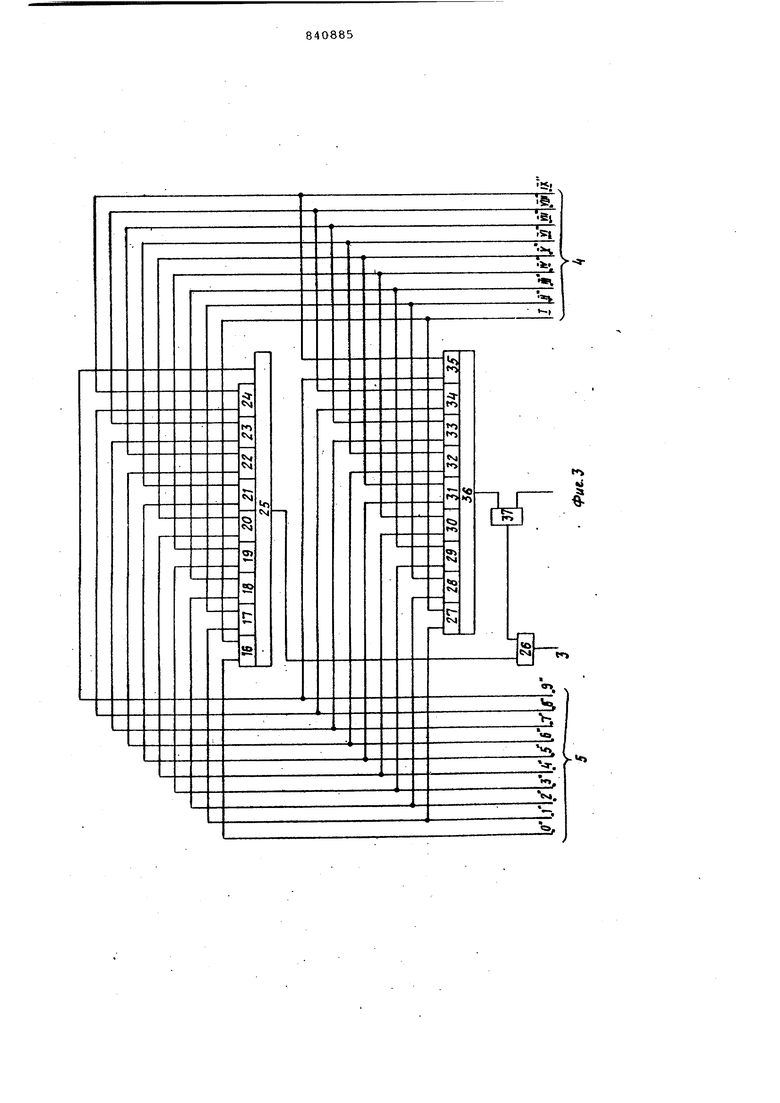

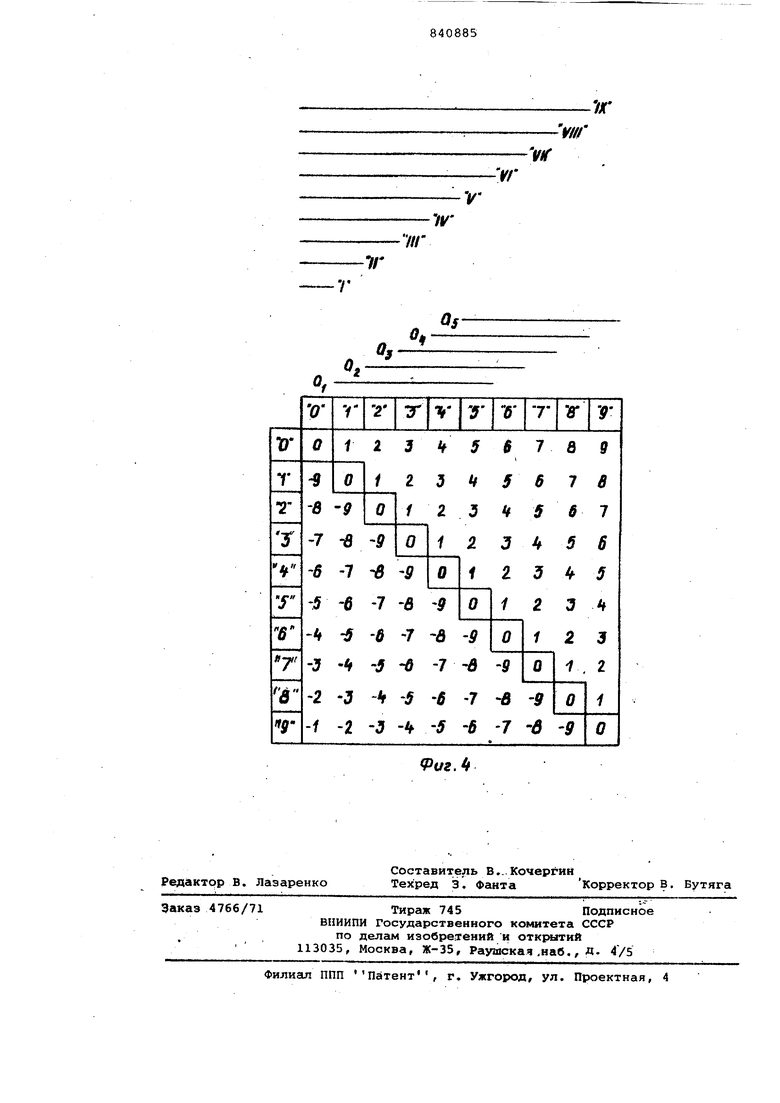

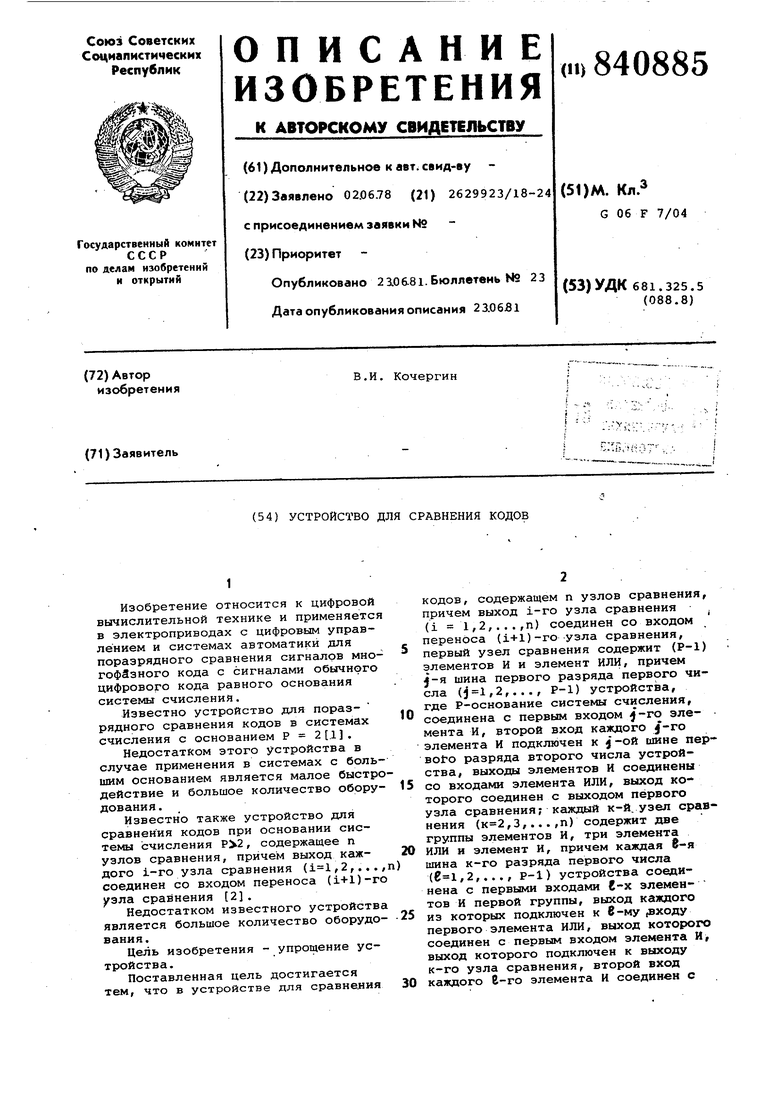

Изобретение относится к цифровой вычислительной технике и применяетс в электроприводах с цифровым управлением и системах автоматики для поразрядного сравнения сигналов многофЗэного кода с сигналами обычного цифрового кода равного основания системы счисления. Известно устройство для поразрядного сравнения кодов в системах счисления с основанием Р 2.1. Недостатком этого устройства в случае применения в системах с боль шим основанием является малое быстро действие и большое количество обору дования. Известно также устройство для сравнения кодов при основании системы счисления , содержащее п узлов сравнения, причем выход каждого 1-го узла сравнения (,2,... соединен со входом переноса (i+l)-r узла сравнения 2. Недостатком известного устройств является большое количество оборудо вания. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве для сравнеяия кодов, содержащем п узлов сравнения, причем выход i-ro узла сравнения (i 1,2,...,п) соединен со входом переноса (i+l)-ro узла сравнения, первый узел сравнения содержит (Р-1) элементов И и элемент ИЛИ, причем 4-я шина первого разряда первого числа (,2,..., Р-1) устройства, где Р-основание системы счисления, соединена с первым входом -го элемента И, второй вход казкдого J-ro элемента И подключен к j-ой шине перBOto разряда второго числа устройства, выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен с выходом первого узла сравнения; каждый к-й, узел сравнения (,3,...,п) содержит две группы элементов И, три элемента ИЛИ и элемент И, причем каждая в-я шина к-го разряда первого числа (,2,..., Р-1) устройства соединена с первыми входами С-х элементов И первой группы, выход каждого из которых подключен к в-му ходу первого элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого подключен к выходу к-го узла сравнения, второй вход каждого 6-го элемента И соединен с -ой шиной к-го .разряда второго числа устройства, каждая Р-я шина к-го разряда первого числа устройства подключена к Р-му входу первого элемента ИЛИ} каждая т-я шина к-го разряда первого числа устройства (т 2,3,..., Р) соединена с первым входом (m-l)-ro элемента И торой группы, второй вход каждого -го элемента И второй группы подключена к -ой шине к-го разряда второго числа устройства, выходы элементов И второй группы соединены со входами второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен со входом переносов к-го узла сравнения, выход третьего элемента ИЛИ подключен ко второму входу элеме та И. . Рассмотрение устройства проведем на примере системы счисления с основанием Р 10. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема первого узла сравнения; на фиг.З схемй к-го узла сравнения (,...,п на фиг. 4 - таблица разности двух десятичных чисел одного разряда. Устройство содержит п соединенных последовательно узлов 1 сравнения, выходы 2 9игнала у, каждого i-ro из которых соединены с шиной 3 переноса последующего (i+l)-ro узла 1 сравнения. Выход 2 сигнала у последнего п-го узла 1 сравнения является выходом устройства. Каждый узел 1 сравнения соответствует разряду устройства и имеет входные шины 4 и 5 сигналов первого кода А и сигналов второго кода В.. Сигналы многофазного (для пятифазного) кода поступают на входные шины 4 преобразованными из пятифазных сигналов а, ау, а, а, а к в девять сигналов: ,ла , II 32 3.. lII aiAaff , Iv a4Aay, v %, ., ,va5. , VIII a5vi5, . / Сигналы десятичного цифрового кода О - 9 поступают на входные шины 5 каждого узла сравнения непосредственно. Первый узел 1 сравнения (фиг. 2) содержит девять (р-1) элементов И 6 14 и элемент ИЛИ 15. Входные шины 5 сигналов В (-9 ) соединены с первыми входами элементов И 6-14, а входные шины 4 сигналов А ( IX) соединены со вторыми входами элементов И 6-14. Выходы элементов И 6-14 соединены со входами эле мента ИЛИ 15, выходная шина которог является выходом 2 первого узла 1 сравнения. Первый узел 1 сравнения формирует на выходе 2 сигнал по сле дующему логическому закону У4 ()y()V... ..,i/()V( :-й узел 1 сравнения (Фиг. 3) содержит элементы И 16-24, элемент ИЛИ 25, элементы И 26, 27-35, элементы ИЛИ 36, 37, причем на входы 5 поступают сигналы О-9 кода Вц, причем шины сигналов соединены соответственно с первыми входами элементов И 16-24, выход каждого из которых подключен к входу элемента ИЛИ 25, выход которого соединен с первым входом элемента И 26, выход которого является выходом к-го узла сравнения. Входная шина сигнала 9 кода Bj{ соединена с десятым (р-ым)входом элемента ИЛИ 25. Вторые входы элементов И 16-24 подключены соответственно к входным шинам 28 сигналов I-Чх кода А к . Входные шины 5 сигналов А - 9 соединены соответственно с первыми входами элементов И 27-35, вторые входы которых соединены соответственно со входными шинами 4 сигналов .l кода Aj{. Выходы элементов И 27-35 соединены с входами элемента ИЛИ 36, выход которого подключен к первому входу элемента ИЛИ . 37, второй вход которого соединен с входной шиной 2 сигнала переноса у. . к-го узла 1 сравнения. Выход элемента ИЛИ 37 соединен со вторым входом элемента И 26. На выходе к-го узла 1 сравнения формируется сигнал по следующему логическому закону: У.. ()v(l II)v V. ..v() V С )v()v...v(9 IX)V УК-Ч.(2) Работа устройства поясняется таблицей разности двух десятичных чисел (А - В) разряда (фиг. 4), где для г пятифазного кода числа А (а а, а) приведены также эквивалентн ему сигналы обычного цифрового кода IQI I I 191 и сигналы которые связаны с сигналами обычного , цифрового кода следующими логическими соотношениями Ч О, II Ov , III 1 V «2,. .., IX 0 V i««v2 /... В соответствии с логической формулой (1) первый узел 1 сравнения выдает сйгнгш о множестве М всех цифр результата вычитания этой таблицы ниже главной диагонали (цифры О). Следовательно, сигнал на выходной шине 3 первого узла 1 сравнения появляется, когда А меньше В. Этот сигнал передается также на вход.ную шину 2 переноса второго разряда. Рассмотрение работы последующих узлов сравнения проведем на примере к-го узла (фиг. 3). В соответствии с логической формулой (2) на выходной шине элемента ИЛИ 36 выдается сигнал о множестве М всех цифр этой таблицы ниже главной диат-оналп, а на выходной шине элемента ИЛИ 25 сигнал о множестве М, всех цифр ниже главной диагонали, включая и главную диагональ. Следовательно множество Mj включает в себя множество М (MV М). Логическое выражение (2) при этом может быть представлено в следу ющем виде Уц (M.vy,4 ) (МЛМа)у V(M2AyK-l)(MjjAy). (3) При отсутствии -сигнала переноса с младшего разряда (Уц 0) и наличии сигнала на выходе элемента или 36 (М - 1) всегда существует Сигнал на выходе элемента ИЛИ 25 (М. 1). Следовательно, сигнал на выходной шине 3 к-го узла сравнения в соответствии с (3) появляется, когда АИ меньше В,. Появление в это время сигнала переноса с младшего разряда (Уц 1) в этом случае ничего не меняет. При нулевой разности сигналов в к-ом разряде (М 0 ) и наличии сигнала переноса с младшего разряда (Уц.) также формируется сигнал переноса на выход ной шине 3. Наличие сигнала переноса на выход ной шине 3 И-го узла сравнения означает/ что код числа А меньше кода числа В. При этом в первом разряде устрой ства используется 9-ть двухвходовых элементов И, 1-н девятивходовой эле мент ИЛИ против 45-ти двухвходовых элементов И и 1-го сорокапятивходового элемента ИЛИ известного устрой ства. В каждом старшем разряде предлагаемого устройства используется 19-ть двухвходовых элементов И, 2-а десятивходовых элемента ИЛИ против 65-ти двухвходових элементов И, 1-го элемента НЕ и 1-го сорокашестивходового элемента ИЛИ известного устройства равного быстродействия, что-позволяет упростить устройство для. сравнения кодов. Формула изобретения Устройство для сравнения кодов, содержащее п узлов сравнения, причем выход каждого 1-го узла сравне.ния (1 1,2,..,,п) соединен со входом переноса (i+l)-ro узла сравнения, отличающееся тем, что, с цельюупрощения устройства, в нем первый узел сравнения содержит (Р-1) элементов И и элемент ИЛИ, причем -я шина первого разряда первого числа (,2,...,Р-1) устройства, .где Р - основание системы счисления, соединена с первым входом элемента И, второй вход каждогоj-го элемента И подключен к j-ой шине первого разряда второго числа устройства, выходы элементов И соединены со входами элемента ИЛИ, выход которого соединен .с выходом первого узла сравнения. Каждый к-й узел сравнения (к 2,3,...,п) содержит две группы элементов И, три элемента ИЛИ и элемент И, причем каждая С-я шина к-го разряда первого числа (6 1,2,..., Р-1) устройства соединена с первыми входами С-х элементов И первой группы, выход каждого из которых подключен к 6-му входу первого элемента ИЛИ, которого соединен с первым входом элемента И, выход которого подключен к к-го узла сравнения, второй вход каждого С-го элемента И соединен с В-ой шиной к-го разряда второго числа устройства, каждая Р-я шина к-го разряда первого числа устройства подключена к Р-му входу первого элемента ИЛИ; каждая га-я шина к-го разряда первого числа устройства (т 2,3,..., Р) соединена с первым входом (m-D-rc элемента И второй группы, второй вход каждого -го элемента И второй группы подключен к j -ой шине к-го разряда второго числа устройства, выходы элементов И второй группы соединены со входами второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которог.о соединен со входом переносов к-го узла сравнения, выход третьего элемента ИЛИ подключен ко второму входу элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 424142, кл. G 06 F 7/00, 1968. 2.Патент Франции № 2021726, л. G 06 F 7/00, 1961 (прототип). 4 f 2..нр11-1.--ш а j V Jf Фе/ал

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения кодов | 1982 |

|

SU1080134A1 |

| Устройство для умножения | 1979 |

|

SU826341A1 |

| Устройство для деления | 1985 |

|

SU1291974A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1989 |

|

SU1633393A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Цифроаналоговый преобразователь с многофазным выходом | 1987 |

|

SU1476611A1 |

| Устройство для деления | 1984 |

|

SU1252772A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

S fput.i

&

2

гп «Ч

4

«VJ

1, ч

i.

УК

Д: «)

К

Ч

«о

:

у .

ь у.

-Jr.

игЛ

Авторы

Даты

1981-06-23—Публикация

1978-06-02—Подача