(54) УСТРОЙСТВО ДЛЯ ввода и ПРЕДВАРИТЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ

Двоичная информация, состоящая и м двоичных чисел, подаваемая на устройство для ранжирования чисел, линейно записывается в сдвиговом регистре информации, ранги которых должны быть определены и для циркуляционного сдвига этих чисел, В Ьдвиговый регистр эталонных данных рчитывается одно число из информацки, хранимой в сдвиговом регистре информации. При этом числа, которые хранятся в сдвиговом регистре информации и которые не считаны в сдвиговый регистр эталонных данных, последовательно сравниваются в схеме сравнения с числом, считанным в сдвиговый регистр эталонных данных. Схема сравнения выдает сигнал каждый раз,когда обнаруживается,что любое число-ичеет определеную числовую связь с эталонным числом. Количество выходных сигналов схемы сравнения подсчитывается счетчиками и полученные результаты чере выходную схему изображаются или записываются для ранжирования двоич ных чисел. Временная схема и схема управления обеспечивают синхронизацию работы всего устройства для ранжировки чисел 2.

Недостаток этого устройства состоит в низком быстродействии, вследствие чего при использовании устройства в автоматизированных системах управления и контроля для предварительной обработки высокоскоростной цикличности повторяющейся стационарной двоичной кодовой информации при большом ее объеме, не обеспечивется обработка ее без потери входно информации из-за необходимости использования в указанном устройстве большого количества времени для ранжировки чисел, причем затрачиваемое время тем больше, чем выше разрядность кодов двоичных чисел. Кроме того, устройство не производит упаковку информации в позиционный код для передачи .его в вычислительные средства, а также требует большого объема аппаратных средств.

Цепь изобретения - увеличение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее узел управления, первый и второй входа) которого соединены соответственно со входами запуска и тактов устройства, а первым выходом с управляющим входом комму таторагпервьш информационным входом подключенного к выходу регистра сдвига эталонных кодов,первый вход которого соединен с выходом элемента и, первым входом соединенного с входом тактов устройства и первым входом регистра сдвига информации, второй вход соторого подключен к информационному входу

устройства, а выход - ко второму bi;формационному входу коммутатора, первым и вторым выходами соединенного соответственно с первым и вторым .входами схемы сравнения, и узел сопряжения с вычислительной машиной, вход-выход которого является входсм-выхрдом устройства, введен узел хранения результатов сравнения, причем три входа узла хранения результатов сравнения соединены соответственно с первым и вторым выходами схемы сравнения и вторым выходом узла управления, а выход - со входом узла сопряжения с вычислительной машиной, выходом подключенного ко второму входу регистра сдвига эталонных кодов, второй вход элемента И соединен с первым выходом узла управления

Узел управления содержит триггер пуска, .выход которого и второй вход подключены соответственно к первому и второму входу элемента И, выходом соединенного со входом счетчика длины кода информации, выход которого подк.точен к первым входам счетчика количества слов в цикле, выходного триггера и счетчика длины позиционного кода, выходом соединенного с первым входом элемента ИЛИ, а вторым входом - с первым входом триггера пуска, вторым входом элемента ИЛИ, вторым входом выходного триггера и выходом счетчика количества слов в цикле, второй вход которого соединен со вторым входом триггера пуска и первым входом блока, выходы выходного триггера и элемента ИЛИ являются соответственно первым и вторым выходами узла.

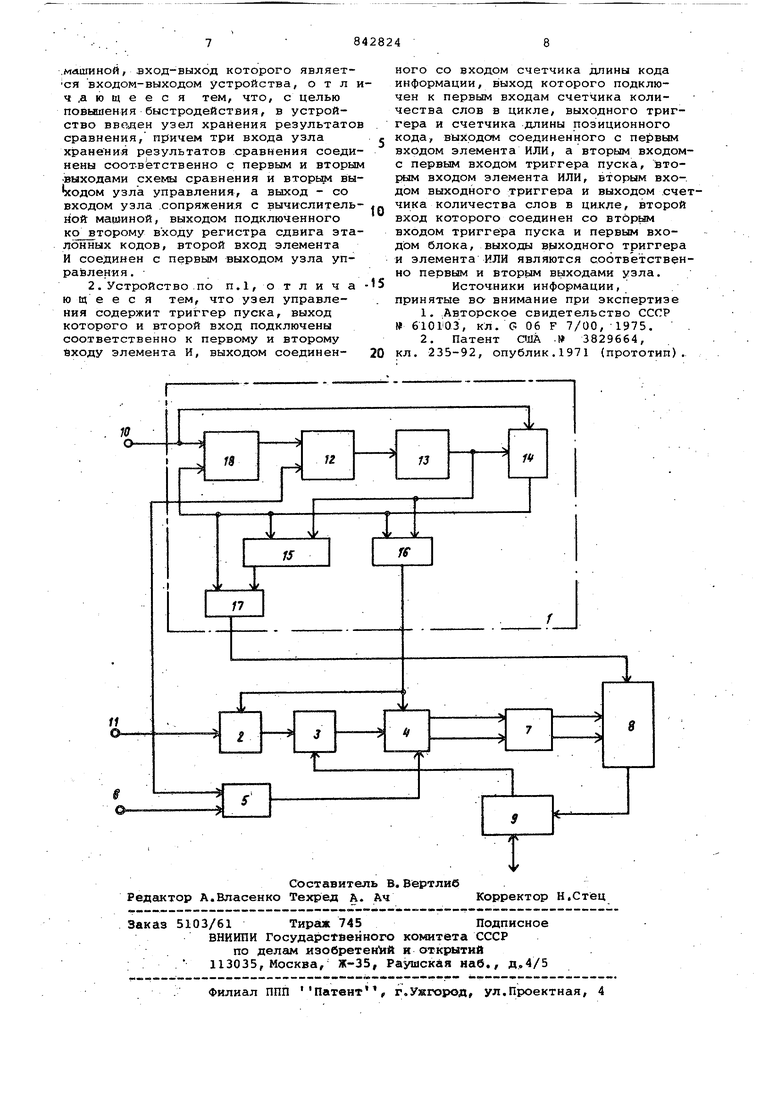

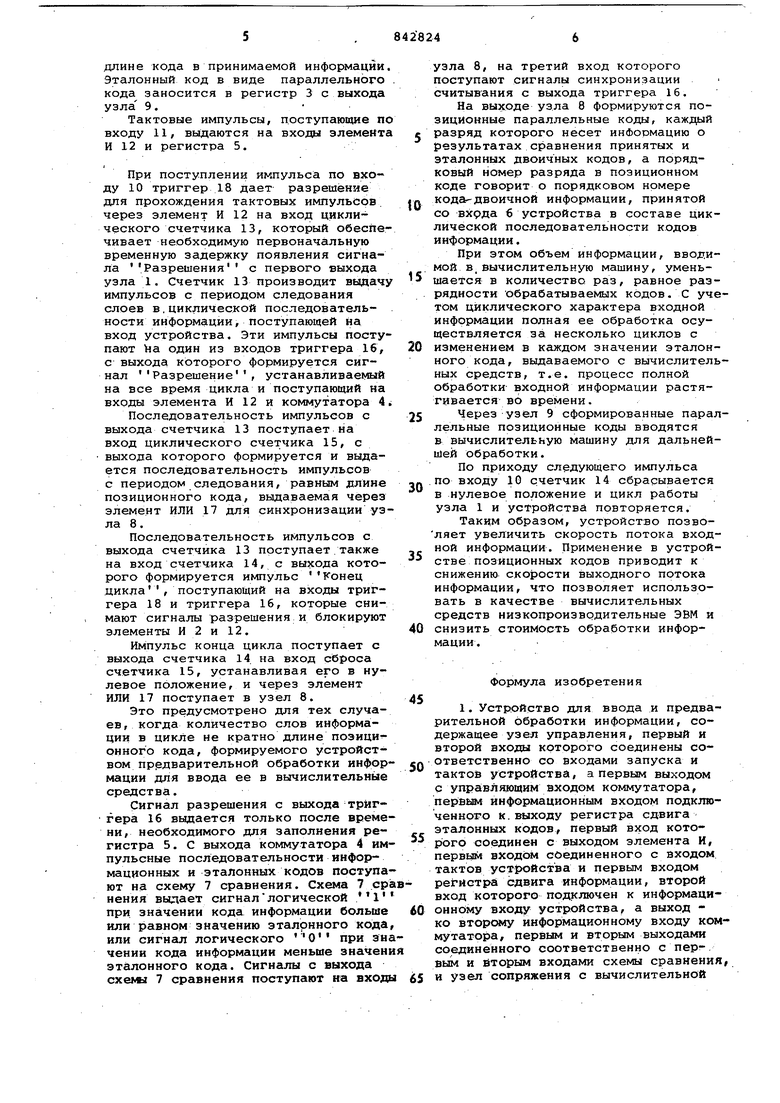

На чертеже представлено устройство, блок-схема.

Оно содержит узел 1 управления, элемент И 2, регистр 3 сдвига эталонных кодов, коммутатор 4, регистр 5 сдвига информации, информационный вход 6 устройства,схему 7 сравнения, узел 8 хранения результатов сравнения, узел 9 сопряжения с вычислительной машиной, входы 10 и 11 запуска и тактов устройства.

Узел 1 управления содержит элемент И 12, счетчик 13 длины кода информации, счетчик 14 количества слов в цикле, счетчик 15 длины позиционного кода, выходной триггер 16, элемеит ИЛИ 17 и триггер 18 пуска.

Устройство работает следующим образом.

Со -йхоаа. 6 устройства на регистр 5 поступает циклическая кодовая информация, которая записывается и продвигается тakтoвыми импульсами, поступающими по входу 11. на второй вход коьвлутатора 4. На первый вход коммутатора с выхода регистра 3 поступают импульсы циклически повторяющегося эталонного кода. Количество разрядов регистра 5 равно

длине кода в принимаемой информации. Эталонный код в виде параллельного кода заносится в регистр 3 с выхода узла 9.

Тактовые импульсы, доступающие по входу 11, выдаются на входы элемента И 12 и регистра 5.

При поступлении импульса по вхо ду 10 триггер 18 дает разрешение для прохождения тактовых импульсов. через элемент И 12 на вход циклического счетчика 13, который обеспечивает необходимую первоначальную временную задержку появления сигнала Разрешения с первого выхода узла 1. Счетчик 13 производит вьэдачу импульсов с периодом следования слоев в,циклической последовательности информации, поступающей на вход устройства. Эти импульсы поступают а один из входов триггера 16, с выхода которого формируется сигнал Разрешение, устанавливаемый на все время цикла и поступающий на входы элемента И 12 и коммутатора 4

Последовательность импульсов с выхода счетчика 13 поступает на вход циклического счетчика 15, с выхода которого формируется и выдается последовательность импульсов с периодом следования, равным длине позиционного кода, выдаваемая через элемент ИЛИ 17 для синхронизации узла 8.

Последовательность импульсов с выхода счетчика 13 поступает.также на вход счетчика 14, с выхода которого формируется импульс Конец цикла , поступающий на входы триггера 18 и триггера 16, которые снимают сигналы разрешения и блокируют элементы И 2 и 12.

Импульс конца цикла поступает с выхода счетчика 14 на вход сброса счетчика 15, устанавливая его в нулевое положение, и через элемент ИЛИ 17 поступает в узел 8.

Это предусмотрено для тех случаев, когда количество слов информации в цикле не кратно длине позици онного кода, формируемого устройством предварительной обработки информации для ввода ее в вычислительные средства.

Сигнал разрешения с выхода триггера 16 выдается только после времени, необходимого для заполнения регистра 5. С выхода коммутатора 4 импульсные последовательности информационных и эталонных кодов поступают на схему 7 сравнения. Схема 7 сранения выдает сигналлогической при значении кода информации больше или равном значению эталонного кода, или сигнёш логического О при значении кода информации меньше значени эталонного кода. Сигналы с выхода схемы 7 сравнения поступают на входы

узла 8, на третий вход которого поступают сигналы синхронизации считывания с выхода триггера 16.

На выходе узла 8 формируются позиционные параллельные коды, каждый разряд которого несет информацию о результатах сравнения принятых и эталонных двоичных кодов, а порядковый номер разряда в позиционном коде говорит о порядковом номере кодаг-двоичной информации, принятой со вхрда 6 устройства в составе циклической последовательности кодов информации.

При этом объем информации, вводимой в вычислительную машину, уменьшается в количество раз, равное разрядности Обрабатываемых кодов, С учетом циклического характера входной информации полная ее обработка осуществляется за несколько циклов с изменением в каждом значении эталонного кода, выдаваемого с вычислительных средств, т.е. процесс полной обработки входной информации растягивается во времени.

Через узел 9 сформированные параллельные позиционные коды вводятся в вычислительную машину для дальнейшей обработки.

По приходу следующего импульса .по входу 10 рчетчик 14 сбрасывается в нулевое положение и цикл работы узла 1 и устройства повторяется.

Таким образом, устройство позволяет увеличить скорость потока входной информации. Применение в устройстве позиционных кодов приводит к снижению скорости выходного потока информации, что позволяет использовать в качестве вычислительных средств низкопроизврдительные ЭВМ и снизить стоимость обработки информации.

Формула изобретения

1. Устройство для ввода и предварительной обработки информации, содержащее узел управления, первый и второй входы которого соединены соответственно со входами запуска и TaKTOiB устройства, а первым выходом с управляющим входом коммутатора, перовым информационным входом подключенного к.выходу регистра сдвига эталонных кодов, первый вход которого соединен с выходом элемента И, первым входом соединенного с входом, тактов устройства и первым входом регистра сдвига информации, второй вход которого подключен к информационному входу устройства, а выход ко второму информационному входу коммутатора, первым и вторым выходгьми соединенного соответственно с первьш и йторым входами схемы сравнения и узел сопряжения с вычислительной .млшиной, вход-выход которого является входом-выходом устройства, о т л чдющеес я тем, что, с целью повьлаения быстродействия, в устройство введен узел хранения результато сравнения, причем три входа узла хранения результатов сравнения соеди нены соответственно с первым и вторы выходами схемы сравнения и вторьш вы Ьсодом узла управления, а выход - со входом узла .сопряження с вычислитель ной машиной, выходом подключенного ко второму входу регистра сдвига эта лонных кодов, второй вход элемента И соединен с первым выходом узла управления . 2. Устройство.по п,1,отлича ю щ е е с я тем, что узел управления содержит триггер пуска, выход которого и второй вход подключены соответственно к первому и второму входу элемента И, выходом соединенкого со входом счетчика длины кода информации, выход которого подключен к первым входам счетчика количества слов в цикле, выходного триггера и счетчика длины позиционного кода, выхрдо соединенного с первым входом элемента ИЛИ, а вторым входомс первым входом триггера пуска, вторым входом элемента ИЛИ, вторым входом выходного триггера и выходом счетчика количества слов в цикле, второй вход которого соединен со вторым входом триггера пуска и первым входом блока, выходы выходного триггера и элемента ИЛИ являются соответственно первым и вторым выходами узла. Источники информации, принятые во- внимание при экспертизе 1.Авторское свидетельство СССР W бЮГОЗ, кл. G 06 F 7/00, 1975. 2.Патент ОНА . 3829664, кл. 235-92, опублик.1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Многоканальное устройство для ввода в ЭВМ информации от двухпозиционных датчиков | 1986 |

|

SU1310794A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

Авторы

Даты

1981-06-30—Публикация

1979-07-09—Подача