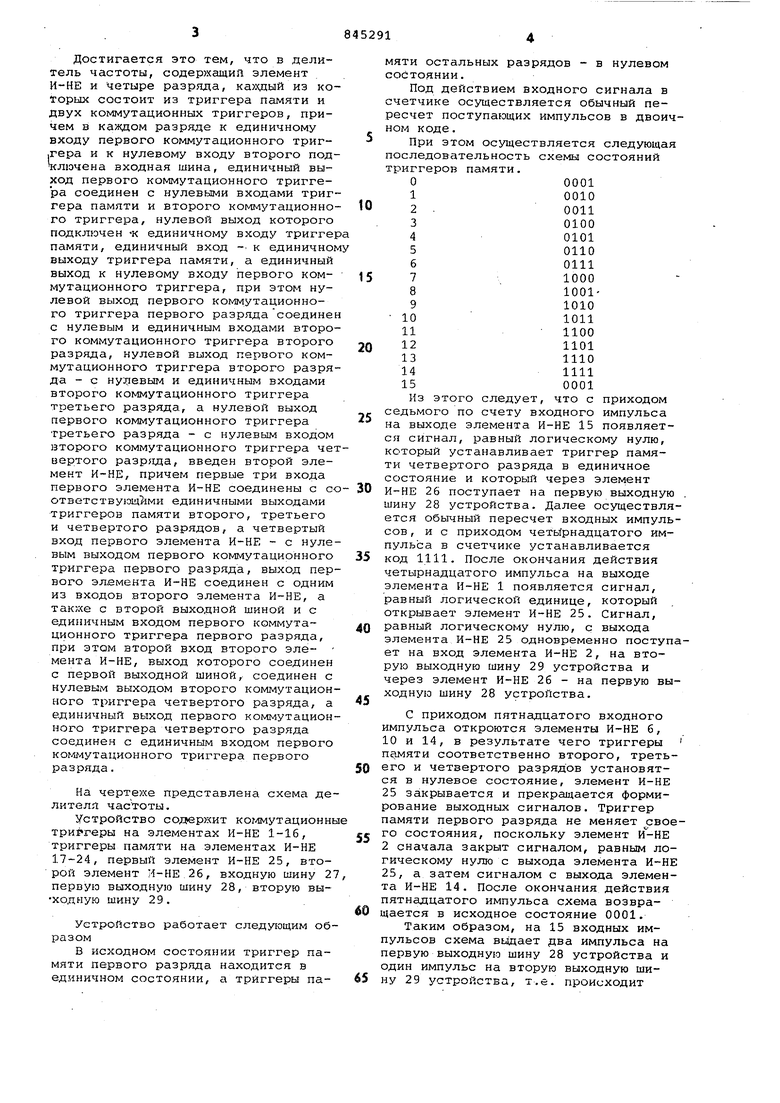

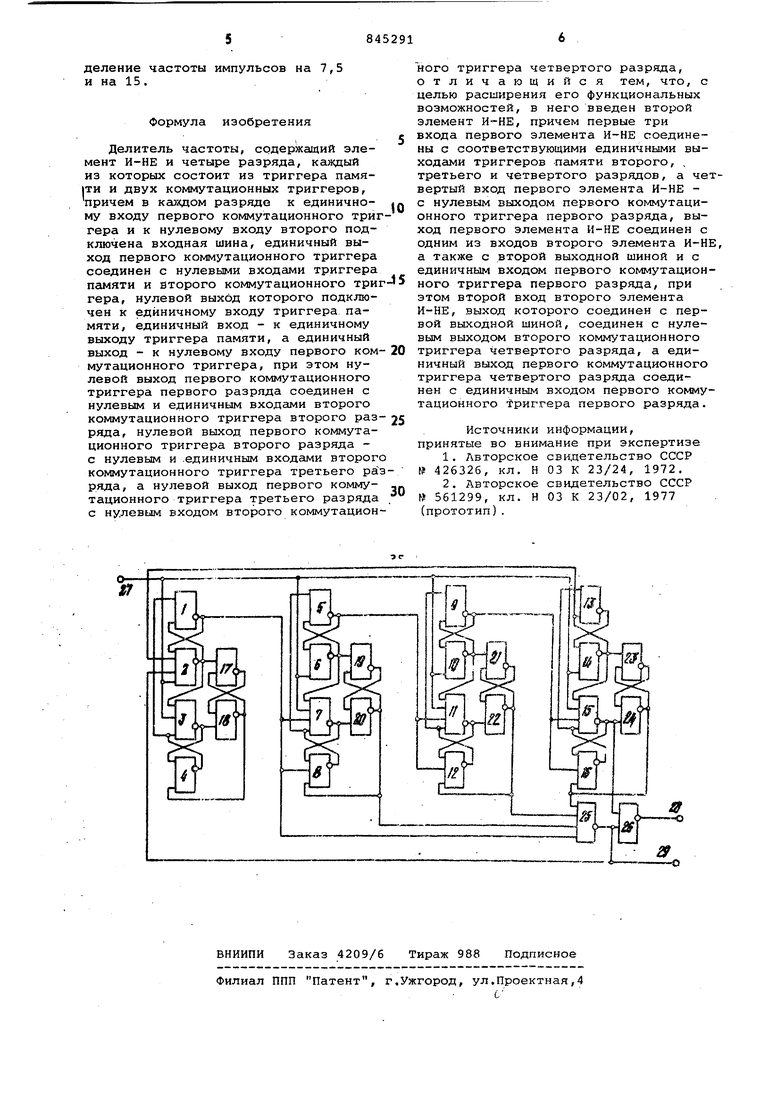

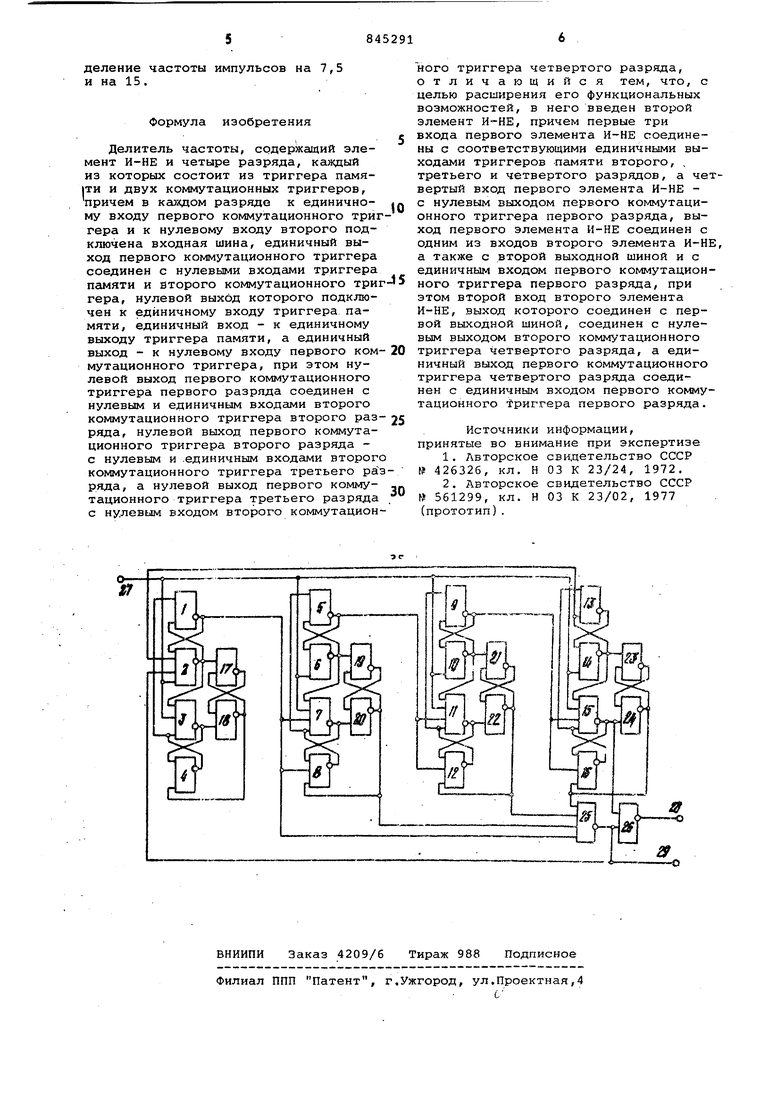

Изобретение относится к автомати-, ке и вычислительной технике и может быть использовано в устройствах, где необходимо деление частоты импульсов на 7,5 и на 15. Известны делители частоты, каждый разряд которых содержит триггеры памяти, коммутационные триггеры и схемы И-НЕ. Известно устройство, содержащее разряды, каждый из которых состоит из триггера памяти и коммутационного триггера, и элементы И-НЕ TilНаиболее близким к изобретению является устройство, содержащее элемент И-НЕ и четыре разряда, каждый из которых состоит из триггера памяти и двух коммутационных триггеров, причем в каждом разр5эде к единичному входу первого коммутационного триггера и к нулевому входу второго подключена входная шина, единичный выход первого коммутационного триггера соединен с. нулевыми входами триггера памяти и второго коммутационного тригге ра, нулевой выход которого подключен к единичному входу триггера памяти, единичный вход - к единичному выходу триггера памяти, а единичный выход - к нулевому первого коммутационного триггера, при этом нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным входами второго коммутационного триггера второго разряда, нулевой выход первого коммутационного триггера второго разряда - с нулевым и единичным входом второго коммутационного триггера третьего разряда, а нулевой выход первого коммутационного триггера третьего разряда - с нулевым входом второго коммутационного триггера четвертого разряда, причем единичный выходы первого и второго коммутационных триггеров четвертого разряда подключены к нулевым уходам втордго коммутационного триггера первого разряда, а входы схекв: И-НЕ соединены с нулевым выходом второго коммутационного триггера третьего разряда и с единичным выходом второго коммутационного триггера четвертого разряда Г2. Однако известное устройство не позволяет делить частоту импульсов на 7,5 и на 15, Целью изобретения является расширение функциональных возможностей устройства. Достигается это тем, что в делитель частоты, содержащий элемент И-НЕ и четыре разряда, из которых состоит из триггера памяти и двух коммутационных триггеров, причем в каждом разряде к единичному входу первого коммутационного триг|Гера и к нулевому входу второго подключена входная шина, единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационного триггера, нулевой выход которого подключен -к единичному входу триггер памяти, единичный вход - к единичном выходу триггера памяти, а единичный выход к нулевому входу первого коммутационного триггера, при этом нулевой выход первого коммутационного триггера первого разрядасоедине с нулевым и единичным входами второго коммутационного триггера второго разряда, нулевой выход первого коммутационного триггера второго разря да - с нулевым и единичным входами второго коммутационного триггера третьего разряда, а нулевой выход первого коммутационного триггера третьего разряда - с нулевым входом второго коммутационного триггера че вертого разряда, введен второй элемент И-НЕ, причем первые три входа первого элемента И-НЕ соединены с со ответствующйми единичными выходами триггеров памяти второго, третьего и четвертого разрядов, а четвертый вход первого элемента И-НЕ - с нуле вым выходом первого коммутационного триггера первого разряда, выход пер вого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, а также с второй выходной шиной и с единичным входом первого коммутационного триггера первого разряда, при этом второй вход второго эле- мента И-НЕ, выход которого соединен с первой выходной шиной, соединен с нулевым выходом второго коммутацион ного триггера четвертого разряда, а единичный выход первого коммутацион ного триггера четвертого разряда соединен с единичным входом первого коммутационного триггера первого разряда. На чертеже представлена схема де лителя частоты. Устройство содержит ког/мутационн триггеры на элементах И-НЕ 1-16, триггеры памяти на элементах И-НЕ 17-24, первый элемент И-НЕ 25, второй элемент И-НЕ, 26, входную шину 2 первую выходную шину 28, вторую выходную шину 29.. Устройство работает следующим об разом В исходном состоянии триггер памяти первого разряда находится в единичном состоянии, а триггеры памяти остальных разрядов - в нулевом состоянии. Под действием входного сигнала в счетчике осуществляется обычный пересчет поступающих импульсов в двоичном коде. При этом осуществляется следующая последовательность схемы состояний триггеров памяти. 00001 10010 2.ООН 30100 40101 5ОНО 60111 71000 8100191010 101011 111100 121101 131110 141111 150001 Из этого следует, что с приходом седьмого по счету входного импульса на выходе элемента И-НЕ 15 появляется сигнал, равный логическому нулю, который устанавливает триггер памяти четвертого разряда в единичное состояние и который через элемент И-НЕ 26 поступает на первую выходную . шину 28 устройства. Далее осуществляется обычный пересчет входных импульсов , и с приходом четь1рнадцатого импульса в счетчике устанавливается код 1111. После окончания действия четырнадцатого импульса на выходе элемента И-НЕ 1 появляется сигнал, равный логической единице, который открывает элемент И-НЕ 25. Сигнал, равный логическому нулю, с выхода элемента И-НЕ 25 одновременно поступает на вход элемента И-НЕ 2, на вторую выходную шину 29 устройства и через элемент И-НЕ 26 - на первую выходную шину 28 устройства. С приходом пятнадцатого входного импульса откроются элементы И-НЕ 6, 10 и 14, в результате чего триггеры соответственно второго, третьего и четвертого разрядов установятся в нулевое состояние, элемент И-НЕ 25 закрывается и прекращается формирование выходных сигналов. Триггер памяти первого разряда не меняет своего состояния, поскольку элемент 2 сначала закрыт сигналом, равным логическому нулю с выхода элемента И-НЕ 25, а затем сигналом с выхода элемента И-НЕ 14. После окончания действия пятнадцатого импульса схема возвращается в исходное состояние 0001. Таким образом, на 15 входных импульсов схема ввдает два импульса на первую выходную шину 28 устройства и один импульс на вторую выходную шину 29 устройства, т.е. происходит деление частоты импульсов на 7,5 и на 15. Формула изобретения Делитель частоты, содержащий элемент И-НЕ и четыре разряда, калодый из которых состоит из триггера памя|ти и двух коммутационных триггеров, причем в разряде к единичному входу первого коммутационного три гера и к нулевому входу второго подключена входная шина, единичный выход первого коммутационного триггера соединен с нулевыми входами триггера памяти и второго коммутационного три гера, нулевой выход которого подключен к единичному входу триггера памяти, единичный вход - к единичному выходу триггера памяти, а единичный выход - к нулевому входу первого ком мутационного триггера, при этом нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным входами второго коммутационного триггера второго раз ряда, нулевой выход первого коммутационного триггера второго разряда с нулевым и .единичным входами второг коммутационного триггера третьего ра ряда, а нулевой выход первого коммутационного триггера третьего разряда с нулевым входом второго коммутацион ного триггера четвертого разряда, отличающийся тем, что, с целью расширения его функциональных возможностей, в него введен второй элемент И-НЕ, причем первые три входа первого элемента И-НЕ соединены с соответствующими единичными выходами триггеров памяти второго, третьего и четвертого разрядов, а четвертый вход первого элемента И-НЕ с нулевым выходом первого коммутационного триггера первого разряда, выход первого элемента И-НЕ соединен с одним из входов второго элемента И-НЕ, а также с второй выходной шиной и с единичным входом первого коммутационного триггера первого разряда, при этом второй вход второго элемента И-НЕ, выход которого соединен с первой выходной шиной, соединен с нулевым выходом второго коммутационного триггера четвертого разряда, а единичный выход первого коммутационного триггера четвертого разряда соединен с единичным входом первого коммутационного триггера первого разряда. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 426326, кл, Н 03 К 23/24, 1972. 2.Авторское свидетельство СССР № 561299, кл. Н 03 К 23/02, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Пересчетное устройство по модулю шесть | 1980 |

|

SU924867A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Распределитель импульсов | 1980 |

|

SU884136A1 |

| Делитель частоты на девять | 1977 |

|

SU687603A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU873417A1 |

| Делитель частоты | 1976 |

|

SU561299A1 |

Авторы

Даты

1981-07-07—Публикация

1979-07-16—Подача