(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU873417A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для деления частоты импульсов на одиннадцать.

Известен делитель частоты, содержащий четыре разряда, включающих в себя триггеры памяти, коммутационны триггеры и элементы И-НЕ l.

Недостатком этого устройства является сложность.

Наиболее близким по технической сущности к предлагаемому является делитель частоты следования импульсов, содержащий четыре счетных разряда, каждый из которых содержит логический элемент И-НЕ, коммутационый триггер, вход которого соединен со входной шиной, причем единичный выход первых трех разрядов соединен с первым единичным входом коммутационного триггера тех .-ка разрядов, е ничный выход которого соединен с первым входом логического элемента И-НЕ того же разряда, а нулевой выход коммутационного триггера каждого из первых трех разрядов соединен с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти всех предыдущих

разрядов и вторым входом логического элемента И-НЕ предыдущего разряда, выходы логических элементов И-НЕ первого И второго разрядов соединены с двумя входами коммутационных триггеров соответственно второго и третьего разрядов, выход логического элемента И-НЕ третьего разряда соединен с первым единичным входом ком0мутационного триггера четвертого разряда, единичный выход которого соединен с единичным входом триггера памяти этого же разряда, с нулевым входом коммутационного триггера и со

5 вторым входом логического элемента И-НЕ третьего разряда, а нулевой выход коммутационного триггера четвертого разряда соединен с нулевыми входами всех триггеров памяти и нуле0выми входами коммутационных триггеров предыдущих разрядов, причем нулевые выходы триггера памяти и коммутационного триггера четвертого разряда соединены со входами логи5ческого элемента И-НЕ данного разряда, причем нулевые входы коммутационного- триггера данного разряда соелинены с выходами логических элементов И-НЕ второго и четвертого разрядов 2 .

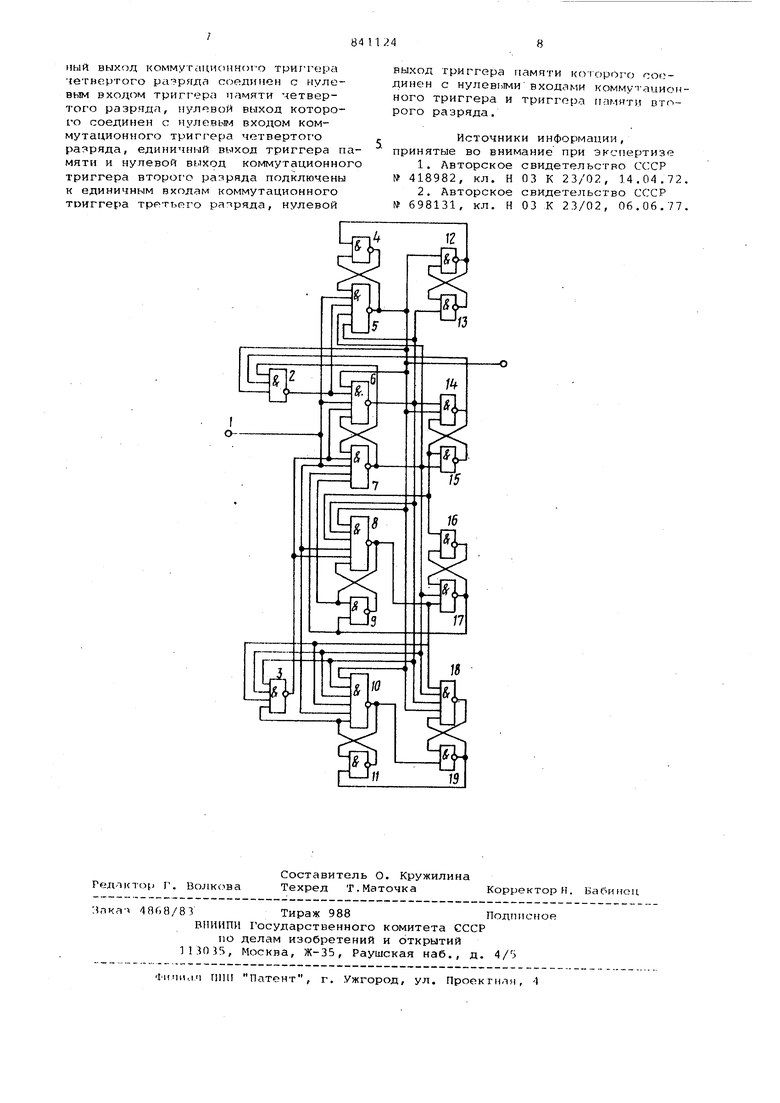

0 Недостатком известного устройства является сложность и недостаточная надежность. Цель изобретения - повышение надеж ности устройства. Поставленная цель достигается тем, что в делитель частоты следования импульсов, содержащий элементы И-НЕ и четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, нулевой вхо которого в первом и втором разрядах, единичный и нулевой входы в.третьем разряде и единичный вход в четвертом разряде соединены с входной шиной, единичный выход триггера памяти в пе вых двух разрядах соединен с единич.ным входом коммутационного триггера этого разряда, единичный выход комму тационного триггера первого разряда соединен с первым входом первого эле мента И-НЕ, выход которого подключен к нулевому входу коммутационного три гера второго разряда, нулевой выход с единичным входом триггера памяти данного разряда,нулевой выход коммутационного триггера второго разряда соединен с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационного триггера и триггера памяти первого разряда и с йторым входом первого элемента И-НЕ, нулевой выход коммутационного тригге ра третьего разряда соединен с первым входом второго элемента И-НЕ, с нулевым входом коммутационного триггера второго разряда и с нулевыми входами коммутационного триггера и триггера памяти первого разряда единич ный выход коммутационного триггера чет вертого разряда соединен с нулевыми вх дами коммутационного триггера и тригге ра памяти третьего разряда,с нулевым входом коммутационного триггера второ разряда, с нулевыми входами коммутационного триггера и триггера памяти первого разряда и с вторым входом второго элемента И-НЕ, выход которог соединен с единичным входом коммутационного триггера четвертого разряда выход первого элемента И-НЕ соединен с единичным и нулевым входами коммут ционного Триггера третьего разряда, выход второго элемента И-НЕ соединен с нулевым входом коммутационного три гера третьего разряда, единичный выход которого соединен с единичным входом коммутационного триггера четвертого разряда, с единичными входам триггеров памяти второго и третьего разрядов, с нулевыми входами коммута ционного триггера и триггера памяти первого разряда и с третьим входом первого элемента И-НЕ, нулевой выход коммутационного триггера третьег разряда соединен с единичными входам коммутационного триггера и триггера памяти четвертого разряда, с нулевым входом триггера памяти третьего разряда и с четвертым входом первого элемента И-НЕ, нулевой выход триггера памяти третьего разряда соединен с третьим входом второго элемента И-НЕ, единичный выход коммутационного триггера четвертого разряда соединен с нулевым входом триггера памяти четвертого разряда, нулевой выход которого соединен с нулевым входом коммутационного триггера четвертого разряда, единичный выход триггера памяти и нулевой выход коммутационного триггера второго разряда подключены к единичным входам коммутационного триггера третьего разряда, нулевой выход триггера памяти которого соединен с нулевыми входами коммутационного триггера и триггера памяти второго разряда. На чертеже представлена структурная схема устройства. Устройство содержит входную шину 1, элементы 2, 3 И-НЕ, элементы 4-11 И-НЕ, попарно образующие коммутационные триггеры четвертого и первого разрядов, элементы 12-19 И-НЕ, попарно образующие триггеры памяти этих же разрядов. Устройство работает следующим образом. В исходном состоянии триггеры памяти находятся в нулевом состоянии, а выходной сигнал, поступающий по входной шине 1, отсутствует и равен логическому О, В этом случае на выходах элементов 2,3,4,13,15., 17 и 19 появляется логический О , на выходах остальных элементов - логическая 1, поэтому с приходом первого входного импульса срабатывает только элемент 10, устанавливая триггер памяти первого разряда в единичное состояние. После окончания действия входного импульса, на выходе элемента 3 появляется логическая 1. С приходом второго входного импульса срабатывает элемент 8, устанавливая триггер памяти второго разрйда в единичное состояние, а триггер памяти первого разряда - в нулевое состояние. С при.ходом третьего входного импульса снова срабатывает элемент 10, устанавливая триггер памяти первого разряда в единичное состояние. По окончании действия тактового импульса на выходе элемента 3 появляется логическая 1, а поскольку и триггер памяти второго разряда находится в единичном состоянии, то элемент 7 подготовлен для срабатывания. Наличие связи с выхода элемента 8- на входы элементов 3,7,9 и 10 препятствует появлению на выходах этих элементов сигнала, равного логическому О, в момент действия входного импульса. С приходом четвертого входного импульса срабатывает элемент 7, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов - в нулевое состояние Наличие связи с выхода элемента 7 входы элементов 3,5,6,10 и 17 преп ствует появлению логического О н выходах этих элементов во время де ствия входного импульса. Сигнал, равный логическому О, с вЕЛХода элемента 14 запретит сраб тывание элемента 8 до тех пор, пок не изменит свое состояние триггер памяти третьего разряда. Аналогичн с приходом пятого входного импульс сработает элемент 10, устанавливая триггер памяти первого разряда в единичное состояние. После окончан входного сигнала на выходе элемент 3 появляется логическая 1, а поскольку на выходе элемента 2 тоже логическая., то с приходом шестого входного импульса сработает элемент 6 и триггер памяти четверто го разряда устанавливается в единич ное состояние, а триггеры памяти младших разрядов - в нулевое состоя ние. Наличие связи с выхода элемент 6 на входы элементов 2,3,5,7,8 и 10 препятствует неправильной работе делителя. Далее осуществляется счет в двоичном коде, при этом наблюдает ся следующая последовательность сос тояний триггеров памяти: 00000 10001 2, 0010 3ООН 40100 50101 61000 71001 81010 91011 101100 110000 Таким образом, видно, что с приходом десятого входного импульса в делителе устанавливается код 1100 поэтому с приходом одиннадцатого входного импульса срабатывает элеме 5 и с его выхода сигнал, равный логическому О, поступает на выход устройства и одновременно устанавли вает все триггеры памяти в нулевое состояние. Наличие связи с выхода элемента 5 на входы элементов 2,4,6 8 и 10 препятствует неправильной работе делителя. Таким образом, на одиннадцать входных импульсов схема выдает один выходной импульс, т.е. осуществляет ся деление на одиннадцать. Введение новых связей позволяет сократить количество оборудования, .уменьшить потребляемую мощность .повысить надежность работы делителя частоты. Формула изобретения Делитель частоты следования импул сов, содержащий элементы И-НЕ и четы ре разряда, каждый из которых состоит из триггера памяти и .коммутационного триггера,нулевой вход которого в первом и втором разрядах, единичный и нулевой входы в третьем разряде и единичный вход в четвертом разряде соединены с входной шиной,единичный выход триггера памяти в первых двух разрядах соединен с единичным входом коммутационного триггера этого разряда, единичный выход коммутационного триггера первого разряда соединен с первым входом первого элемента И-НЕ, выход которого подключен к нулевому входу коммутационного триггера второго разряда, нулевой выход - с единичным входом триггера памяти данного разряда, нулевой выход коммутационного триггера второго разряда соединен с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационного триггера и триггера памяти первого разряда и с вторым входом первого элемента И-НЕ, нулевой выход коммутационного триггера третьего разряда соединен с первым входом второго элемента И-НЕ, с нулевым входом коммутационного триггера второго разряда и с нулевыми входами коммутационного триггера и триггера памяти первого разряда единичный выход коммутационного триггера четвертого разряда соединен с нулевыми входами коммутационного триггера и триггера памяти третьего разряда, с нулевым входом коммутационного триггера второго разряда, с нулевыми входами коммутационного триггера и триггера памяти первого разряда и с вторым входом второго элемента И-НЕ, выход которого соединен с единичным входом коммутационного триггера четвертого разряда, отличающийся тем, что, с целью повыпения надежности устройства, выход первого элемента И-НЕ соединен с единичным и нулевым входами коммутационного триггера третьего разряда, выход второго элемента И-НЕ соединен с нулевым входом коммутационного триггера третьего разряда, единичный выход которого соединен с единичным входом коммутационного триггера четвертого разряда, с единичными входами триггеров памяти второго и третьего разрядов, с нулевыми входами коммутационного триггера и триггера памяти первого разряда и с третьим входом первого элемента И-НЕ, нуле- , вой выход коммутационного триггера третьего разряда соединен с единичными входами коммутацион-ного триггера и триггера памяти четвертого азряда, с нулевым входом триггера памяти третьего разряда и с четвертьвл входом первого элемента И-НЕ, нулевой выход триггера памями третьео разряда соединен с третьим вхоом второго элемента И-НЕ, единич-

иый выход коммутациоинотО триттера четвертого соелннен с нулевым входе м триггерг) памяти четвертого разряда, выход которого соединен с нулевьм входом коммутационного триггера четвертого разряда, единичный выход триггера памяти и нулевой В1лход коммутационного триггера второго разряда подключены к единичным входам коммутационного триггера третьего разряда, нулевой

выход триггера памяти кочорого соединен с нулевымивходами коммутационного триггера и триггера ггамяти второго разряда.

Источники информации, принятые во внимание при экспертизе

№ 418982, кл. Н 03 К 23/02, 14.04,72,

№ 698131, кл, Н 03 К 23/02, 06.06.77.

Авторы

Даты

1981-06-23—Публикация

1979-09-28—Подача