(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты | 1979 |

|

SU845291A1 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Многопрограмный делитель частоты | 1976 |

|

SU641658A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

. , 1 .

Изобретение относится к импульсной технике.

Известен делитель частоты следования импульсов, содержащий регистр сдвига, состоящий из N элементов памяти, два элемента НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИСКЛЮЧИТЕЛЬНО ИЛИ-НЕ, соединенные соответственно с. разрядами регистра сдвига 11. ,

Однако устройство характеризуется недостаточно высокой надежностью.

Наиболее близким по технической сущности к изобретению является делитель частоты, следования импульсов, содержащий элемент И-НЕ и че тыре соединенных последовательно разряда, каждый из которых содержит триггер памяти и два коммутационных триггера,первые входы каждого, из которых соединены со входной шиной, выход первого коммутационного триггера первого разряда соединен со вторыми входами коммутационных триггеров второго и третьего разрядов и вторым входом второго коммутационного триггера четвертого разряда, выход первого коммутационного триггвра второго разряда соединен с третьим и четвертым входами второго коммутационного триггера третьего разряда.

выход первого коммутационного триггера третьего разряда соединен с третьим и четвертым входами второго коммутационного триггера четвертого разряда, входы дополнительного логического элемента И-НЕ соединены с выходами второго коммутационного триггера четвертого разряда, единичный выход первого коммутационного

10 триггера которого соединен с дополнительным входом первого коммутационного триггера второго разряда, а единичный выход второго коммутационного трТ1ггера четвертого разряда

15 соединен с -дополнительным входом первого коммутационного триггера первого разряда и вторым дополнительным входом первого коммутационного триггера второго разряда 2.

Недостатком данного устройства

20 является низкая надежность.

Цель изобретения - повышение надежности работы устройства.

С этой целью делитель частоты

25 следования импульсов, содержащий четыре разряда, каждый из которых, кроме третьего, включает в себя первый и второй коммутационные триггеры и триггер памяти, нулевой вход которого соединен с единичным выходом

30

первого коммутационного триггера и с нулевым входом второго коммутационного триггера, нулевой выход которог подключен к единичному входу триггера памяти,единичный выход - к нулевому входу первого коммутационного триггера, а единичный вход - к единичному выходу триггера памяти этого же разряда,при этом третий разряд содержит триггер памяти и коммутационный триггер,нулевой выход и едничный вход которого соединены соответственно с единичным входом и единичным выходом триггера памяти этого же разряда, а к нулевому входу коммутадионного триггера третьего разряда к единичным входам всех первых и нулевым входам всех вторых коммутационных триггеров подключена входная шина, нулевой выход первого коммутационного триггера первого разряда соединен с нулевым и единичным;.вхо-. дами второго коммутационного триггера второго разряда, нулевой выход первого коммутационного триггера второго разряда соединен с нулевым и единичным входами коммутационного триггера третьего разряда, а первый и второй входы первого дополнительного элемента И-НЕ соединены с единичным и нулевым выходами второго коммутационного триггера четвертого разряда, единичный выход которого соединен с первым дополнительным единичным входом первого коммутационного триггера первого разряда, введен втброй дополнительный элемент ИНЕ, выход которого соединен с нулевь и единичным входами второго коммутационного триггера четвертого разряда нулевой выход которого соединен с первыми дополнительными нулевыми входами коммутационного триггера памяти третьего разряда и с первым Ьходом второго дополнительного элемента И-НЕ, второй вход которого соединен с единичным выходом коммутационного триггера третьего разряда, при этом единичный выход первого коммутационного триггера четвертого разряда соединен с вторым дополнительным единичным входом коммутационного триггера первого разряда и с дополнительными нулевыми входами первого коммутационного триггера и триггера памяти третьего разряда.

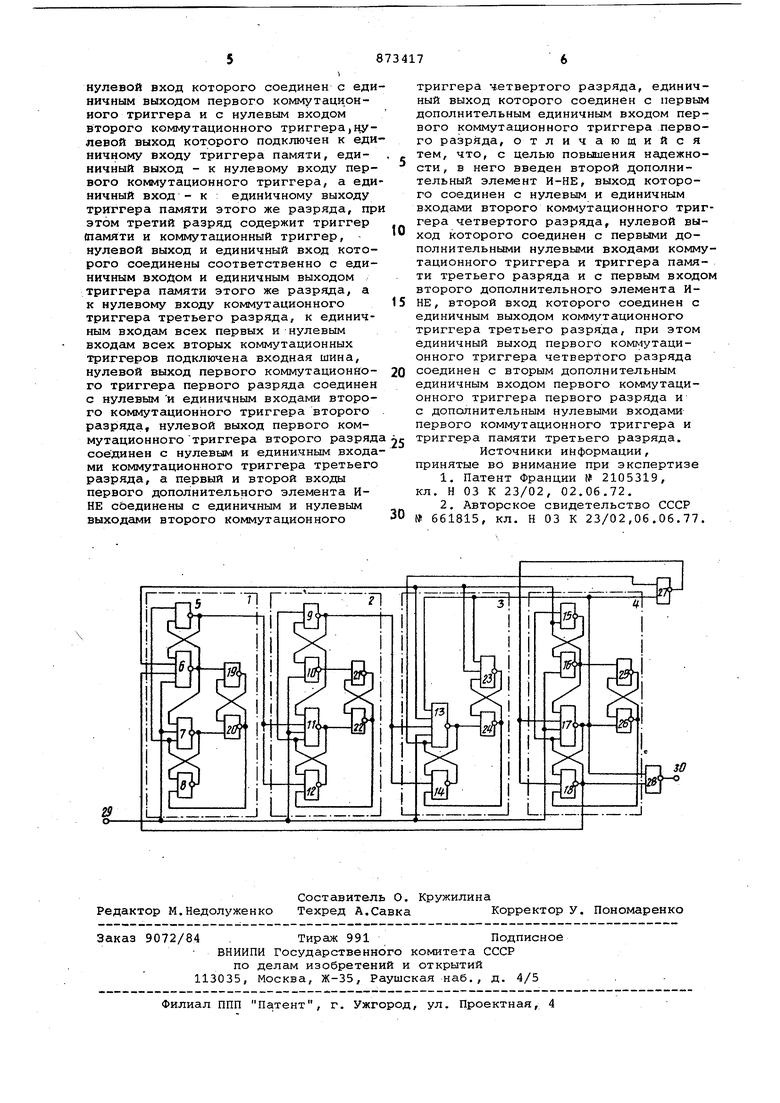

На чертеже представлена структурная схема устройства.

Оно содержит четыре разряда 1-4, комфтационные триггеры которых выполнены на элементах И-НЕ 5-18, а триггеры памяти выполнены на элементах И-НЕ 19-26, и дополнительные элементы И-НЕ 27 и 28, входную 29 и выходную 30 шины.

Устройство работает следующим образом.

В исходном состоянии триггер памяти первого разряда находится в единичном состоянии, триггеры памяти остальных разрядов - в нулевом.

Под действием сигнала в делителе осуществляется обычный -пересчет поступающих импульсов в двоичном коде С приходом седьмого по счету импульсГа на выходе логического элемента И-НЕ 7 появляется сигнал, равный ло(гическому нулю, который устанавливает триггер памяти четвертого разряда в единичное состояние, а триггер памяти третьего разряда - в нулевое состояние и который через первый дополнительный логический И-НЕ 28 .поступает на выход. Далее осуществляется обычный пересчет поступающих импульсов и с приходом четырнадцатого импульса в делителе устанавливается код 1111. После окончания четырнадцатого импульса на выходе логического элемента И-НЕ 18 появляется сигна равный логическому нулю, который через первый дополнительный логический элемент И-НЕ 28 поступают на выходную шину 30.

С приходом пятнадцатого по счету импульса открываются логические элементы И-НЕ 10 и 16, на выходе их появляются сигналы равные логическому нулю, которые устанавливают триггеры памяти, кроме первого разряда,в нулевое состояние. Одновременно прекращается формирование выходного сигнала.

Триггер памяти первого разряда свое состояние не изменяет, поскольку логический элемент И-НЕ 16 остается закрытым сначала сигналом равным логическому нулю с выхода логического элемента И-НЕ 18, а затем сигналом с выхода логического элемента И-НЕ 16. После окончания действия входного сигнала схема возвращается в исходное состояние 0001.

Таким образом, на 15 входных импульсов делитель выдает два выходных т.е. происходит деление частоты на 7,5. Кроме того, делитель позволяет осуществлять деление частоты на 15. Выходным сигналом при этом будет сигнал с выхода логического элемента ИНЕ 16.

Введение второго дополнительного логического элемента И-НЕ 27 с соответствующи1У1и связями позволяет исключить из третьего разряда делителя частоты один коммутационный триггер, что сокращает количество логических элементов и существенно повышает надежность делителя частоты.

Формула изобретения

Делитель частоты следования импульсов, содержащий четыре разряда, каждый из которых, кроме третьего, включает в себя первый и второй коммута 5 ционные триггеры и триггер памяти.

Авторы

Даты

1981-10-15—Публикация

1979-09-20—Подача