I

Изобретение относится к импульсной технике.

Известен делитель частоты, содержащий два счетчика импульсов, снабженных входными и выходными схемами, логическую схему предварительной установки коэффициента деления, состоящую из логических элементов И, ИЛИ, НЕ, управляющее устройство l.

этот делитель сложен.

Наиболее близким к предлагаемому является делитель, содержащий три логических элемента И-НЕ, четыре триггера памяти, три коммутационных триггера, выходы первого из которых соединены с первым входом первого триггера памяти и первым входом первого логи- ческого элемента И-НЕ, выход которого соединен с одним входом первого коммутационного триггера, вторым входом первого триггера памяти, первым входом второго триггера памяти и первым ВХОДОМ второго логического элемента И-НЕ, второй вход которого соединен с

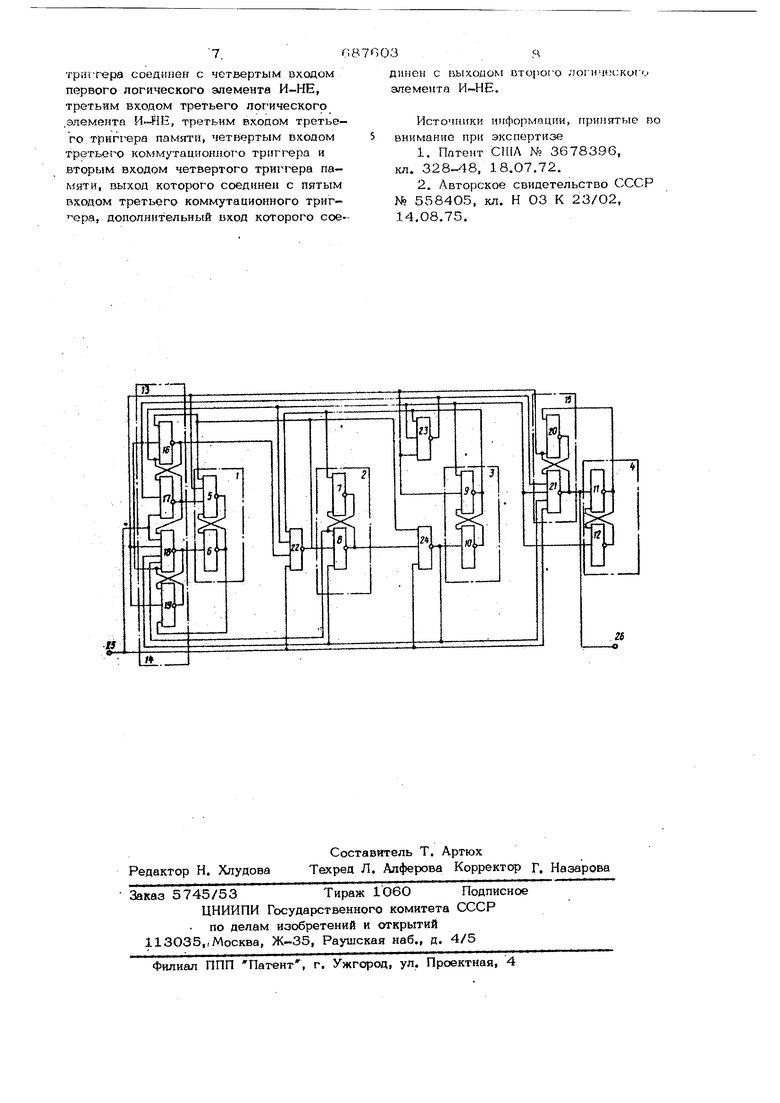

выходом -второго триггера памяти, второй вход которого соединен с вторым входом первого логического элемента И-НЕ, первым входом третьего логического элемента И-НЕ и Ш}1ходом третьего триггера памяти, первый вход которого соединен с выходом второго ncwH- ческого элемента И-НЕ, третьим вхоаом второго триггера памяти и первым входом второго коммутационного триггера, второй вход которого с вторым выходом второго триггера памяти, третий вход соединен с вторым входом первого коммутационного триггера, а четвертый вход подключен к выходу первого коммутационного триггера, третий вход которого соединен с выходом третьего ческого элемента И-НЕ и первым входом третьего коммутационного триггера, второй вход которого соединен с вторым входом третьего триггера памяти, qepвый вход четвертого триггера памяти соединен с выходной шиной и выходом третьего коммутационного триггера. Tpei ;тй b;tor.i кото|юго соояииои с троп)- ими входами первого и второго логических элементов И-НЕ, соответствугощнмн ох.одч. пг рво:о и второгО коммутагиюь гплх тригг-cpoD и входной шиной f 2 |, Однако тпкой делнгел 1 едостаточло надежен. Целью изобретения является повьшге- ние надежности. Это достигается тем, что в делителе частоты, ссаержашем тр1г лоп ческих: элемента И-НЕ, четыре триггера памяти три коммутационных трн)гера, выходы первого из которых соедине г.ы с первым входом первого тригтера памяти и пер вым входом первого логического элемента И-НЕ, выход которого соединен с одним входом первого коммутационного тригг ера, вторым входом первого тригге ра памяти, первым входом второго триггера памяти и первым входом лог-ическо- го элемента , второй вход которого соединен с выходом второго триггера па мяти, второй вход которого соединен с вторым входом первого логического элемента И-НЕ, первым входом третьего логического элемента И-НЕ и выходом третьего триггера памяти, первый вход которого соед1шен с выходом второго ло гического элемента И-НЕ, третьим входом второго триггера памяти и первым входом второго коммутационного триггера, второй вход которого соединен с вто рым выходом второго триггера памяти, третий вход соединен с вторым входом первого ко ч мутационного триггера, ,з четвертый вход подключен к выходу первого коммутационного триггера, третий вход которого соединен с выходом треть его логического элемента И-НЕ и первым входом третьего коммутационного триггера, второй вход которого соединен с вторым входом третьего триггера памя ти, первый вход четвертого триггера памяти соединен с выходной шиной и выходом третьего коммутационного триггера, третий вход .которого соединен с третьими входами первого и второго логических элементов И-НЕ, соответствующими входами первого и второго коммутационных триггеров и входной шиной, выход третьего коммутационного триппера, соединен о вторым входом третьего элемента И-4-1Е, четвертым входом первого триг гера памяти и двумя дополнительными входами второго коммутационного триггера, выход первого коммутационного триггера соединен с четвертым входом первого ЛО1 ическосо .: 1смкчгп ll-Hli, TppTi.iHM lixoaoM третьего логпчоского элсмоитг К-НГг, третьим входом третьего тр и-1-ор,ч гшмяти, fOTiiepTF.iM входом TpOTijero коммутан юнио1о тригге 1а , и вторым входом чоггюртого трИ1гера памяти, вьход соединен с пятым входом трс.тьего коммутационого три1; ера, дополнительный вход которого соединен с выходом второго ло1ического элемента . На чертеже приведена структурная элокт 1ическая схема предлагаемого делителя. Делитель содержит гетыре триггера памяти 1--4, выполненных на логических элементах И-НЕ 5-12, коммутационные триггеры 13 - 15, выполненные на логических элементах И-НЕ 16 - 21, и логические элементы И-НЕ 22- 24. Входной сигнал подается на входную шину 25. Выходной сигнал снимается с выхода 26. Устройство работает следующим образом. В исходном состоянии все триггеры памяти 2 - 4 находятся в нулевом состоянии, а тактирующий сигнал, поступающий на шину 25 отсутствует (равен логическому нулю). В этом случае на выходах логических элементов И-НЕ 5, 7, 9, 11, 18, 10, 21, 22, 24 будет сигнал, равный логической единице, на выходах остальных логических элементов И-НЕ будет сигнал, равный логическому нулю. С приходом первого входного импульса открывается логический элемент И-НЕ 18 и на его выходе появляется сигнал, равный логическому нулю, который устанавливает триггер памяти 1 в единит шое состояние. Наличие связи с выхода элемента И-НЕ 18 на вход элемента И-НЕ 10 препятствует появлению на выходе логического элемента И-НЕ 19-сигнала, равного логическому нулю в момент действия входного импульса. По окончании действия вхоаного импульса на выходе Логического элемента И-НЕ 19 появляется, сигнал, равный логическому нулю, а на выходе логического элемента И-НЕ 16 - сигнал, равный логической единице. Поэтому с приходом второго входного импульса логический нуль появляется на выходе логического элемента И-НЕ 22, который устанавливает второй триггер памяти 2 в единичное состояние, а первый триггер памяти 1 в нулевое состояние. Наличие связей

с- пыхопд логичсского элсмопта M-JIE 22 па входы логических элсмсптор, И-Н 16 и 24 Г1 юпятствуот появлению на их выходах , равного логическому нулю в KfOMOHT- действия тактируюшег-о сигнала. Но окончании действия второго пходного импульса на выходе логического эломсита И-ИЕТ 16 появляется сигна paBHi iH ло1-ическому нулю и поэтому с приходом третьего входного импульса логический нуль пожзляется на выходе логического элемента И-НЕ 24, устанafiливaя третий триггер памяти 3 в единичное состояние. Сигнал, равный ло1ическому нулю, с нулевого выхода третьего триггера памяти 3 устанавливает в нулевое состояние второй тригге памяти 2. Наличие связей с выхода логического элемента И-НЕ 24 на входы логических элементов И-НЕ 8, 18, 21 препятствует появлению на их выходах логического нуля в момент действия входного сигнала. С приходом четвертого входного импульса открывается логический элемент И-НЕ 18, устанавливая первый триггер памяти 1 в единичное состояние. По окончании действия входного импульса подготовленным к срабатыванию оказывается логический элемент И-НЕ 17, поскольку на выходах логических элементов И-НЕ 16 и 23 - логическая единица. Следовательно, с приходом пятого входного импульс на выходе логического элемента И-НЕ 17 появляется сигнал, равный логическому нулю, который устанавливает пердый и третий триггеры памяти в нулевое состояние, а четвертый триггер памя- ти 4 - в единичное состояние.

Далее аналогичным образом с приходом шестого входного импульса первый триггер памяти устанавливается в единичное состояние, с приходом седьмого входного импульса второй триггер памяти устанавливается в единичное состояние, а первый триггер памяти - в нулевое состояние. С приходом восьмого входного импульса третий триггер памяти устанавливается в единичное состояние, а второй триггер памяти Устанавливается в нулевое состояние. По окончании действия восьмого входного импульса подготовленным к срабатыванию оказывается логический элемент И-НЕ 21, поэтому с приходом девятого входного импульса на выходе логического элемента И-НЕ 21 появляется сигнал, равный логическому нулю,

который поступает на выход 26 и вознращает делитель в исходное состояние, устана -и1ипая триггеры памяти в нулевое состояние.

Формула изобретения

Делитель частоты на девять, содержащий три логических элемента И-НЕ, четыре триггера памяти, три коммутационных триггера, выходы первого из которых соединены с первым входом первого триггера памяти и первым входом первого логического элемента И-НЕ, выход которого соединен с одним входом первого коммутационного триггера, вторым входом первого триггера памяти, первым входом второго триггера памяти и первым входом второго логического элемента И-ЛЕ, второй вход которого соединен с выходом второго триггера памяти, второй вход которого соединен с вторым входом первого логического элемента И-НЕ, первым входом третьего логического элемента И-НЕ и выходом .третьего триггера памяти, первый вход которого соединен с выходом второго логического элемента И-НЕ, третьим входом второго триггера памяти и первым входом второго коммутационного триггера, второй вход которого соединен с вторым входом второго триггера памяти, третий вход соединен с вторым входом первого коммутационного триггера, а четвертый вход подключен к выходу первого коммутационного триггера, третий вход которого соединен с выходом третьего логического элемента И-НЕ и первым входом третьего коммутационного триггера, второй вход которого соединен с вторым входом третьего триггера памяти, первый вход четвертого триггера памяти соединен с выходной шиной и выходом третьего коммутационного триггера, третий вход которого соединен с третьими входами первого и второго логических элементов И-НЕ, соответствующими входами первого и второго коммутационных триггеров и входной шиной, отл ичающийся тем, что, с целью 7ювышения надежности, выход третьего ком 1утационного триггера соединен с вторым входом третьего элемента И-НЕ, четвертым входом первого триггера памяти и двумя дополнительными входами второго коммутационного триггера, выход первого коммутационного

триг-гера соединен с четвертым входом первого логического элемента И-НЕ, третьим Входом третьего логического .элемента И.41Е, третьим входом третьего триггера памяти, четвертым входом третьего коммутациошют о триггера и вторым входом четвертого триггера памяти, выход которого соединен с пятым входом третьего коммутационного триг ра, дополнительный вход которого соединен с выходом DTOjlOrO ЛОГИШСКОГи

элемента И-НЕ.

Источники информации, нринэт-ые во внимание при экспертизе

1.Патент США № 3678396, кл. 328-48, 18.07,72,

2.Авторское свидетельство СССР № 558405, кл. Н 03 К 23/02, 14.О8.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты | 1979 |

|

SU845291A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Многопрограммный делитель частоты | 1980 |

|

SU924866A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты импульсов на 10 | 1978 |

|

SU746943A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

Авторы

Даты

1979-09-25—Публикация

1977-07-06—Подача