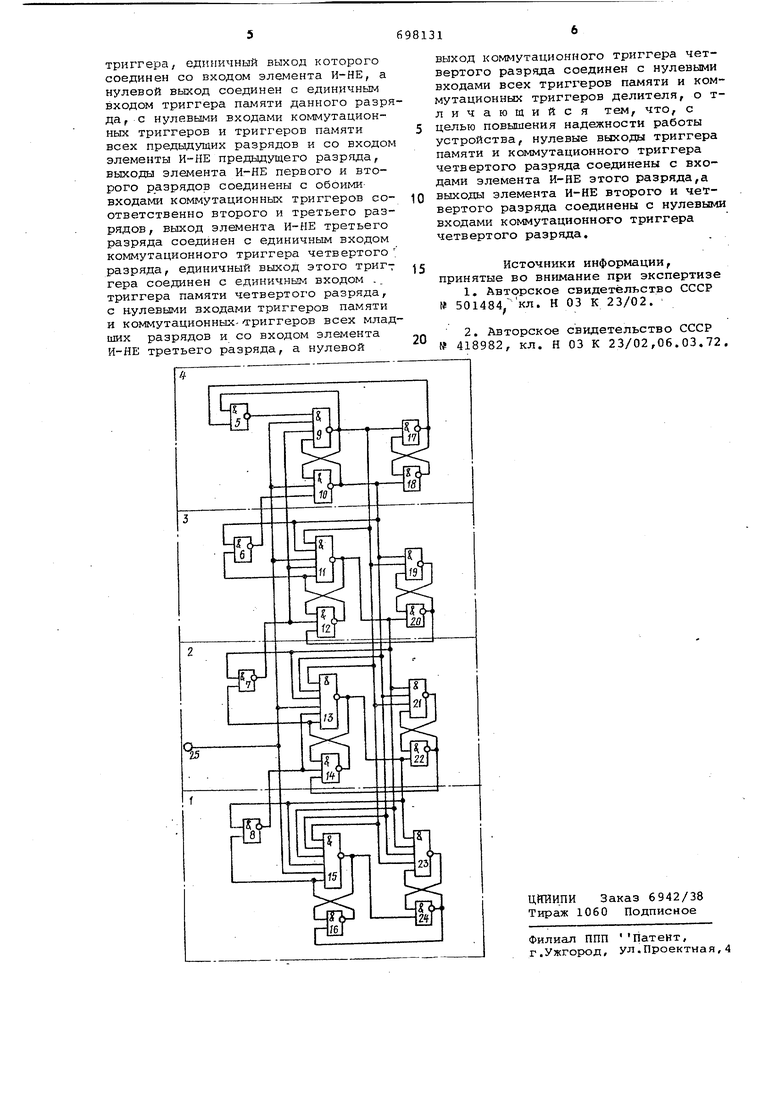

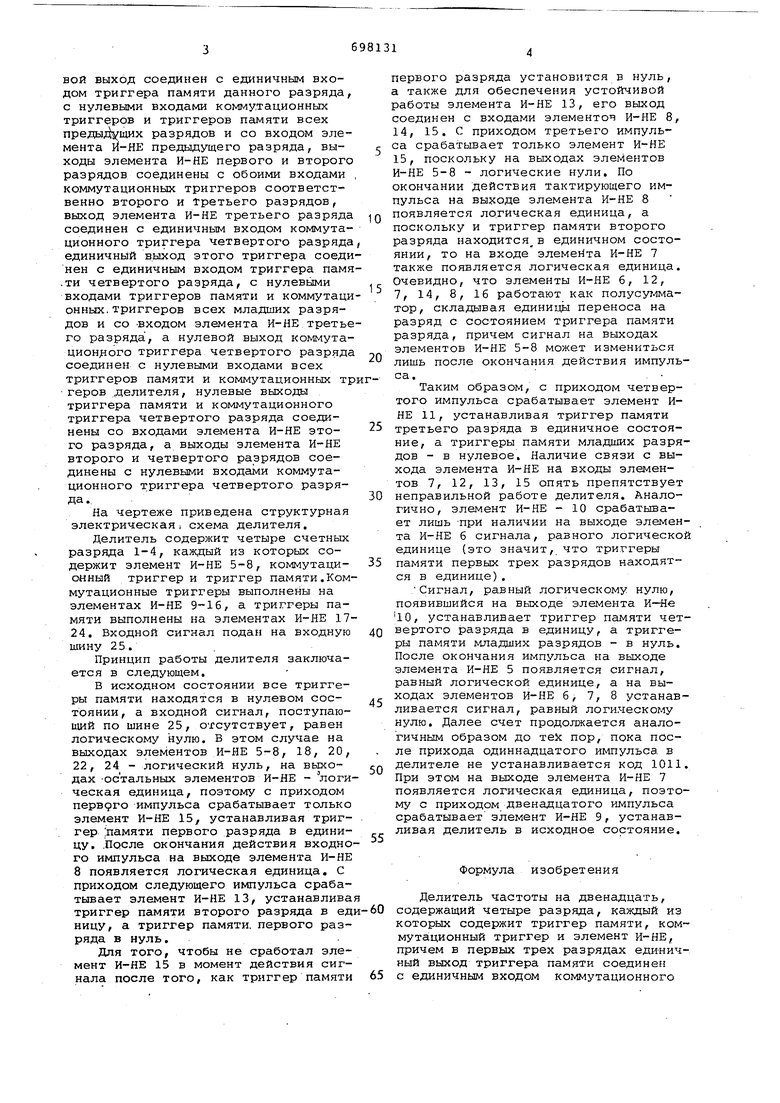

Изобретение относится к импульсной технике. Известен делитель частоты импульсов., содержащий пять счетных разрядов, каждый из которых содержит триг геры, логические элементы И, логический элемент ИЛИ и логические элементы НЕ 1j , Недостатком такого делителя является сложность и недостаточное быстродей-твие, Наиболее близким по технической сущности к предлагаемому изобретению является делитель частоты ИМПУЛЬСОВ, содержащий-четыре разряда, каждый : из которых содержит триггер памяти, коммутационный триггер и элемент ИНЕ, причем в первых трех разряд;ах единичный выход триггера памяти соединен с единичным входсм когФ утацион ного триггера, единичный выход которого соединен со входом элемента ИНЕ, а нулевой выход соединен с единичным входом триггера памяти данного разряда, с нулевыми входами комму тационных триггеров и триггеров памя ти всех предыдущих разрядов и со вхо дом элемента И-НЕ предыдущего разряда, выходы элемента Н-НЕ первого и вторето разрядов соединены с сбоили входами комг-1утационнык триггеров соответственно второго и третьего разрядов , выход элемента И-НЕ третьего разряда соединен с-.единичным входом коммутационного триггера четвертого разряда, единичный выход этого триггера соединен с единичным входом триггера памяти четвертого разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех младших разрядов и со входо -. элемента И-НЕ третьего разряда, а нулевой выход коммутационного триггера четвертого разряда-соединен с нулевыми входами всех триггеров памяти и коммутационных триггеров делителя 2. Однако и этот делитель частоты недостаточно надежен. Целью изобретения является повышение надежности работы устройства. Цель достигаетсятем,что делитель частоты на двенадцать, содержащий четыре разряда, каждый из которых содержит триггер памяти, коммутационный триггер и элемент И-НЕ, причем в первых трех разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соедине.н со входом элемента И-НЕ,.а нулевой выход соединен с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров Пс1мяти всех предыд ущих разрядов и со входом элемента Й-НЕ предыдущего разряда, выходы элемента И-НЕ первого и второго разрядов соединены с обоими входами коммутационных триггеров соответственно второго и Третьего разрядов, выход элемента И-НЕ третьего разряда соединен о единичным входом коммутационного триггера четвертого разряда единичный выход этого триггера соеди нен с единичным входом триггера памя .ти четвертого разряда, с нулевыми входами триггеров памяти и коммутаци онных, триггеров всех младших разрядов и со -входом элемента И-НЕ. третье го разряда , а нулевой выход коммутациoн oгo триггера четвертого разряда соединен с нулевыми входами всех триггеров памяти и коммутационных тр геров делителя, нулевые выхода триггера памяти и коммутационного триггера четвертого разряда соединены со входами элемента И-НЕ этого разряда, а выходы элемента И-НЕ второго и четвертого разрядов соединены с нулевыми входами коммутационного триггера четвертого разряда.. . На чертеже приведена структурная электрическая, схема делителя. Делитель содержит четыре счетных разряда 1-4, каждый из которых содержит элемент И-НЕ 5-8, коммутационный триггер и триггер памяти.Ком мутационные триггеры выполнены на элементах И-НЕ 9-16, а триггеры памяти выполнены на элементах И-НЕ 17 24. Входной сигнал подан на входную шину 25. Принцип работы делителя заключается в следующем. В исходном состоянии все триггеры памяти находятся в нулевом соетоянии, а входной сигнал, поступающий по шине 25, отсутствует, равен логическому нулю. В этом случае на выходах элементов И-НЕ 5-8, 18, 20, 22, 24 - логический нуль, на выходах-остальных элементов И-НЕ ческая единица, поэтому с приходом первфго импульса срабатывает только элемент И-НЕ 15, устанавливая триггер :памяти первого разряда в единицу, .После окончания действия входно го импульса на выходе элемента И-НЕ 8 появляется логическая единица, С приходом следующего импульса срабатывает элемент И-НЕ 13, устанавлива триггер памяти второго разряда в ед ницу, а триггер памяти, первого разряда в нуль. Для того, чтобы не сработал элемент И-НЕ 15 в момент действия сигнала после того, как триггер памяти первого разряда установится в нуль, а также для обеспечения устойчивой работы элемента И-НЕ 13, его выход соединен с входами элементов И-НЕ 8, 14,15. С приходом третьего импульса срабатывает только элемент И-НЕ 15,поскольку на выходах элементов И-НЕ 5-8 - логические нули. По окончании действия тактирующего импульса на выходе элемента И-НЕ 8 появляется логическая единица, а поскольку и триггер памяти второго разряда находится в единичном состоянии, то на входе элемента И-НЕ 7 также появляется логическая единица. Очевидно, что элементы 6, 12, 7, 14, 8, 16 работают как полусутФ1атор, складывая единицы переноса на разряд с состоянием триггера памяти разряда, причем сигнал на выходах элементов И-НЕ 5-8 может измениться лишь после окончания действия импульса. Таким образом, с приходом четвертого импульса срабатывает элемент ИНЕ 11, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов - в нулевое. Наличие связи с выхода элемента И-НЕ на входы элементов 7, 12, 13, 15 опять препятствует неправильной работе делителя. Аналогично, элемент И-НЕ - 10 срабатывает лишь -при наличии на выходе элемента И-НЕ 6 сигнала, разного логической единице (это значит, что триггеры памяти первых трех разрядов находятся в единице). .Сигнал, равный логическому нулю, появившийся на выходе элемента И-Не 10, устанавливает триггер памяти четвертого разряда в единицу, а триггеры памяти младших разрядов - в нуль. После окончания импульса на выходе элемента И-НЕ 5 появляется сигнал, равный логической единице, а на выходах элементов И-НЕ б, 7, 8 устанавливается сигнал, равный логическому нулю. Далее счет продолжается аналогичным образом до тех пор, пока после прихода одиннадцатого импульса в делителе не устанавливается код 1011. При этом на выходе элемента И-НЕ 7 появляется логическая единица, поэтому с приходом двенадцатого импульса срабатывает элемент И-НЕ 9, устанавливая делитель в исходное состояние. Формула изобретения Делитель частоты на двенадцать, содержащий четыре разряда, каждый из которых содержит триггер памяти, коммутационный триггер и элемент И-НЕ, причем в первых трех разрядах единичный выход триггера памяти соединен с единичным входом коммутационного

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Двоично-десятичный счетчик | 1974 |

|

SU506131A1 |

Авторы

Даты

1979-11-15—Публикация

1977-06-06—Подача