(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНОДЕСЯТИЧНЫЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1439745A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU637808A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода с масштабированием | 1980 |

|

SU888105A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении пре образователей кодов. Известен преобразователь двоичного кода в двоично-десятичный, содержащий регистр двоичного числа, распределитель импульсов, шифратор, дво ично-десятичный сумматор, элементы И первый вход каждого из которых соеди нен с соответствующим выходом регист ра двоичного числа, а выход с соответствующим входом шифратора, выходы которого соединены со входами двоично-десятичного сумматора . Недостаток такого устройства состоит в низком быстродействии, связанном с последовательным опросом всех разрядов двоичного числа. Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоичного кода в двоично-десятичный содержащий регистр двоичного числа, шифратор, двоично-десятичный суммато входы которого соединены с соответст вующими выходами шифратора, распределитель импульсов и группы элементов И, выходы которых соединены с соответствующими входами шифратора/ первые входы элементов И каждой группы соединены с соответствующим выходом распределителя импульсов, а вторые входы элементов И каждой группы соединены с выходами тех разрядов регистра,двоичного числа, значение весов которых не содержит единиц в одних и тех же разрядах , последний выход распределителя импульсов является управляющим выходом преобразователя 2j. Недостатком этого преобразователя является также относительно низкое быстродействие, связанное с тем, что количество тактов опроса постоянно и не зависит от преобразуемого двоичного числа, так как распределитель импульсов генерирует последовательность импульсов с интервалами, рассчитанными на максимально возможное преобразуемое число.. Поэтому коды, представляемые малымколичеством двоичных разрядов, преобразуются неоправданно медленно. Цель изобретения - повышение .быстродействия . Для достижения указанной цели в преобразователь двоичного кода в двоично-десятичный, содержащий регистр двоичного числа, шифратор, двоичнодесятичный сукматор, входы которого соединены с соответствующими выходами шифратора, распределитель импульсов и группы элементов И, выходы которых соединены с соответствующими входами шифратора, первые входы элементов И каждой группы соединены с соответствующим выходом распределителя импульсов, а вторые входы элементов И каждой группы с.оединены с выходами тех разрядов регистра двоичного числа, значение весов которых не содержит единиц в одних и тех же разрядах д воично-десятичного числа, последний выход распределителя импульсов является управлянмцим выходом преобразователя, введена дополнительная группа из (п-1) элементов ИЛИ, где п - число групп элементов ИЛИ, а распределитель импульсов содержит последовательно соединенные генератор одиночных импульсов, (п-1) блок управляемой задержки и элемент задержки, выход которого является последним выходом распределителя импульсов, входы i-го (i 1,,.,,п-1) элемента ИЛИ дополнительной группы соединены со вторыми входами элементов И (i + + 1)-ой группы, а выход i-ro элемента И дополнительной группы соединен с управляющим входом i-ro блока управляемой, задержки.

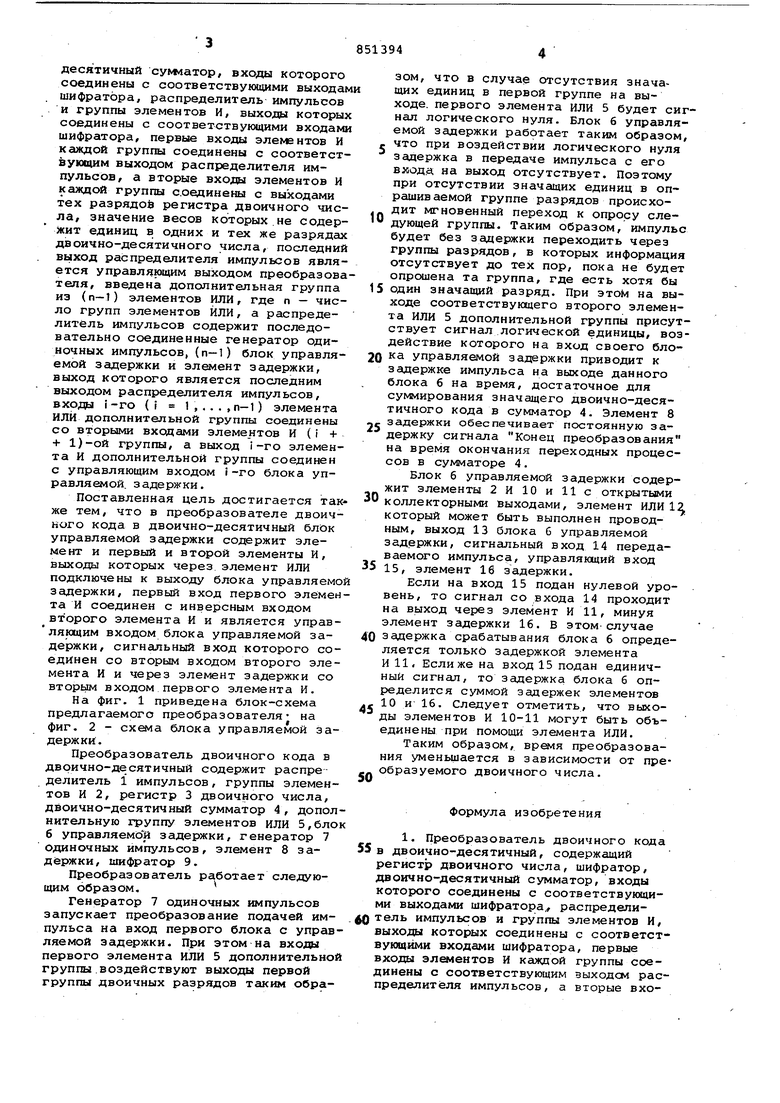

Поставленная цель достигается также тем, что в преобразователе двоичного кода в двоично-десятичный блок управляемой задержки содержит элемент и первый и второй элементы И, выходы которых через элемент ИЛИ подключены к выходу блока управляемой задержки, первый вход первого элемента И соединен с инверсным входом второго элемента И и является управляющим входом блока управляемой задержки, сигнальный вход которого соединен со вторым входом второго элемента И и через элемент задержки со BTOpbiM входом первого элемента И.

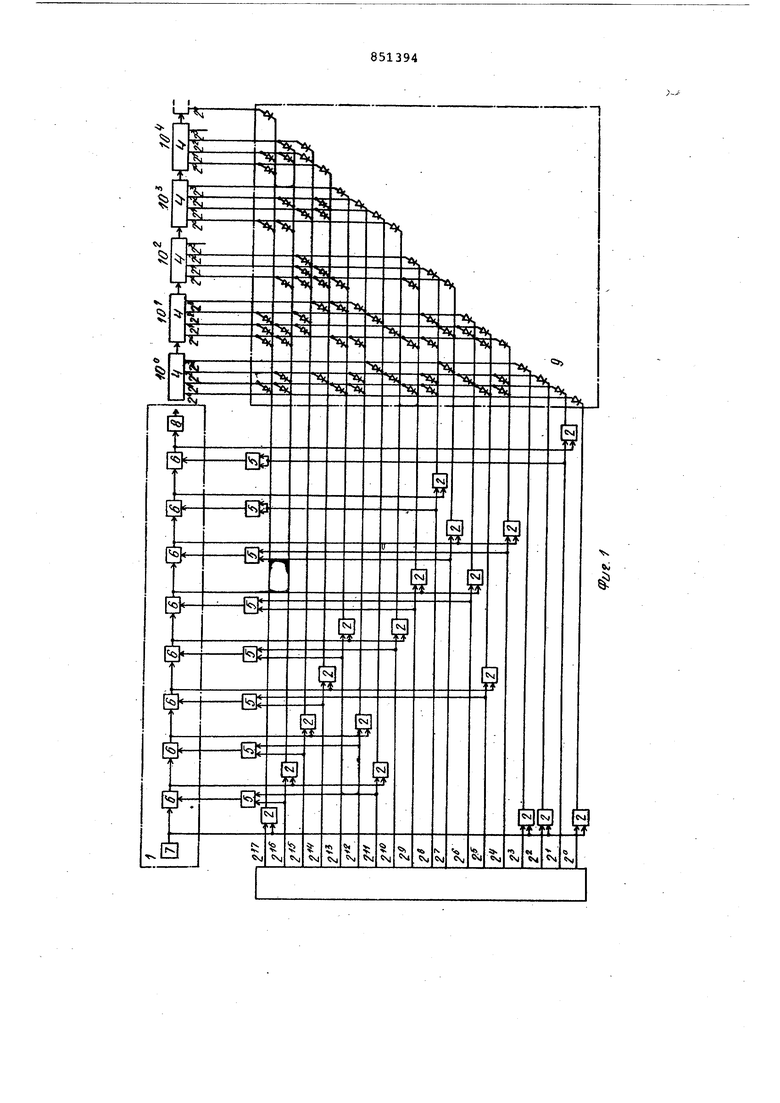

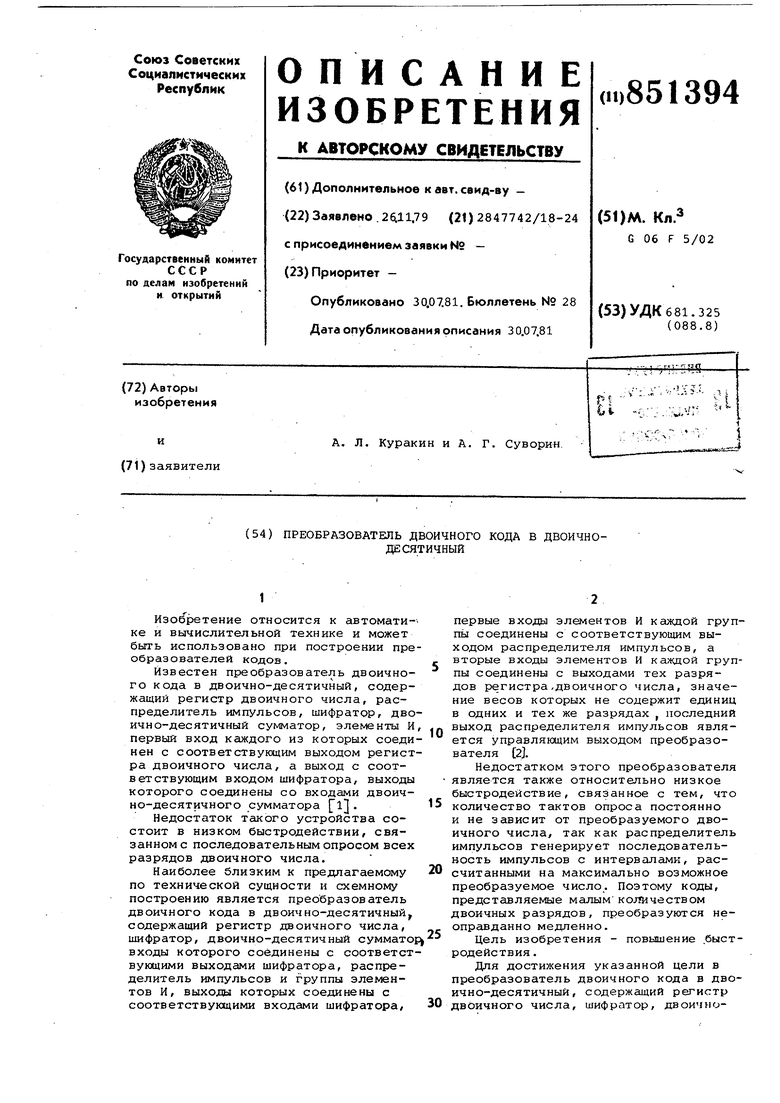

На фиг. 1 приведена блок-схема предлагаемого преобразователя- на фиг. 2 - схема блока управляемой задержки.

Преобразователь двоичного кода в воично-десятичный содержит распре елитель 1 импульсов, группы элементов И 2, регистр 3 двоичного числа, воично-десятичный сумматор 4, дополнительную группу элементов ИЛИ 5,блок 6 управляемо задержки, генератор 7 одиночных импульсов, элемент 8 заержки, шифратор 9.

Преобразователь работает следуюим образом.

Генератор 7 одиночных импульсов запускает преобразование подачей им- , пульса на вход первого блока с управяемой задержки. При этом на входы ервого элемента ИЛИ 5 дополнительной руппы воздействуют выходы первой руппы двоичных разрядов таким образом, что в случае отсутствия значащих единиц в первой группе на выходе, первого элемента ИЛИ 5 будет сигнал логического нуля. Блок б управляемой задержки работает таким образом, что при воздействии логического нуля задержка в передаче импульса с его вход.д на выход отсутствует. Поэтому при отсутствии значащих единиц в опрашиваемой группе разрядов происходит мгновенный переход к опросу следующей группы. Таким образом, импульс будет без задержки переходить через группы разрядов, в которых информация отсутствует до тех пор, пока не будет опрошена та группа, где есть хотя бы один значащий разряд. При этом на выходе соответствующего второго элемента ИЛИ 5 дополнительной группы присутствует сигнал логической единицы, воздействие которого на вход своего блока управляемой задержки приводит к задержке импульса на выходе данного блока 6 на время, достаточное для суммирования значащего двоично-десятичного кода в сумматор 4. Элемент 8 задержки обеспечивает постоянную задержку сигнала Конец преобразования на время окончания переходных процессов в сумматоре 4,

Блок б управляемой задержки содержит элементы 2 И 10 и 11 с открытыми коллекторными выходами, элемент ИЛИ 12 который может быть выполнен проводным, выход 13 блока 6 управляемой задержки, сигнальный вход 14 передаваемого импульсу, управляющий вход 15, элемент 16 задержки.

Если на вход 15 подан нулевой уровень, то сигнал со входа 14 проходит на выход через элемент И 11, минуя элемент задержки 16. В этом-случае задержка срабатывания блока 6 определяется только задержкой элемента И 11, Если же на вход 15 подан единичный сигнал, то задержка блока 6 определится суммой задержек элементов 10 и 16. Следует отметить, что выходы элементов И 10-11 могут быть объединены при помощи элемента ИЛИ.

Таким образом, время преобразования уменьшается в зависимости от преобразуемого двоичного числа.

Формула изобретения

7

№

ISL

Fok14;

h«iKf

kskCvj

Nj

«4J

Ч

,

«

4;

S

Ч(

«J

3 «M

«

«SI

N

W

п

- p

I-LyI T

//

in 15 fPu 2.

Авторы

Даты

1981-07-30—Публикация

1979-11-26—Подача