Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении, преобразователей кодов,

Цель изобретения - упрощение преобразователя.

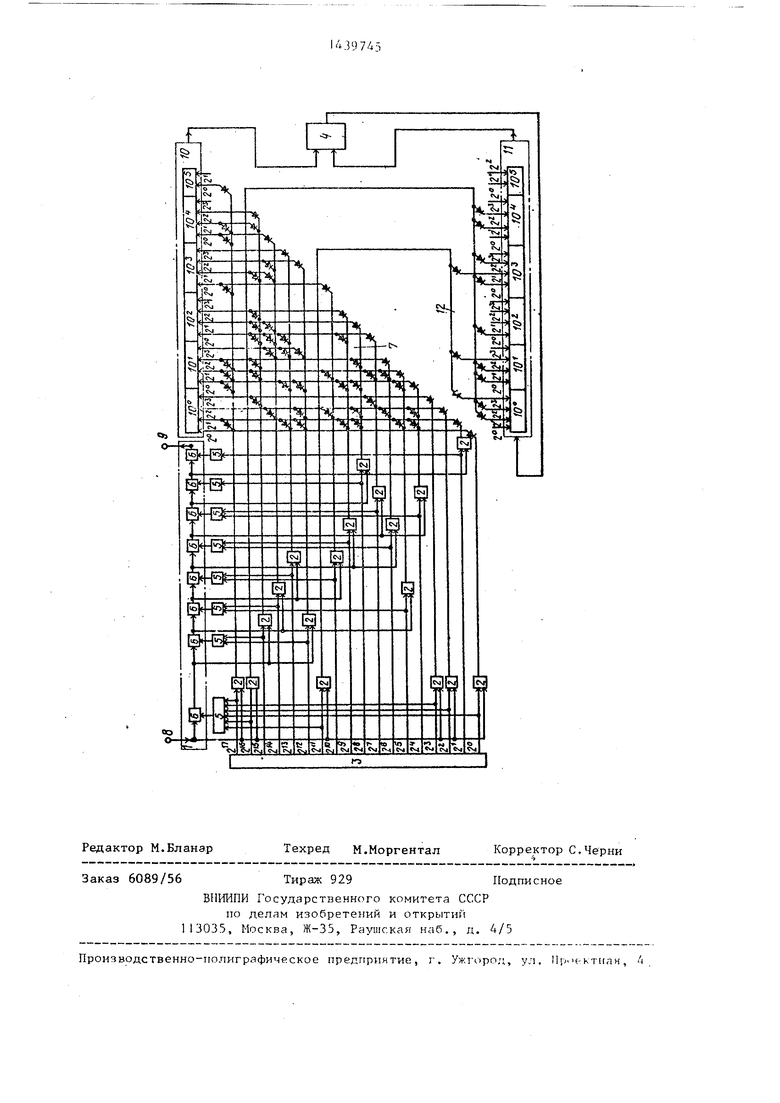

На чертеже изображена структурная схема преобразователя.

Преобразователь содержит распределитель 1 импульсов, группы элементов И 2, входной регистр 3, последовательный двоично-десятичньм сумматор 4, Группу элементов ИЛИ 5, элементы 6 управляемой задержки -распределите- ля 1 импульсов, первый шифратор 7, вход 8 пуска преобразователя, выход 9 конда преобразования, регистр 10 слагаемого, регистр 11 суммы, второй шифратор 12.

Предлагаемый преобразователь работает следующим образом.

Рассмотрим сначала работу устройства при условии, что во всех разрядах регистра двоичного числа 3 имеются значащие единиды.

В этом случае после поступления на вход 8 импульса пуска преобразователя элементы И 2 первой группы оказываются открытыми и на их выхо- дах появляются импульсные сигналы, которые пост упают на вход первого шифратора 7. Импульсные сигналы с выхода шифратора 7 в виде двоично- десятичного кода, который соответст- вует сумме двоичных разрядов, поступающих с выходов первого, четвертого пятого и шестог О элементов И 2 первой группы, параллельно записываются в регистр 10 слагаемого. Импульсные сигналы с выхода шифратора 12 также в виде двоично-десятичного кода, ко- .торый соответствует сумме двоичных разрядов, поступающих с выходов второго и третьего элементов И 2 первой группы, параллельно записываются в регистр 11 суммы.

Таким образом, после окончания импульса пуска в регистрах слагаемого 10 и суммы 11 оказываются записанны- ми двоично-десятичные эквиваленты, соответствующие разрядам первой группы входного регистра 3.

Одновременно сигнал с выхода первого элемента ИЛИ 5 группы воздейст-лует на первьй элемент 6 управляемой задержки так, что вызывает задержку импульса на выходе этого элемента на время, требуемое для суммирования

данных, записанных в регистрах слагаемого 10 и суммы 11, которое равно Т Nt, где N - количество разрядов в регистре слагаемого (суммы), Т - период тактовой частоты, подаваемой на регистры.

При поступлении тактовых сигналов |На регистры слагаемого 10 и суммы 11 в последовательном двоично-десятичном сумматоре 4 осуществляется потет- радное сложение данных, которые записаны в регистрах 10 и 11. С выхода последовательного двоично-десятичного сумматора 4 результат этого сложения вновь записывается в регистр 11 суммы. Задержанный импульс с выхода первого элемента 6 управляемой задержки опрашивает разряды входного регистра 3, соединенные с элементами И 2 второй группы. С выхода элементов И 2 второй группы импульсные сигналы поступают на шифратор 7, который преобразует эти сигналы, соответствующие коду разрядов входного регистра 3, в эквивалентный двоично-десятичный код, который параллельно записывается в регистр 10 слагаемого. Сигнал - с выхода второго элемента ИЛИ 5 группы обеспечивает задержку прохождения сигнала через второй элемент 6 управляемой задержки. За время этой задержки осуществляется второй цикл преобразования, а именно суммирование данных, находящихся в регистрах слагаемого 10 и суммы 11. Результат суммирования вновь записывается в регистр 11 суммы.

Аналогичным образом происходит преобразование остальных разрядов входного регистра 3 по мере прохождения импульса пуска через элементы 6 упр авля емой з аде ржки.

Таким образом, при появле1ши импульса на выходе последнего элемента 6 управляемой задержки в регистре 11 суммы оказывается записанным число в двоично-десятичном коде, которое является эквивалентом двоичного числа, записанного во входном регистре 3.

В случае, если в коде соответствующих разрядов входного регистра 3, связанных с определенной группой элементов И 2, отсутствуют значащие единицы, то в этом случае элементы И 2 соответствующей группы оказываются закрытыми и на их выходе отсутствуют импульсные сигналы.

В то тхе время, на выходе элемента ИЛИ 5 соответствующей группы под воздействием нулевых разрядов входного регистра 3 имеется сигнал логического О и соответствуюищй элемент 6 управляемой задержки распределителя 1 импульсов пропускает импульс с входа на выход без задержки.

Таким образом, происходит мгновенный переход к опросу следующей группы разрядов входного регистра 3.

Далее также импульс без задержки проходит через соответствующий элемент 6 управляемой задержки распределителя импульсов первой группы разрядов входного регистра 3, в которой отсутствуют значащие единицы, до тех пор, пока не опрошена та группа, где есть хотя бы одна значащая единица. Работа устройства в этом случае аналогична описанной.

Двоично-десятичный сумматор, который применен в известном преобразователе, осуществляет преобразование путем сложения с коррекцией двоично- десятичных чисел по тетрадам и последовательного сдвига (переноса) в следующий по старшинству двоично-десятичный сумматор на тетраду, т.е. преобразование осуществляется последовательно от тетрады к тетраде. В результате преобразования внутри тетрады может производиться коррекция. Если в какой-либо тетраде происходит перенос, то к ней добавляют число шесть, чтобы компенсировать разницу

0

в весах разрядов. Благодаря этому достигается правильное значе ше двоично-десятичного числа. Однако оно может еще содержить псевдотетрады. Поэтому проверяют, получилось ли в данной тетраде число больше девяти. Если это так, то для ликвидации псевдотетрады также прибавляют число шесть. Возникающий при этом перенос, как и обычный, последовательно передается в следукнцую по старшинству тетраду.

В предлагаемом преобразователе чис- 5 ло циклов преобразования всегда равно числу групп, содержащих значащие еди ницы в разрядах числа, записанного в регистр двоичного числа. Время преобразования tnj предлагаемого преобразователя

0

tnj К Т,

где К - число групп двоичных разрядов, в которых есть знача

щие единицы; Tij.- время преобразования одной

группы двоичных разрядов. Таким образом, в предлагаемом преобразователе, количество циклов преоб- разования на один меньше, чем в известном.

Выигрьш быстродействия имеет место, если в первой группе разрядов регистра двоичного числа имеются зна- чащие единицы.

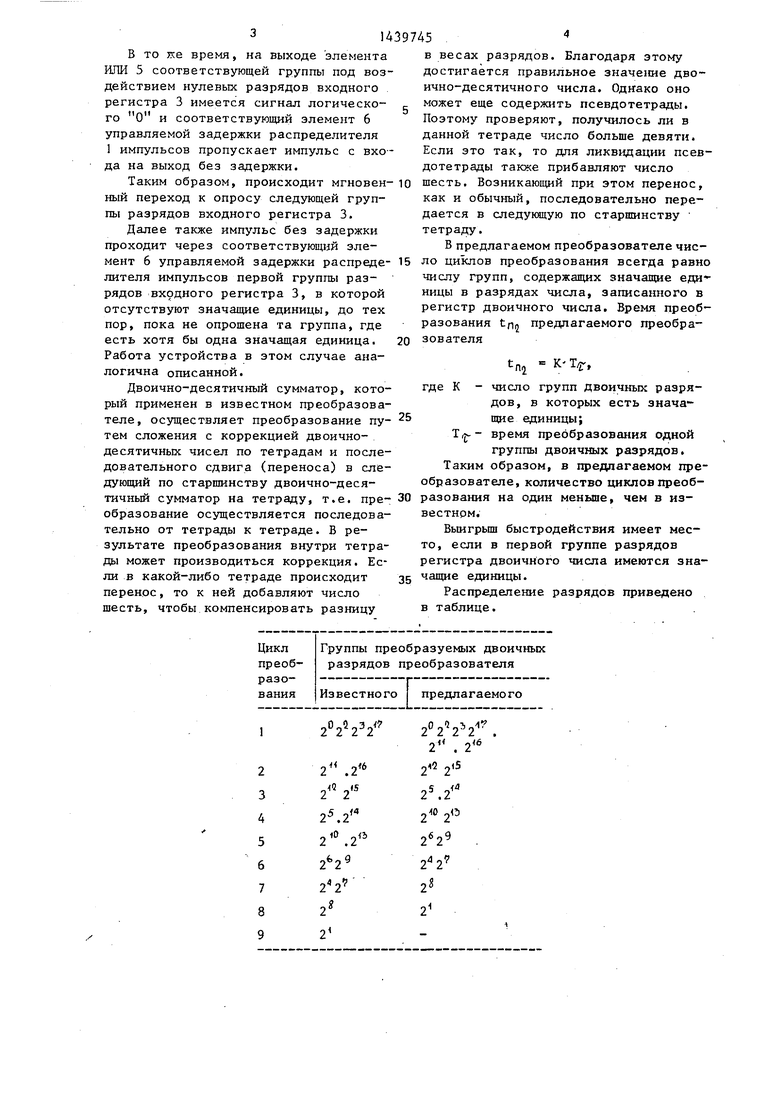

Распределение разрядов приведено в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоичного кода в двоично-десятичный масштабированный код | 1978 |

|

SU767750A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU637808A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1078422A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1985-06-03—Подача