(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1976 |

|

SU616629A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммная управляющая система | 1989 |

|

SU1631542A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1290316A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Многопрограммное устройство управления | 1984 |

|

SU1231501A1 |

1

Изобретение относится к вычислительной технике, в частности к устройствам управления цифровых вычислительных машин.

Для повышения быстродействия цифровых вычислительных машин, использующих микропрограммный принцип управления, применяются устройства управления с переменной длительностью такта. При этом длительность К-го такта

Т max (t , t , . . . , t) ,

где t - - длительность i-й микрооперации, выполняемой в К-м такте.

Известно устройство управления, содержащее блок памяти, блок формирования выходных сигналов, блок формирования сигналов возбуждения памяти, блок формирования кодов временных интервалов, управляемый генератор импульсов I .

Недостаток устройства - низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее адресный регистр, блок памяти микропрограмм, регистр

микрокоманд, дешифраторы, блок управления длительностью микропрограммного такта, секционная линия задания длительности такта, элемент НЕ 2 .

Однако данное устройство формирует наборы управляющих сигналов с различной длительностью. При этом блок управления устройства переклюtoчается на выполнение следующего такта после выполнения самого длинного такта, используемого для управления самым медленным узлом ЦВМ, причем это переключение производится в момент времени-, когда на всех выходах линии задержки прису.тствуют одинаковые уровни, например, сигналом с последнего выхода линии задержки. Это значительно снижает быстродействие устройства.

Цель изобретения - повышение быстродействия .

Поставленная цель достигается тем, что в устройство, содержащее дешифраторы, регистр микрокоманд, блок памяти микропрограмм, регистр ещреса и элемент НЕ, вход которого соединен со входом синхронизации регистра адреса, информационный выход которого соединен с адресным входом блока памяти микропрограмм, информационный выход которого соединен с информационным входом регистра микрокоманд, информационные выходы групп разрядов которого соединены со входами соответствующих дешифраторов, выходы которых, являются управляющимиV выходами устройства, введены блок приоритета, элементы И, элементы задержки и элемент ИЛИ, выход которого соединен со входом элемента НЕ, выход которого соединен с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами блока приоритета, в ;оды которого соединены с соответствующими выходами дешифраторов, выходы элементов И соединены со входами соответствующих «элементов задержки, выходы которых соединены со входами элемента ИЛИ.

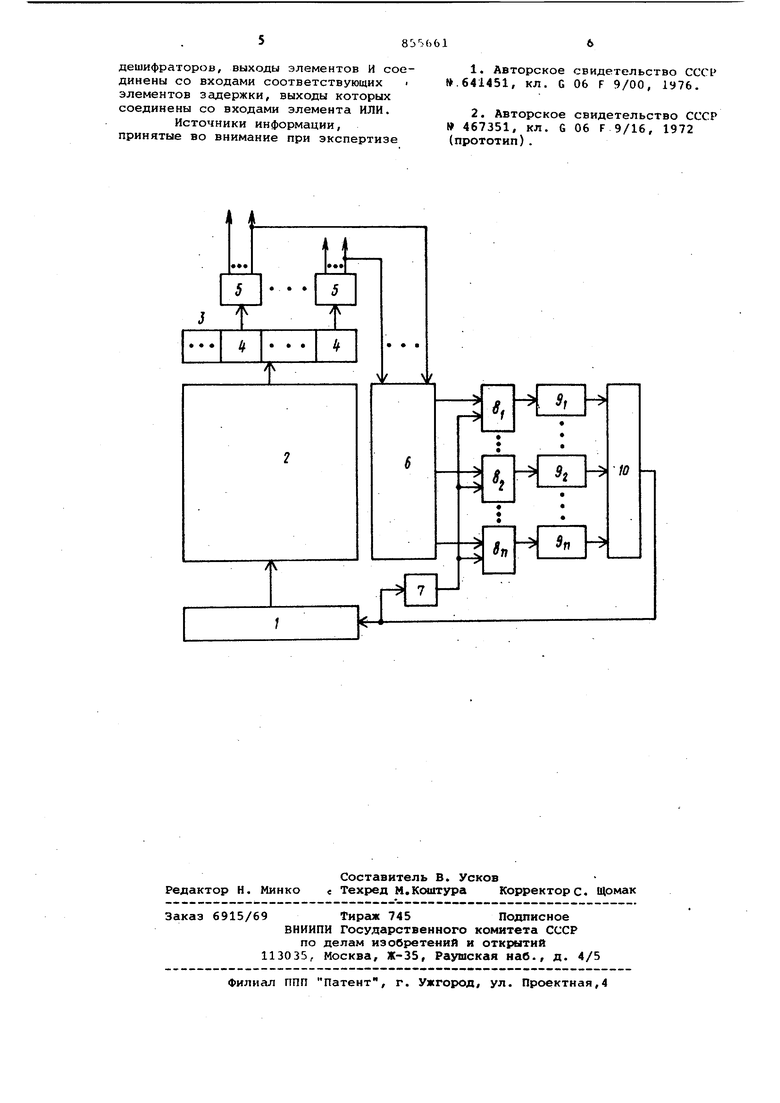

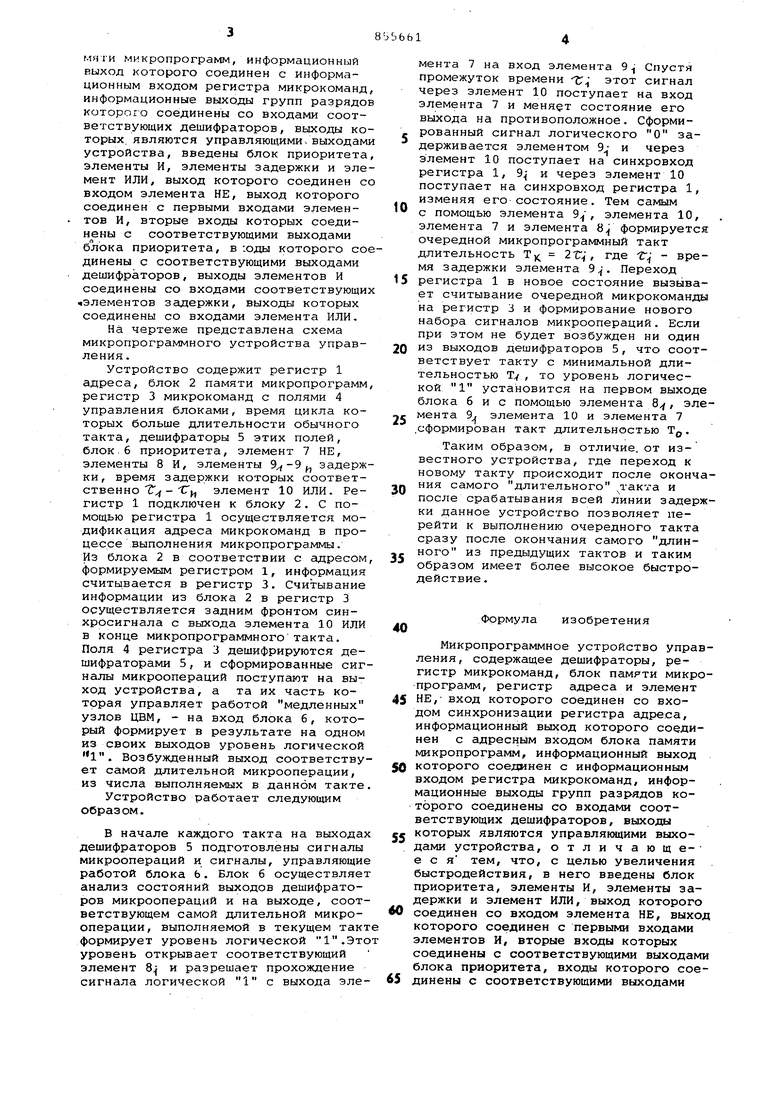

На чертеже представлена схема микропрограммного устройства управления .

Устройство содержит регистр 1 адреса, блок 2 памяти микропрограмм, регистр 3 микрокоманд с полями 4 управления блоками, время цикла которых больше длительности обычного такта, дешифраторы 5 этих полей, блок б приоритета, элемент 7 НЕ, элементы 8 И, элементы задержки, время задержки которых соответственно Т - tTj элемент 10 ИЛИ. Регистр 1 подключен к блоку 2. С помощью регистра 1 осуществляется модификация адреса микрокоманд в процессе выполнения микропрограммы. Из блока 2 в соответствии с адресом, формируемым регистром 1, информация считывается в регистр 3. Считывание информации из блока 2 в регистр 3 осуществляется задним фронтом синхросигнала с выхода элемента 10 ИЛИ в конце микропрограммного такта. Поля 4 регистра 3 дешифрируются дешифраторами 5, и сформированные сигналы микроопераций поступают на выход устройства, а та их часть которая управляет работой медленных узлов ЦВМ, - на вход блока 6, который формирует в результате на одном из своих выходов уровень логической 1. Возбужденный выход соответствует самой длительной микрооперации, из числа выполняемых в данном такте.

Устройство работает следующим образом.

В начале каждого такта на выходах дешифраторов 5 подготовлены сигналы микроопераций и сигналы, управляющие работой блока Ь. Блок б осуществляет анализ состояний выходов дешифраторов микроопераций и на выходе, соответствующем самой длительной микрооперации, выполняемой в текущем такт формирует уровень логической 1.Это уровень открывает соответствующий элемент 8 и разрешает прохождение сигнала логической 1 с выхода элемента 7 на вход элемента 9-j Спустя промежуток времени этот сигнал через элемент 10 поступает на вход элемента 7 и меняет состояние его выхода на противоположное. Сформированный сигнал логического О задерживается элементом и через элемент 10 поступает на синхровход регистра 1, и через элемент 10 поступает на синхровход регистра 1, изменяя его состояние. Тем самым с помощью элемента 9у, элемента 10, элемента 7 и элемента 8 формируется очередной микропрограммный такт длительность Т) 2Т , где - время задержки элемента . Переход

5 регистра 1 в новое состояние вызывает считывание очередной микрокоманды на регистр 3 и формирование нового набора сигналов микроопераций. Если при этом не будет возбужден ни один из выходов дешифраторов 5, что соот0ветствует такту с минимальной длительностью TY , то уровень логической 1 установится на первом выходе блока бис помощью элемента 8, элемента 9 элемента 10 и элемента 7

Таким образом, в отличие, от известного устройства, где переход к новому такту происходит после окончания самого длительного такта и

0 после срабатывания всей линии задержки данное устройство позволяет перейти к выполнению очередного такта сразу после окончания самого длинного из предыдущих тактов и таким образом имеет более высокое быстродействие .

Формула изобретения

40

Микропрограммное устройство управления, содержащее дешифраторы, регистр микрокоманд, блок памяти микропрограмм, регистр адреса и элемент

НЕ,- вход которого соединен со входом синхронизации регистра адреса, информационный выход которого соединен с адресным входом блока памяти микропрограмм, информационный выход

которого соединен с информационным входом регистра микрокоманд, информационные выходы групп разрядов которого соединены со входами соответствующих дешифраторов, выходы

которых являются управляющими выходами устройства, отличающе-е с я тем, что, с целью увеличения быстродействия, в него введены блок приоритета, элементы И, элементы задержки и элемент ИЛИ, выход которого

соединен со входом элемента НЕ, выход которого соединен с первыми входами элементов И, вторые входы которых соединены с соответствующими выходами блока приоритета, входы которого соединены с соответствующими выходами

дешифраторов, выходы элементов И соединены со входами соответствующих . элементов задержки, выходы которых соединены со входами элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР 467351, кл. G 06 F 9/16, 1972 (прототип).

Авторы

Даты

1981-08-15—Публикация

1979-11-19—Подача