Изобретение относится к вычислительной технике и может быть использовано в микропроцессорньк системах с микропрограммным управлением.

Целью изобретения является увеличение быcтpoдeik:твия устройства.

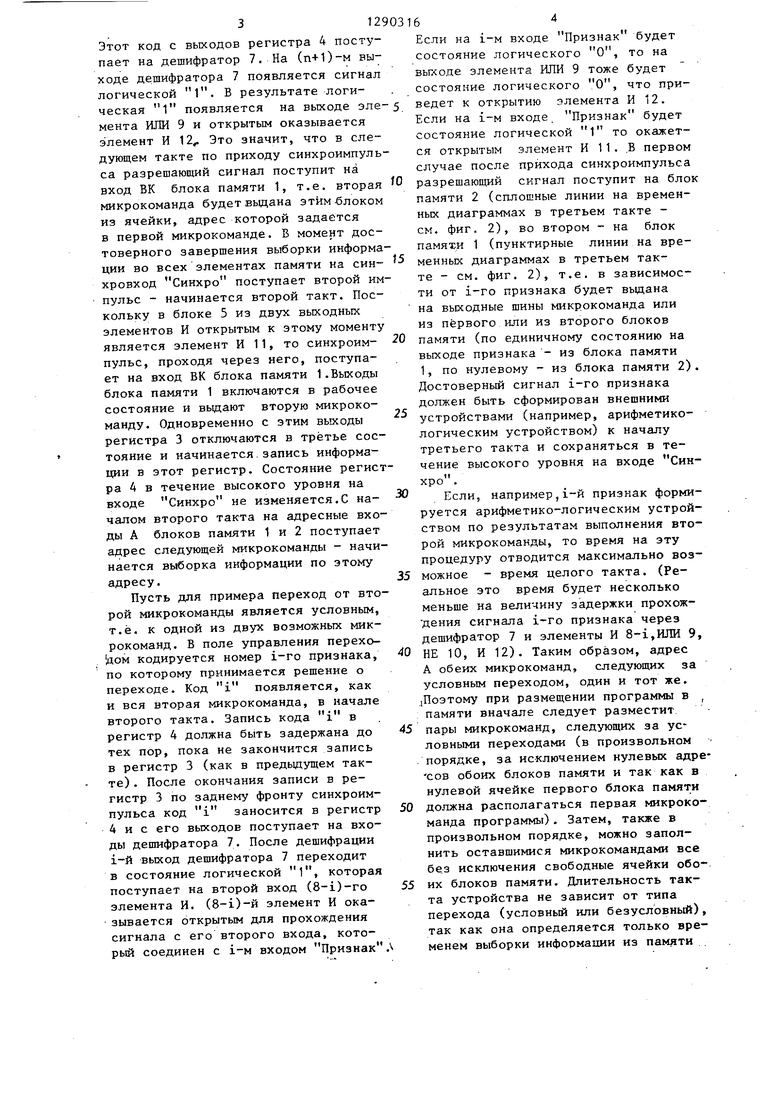

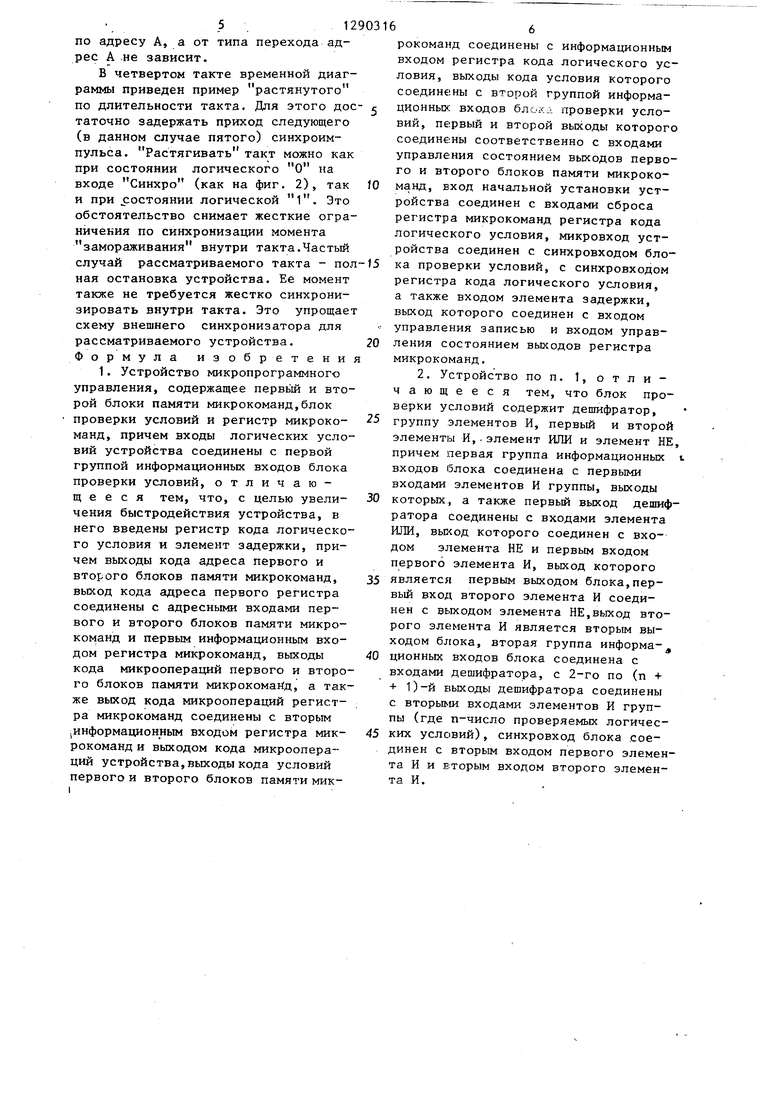

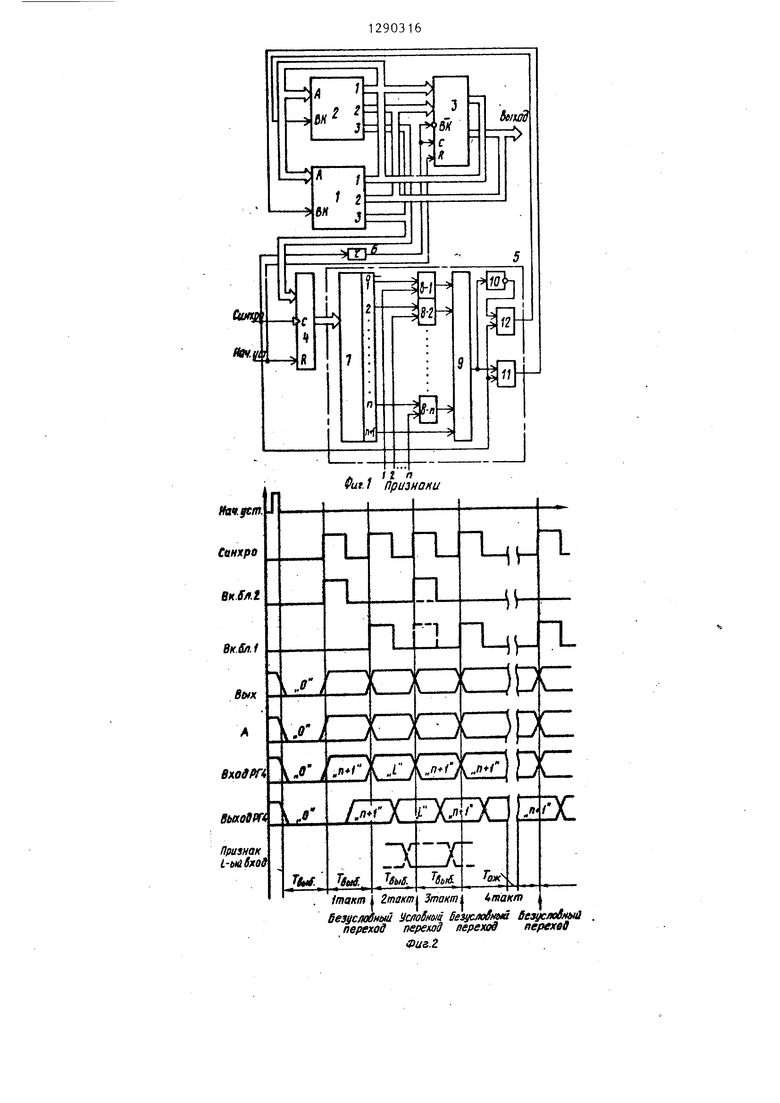

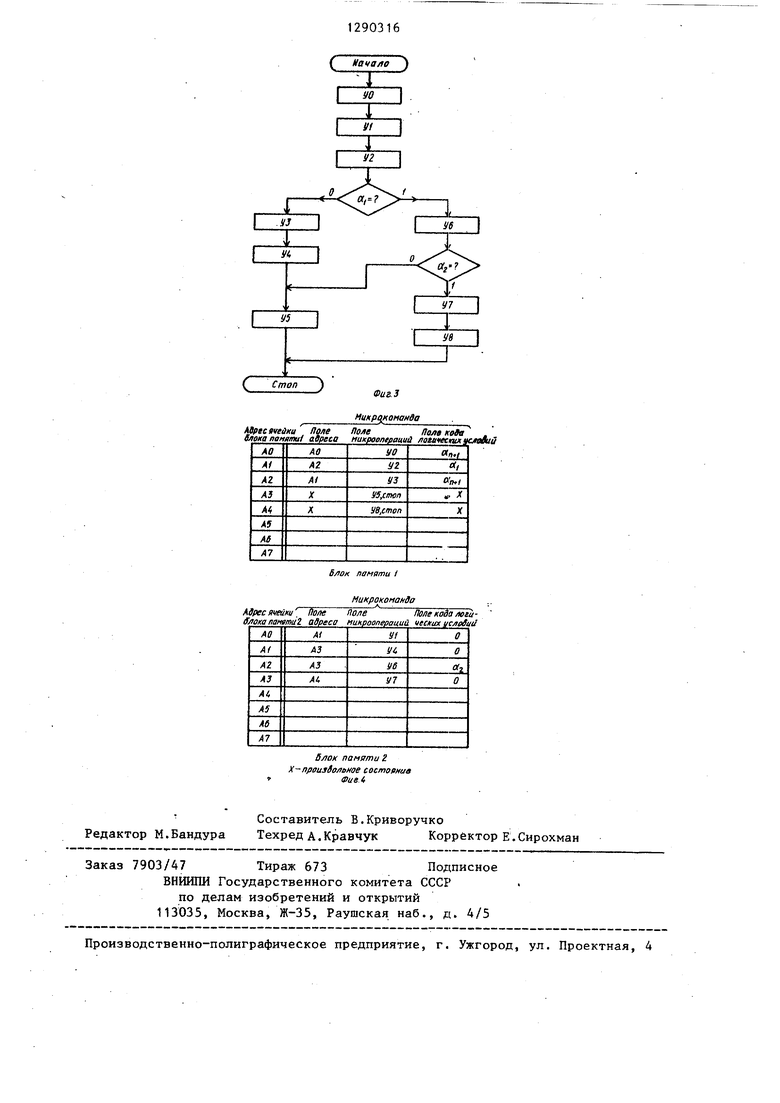

На фиг. ,1 показана функциональная схема устройства} на фиг. 2 - временные диаграм1«)1 работы устройства; на фиг, 3 - блок-схема программы; на фиг. 4 - размещение микрокоманд в блоках памяти, соответствукмцее приведенному алгоритму.

Устройство содержит первый 1 и второй 2 блоки памяти микрокоманд, регистр 3 микрокоманд, регистр 4 кода логического условия, блок 5 проверки условий, элемент 6 задержки.

Блок 5 проверки условий содержит дешифратор 7, группу из п элементов И 8, элемент ИЛИ 9, элемент НЕ 10, первый 11 и второй 12 элементы И.Устройство работает следующим образом.

В исходном состоянии (фиг. 1 и 2) на входах Нач.уст, и Синхро на- , ходятся логические О. Для организации выборки первой микрокоманды

на вход Нач.уст. подается импульс. ЗО мешали -ЬыходаЬ: блока памяти 2. В Регистры 3 и 4 устанавливаются в нутированный элементом НЕ 10 сигнал т.е. сигнал логической 1. На син хровходе блока 5 находится уровень логического О, поэтому выходы эле ментов И 11 и 12 также находятся в состоянии логического О. Эти уровни держат отключенными выходы блоков памяти 1 и 2 микрокоманд.Че рез время выборки после сигнала на входе Нач.уст. можно подавать си нал на вход Синхро для вьщачи первой микрокоманды из памяти на выходные шины. Первый импульс с входа Синхро поступая на синхро вход блока 5, проходит через элемент И 12 и оказывается на разреша ющем входе ВК блока памяти 2.Выходы этого блока включаются в рабочее состояние и вьщают на выходные шины микрокоманду, записанную по нулевому адресу. Таким образом первая микрокоманда микропрограммы должна располагаться по нулевому адресу второго блока памяти.Начин ется первый такт работы устройств Уровень логической 1 с входа Си хро, поступая на управляющий вход ВК регистра 3, отключает его вых ды в третье состояние,чтобы они не

то же время по сигналу логической 1 на синхровходе С ре гистра 3 происходит запись в этот регистр той информации, которую пока

евое состояние. Сигнал логического О на входе ВК регистра 3, постуающий с входа Синхро, включает ыходы регистра 3 в рабочее состояние. Следовательно, после установки егистра 3 в ноль нулевой код оказывается на адресных входах А блоков памяти 1 и 2, в которых начинается выборка информации по этому адресу. Одновременно с этим регистр 4 выдает нулевой код на вторую группу информационных входов блока 5 проверки условий. После дешифрации этого кода дешифратором 7 на нулевом выходе дешифратора 7 появляется логическая 1, на всех остальных выходах - логический О. Нулевой выход дешифратора 7 не используется в блоке 5, поэтому сигналы логичес- кого О устанавливают в состояние логического О и выходы группы элементов И 8-1,...,8-п. В результате на выходе элемента ИЛИ 9 оказался сигнал логического О. Элемент И 11 закрывается для прохожде- ния сигнала с синхровхода блока 5, а элемент И 11 открывается, так как на его первый вход поступает инвер

мешали -ЬыходаЬ: блока памяти 2. В

тированный элементом НЕ 10 сигнал, т.е. сигнал логической 1. На син- хровходе блока 5 находится уровень логического О, поэтому выходы элементов И 11 и 12 также находятся в состоянии логического О. Эти уровни держат отключенными выходы блоков памяти 1 и 2 микрокоманд.Через время выборки после сигнала на входе Нач.уст. можно подавать сигнал на вход Синхро для вьщачи первой микрокоманды из памяти на выходные шины. Первый импульс с входа Синхро поступая на синхро- вход блока 5, проходит через элемент И 12 и оказывается на разрешающем входе ВК блока памяти 2.Выходы этого блока включаются в рабочее состояние и вьщают на выходные шины микрокоманду, записанную по нулевому адресу. Таким образом первая микрокоманда микропрограммы должна располагаться по нулевому адресу второго блока памяти.Начинается первый такт работы устройства. Уровень логической 1 с входа Синхро, поступая на управляющий вход ВК регистра 3, отключает его выходы в третье состояние,чтобы они не

ЗО мешали -ЬыходаЬ: блока памяти 2. В

то же время по сигналу логической 1 на синхровходе С регистра 3 происходит запись в этот регистр той информации, которую пока

35 выдает блок памяти 2. Состояние

регистра 4 сохраняется, чтобы не -нарушить разрешающий сигнал блока 5 для блока памяти 2, После того, как произойдет запись в регистр 3,можно

40 отключить выходы блока памяти 2 и сменить информацию в регистре 4. Для этого сигнал на входе Синхро из состояния, д огической 1 устанавливается в состояние логического О

45 В результате на выходе элемента И 12 устанавливается состояние логического О, что приводит к отключению выходов блока памяти 2 в третье состояние, в регистр 4 записывается код

50 поля управления переходом к следующей микрокоманде, выходы регистра 3 включаются в рабочее состояние и выдают на входные шины тот же код,что И код, только что выдаваемый блоком

55 памяти 2.

Пусть, например, в регистр 4 записывается код п +1 из поля управления переходом первой микрокоманды.

312

Этот код с выходов регистра 4 поступает на дешифратор 7. На (п+1)-м выходе дешифратора 7 появляется сигнал логической 1. В результате логическая 1 появляется на выходе эле мента ИЛИ 9 и открытым оказывается элемент И 12 Это значит, что в следующем такте по приходу синхроимпульса разрешающий сигнал поступит на вход ВК блока памяти 1, т.е. вторая микрокоманда будет выдана этим блоком из ячейки, адрес которой задается в первой микрокоманде. В момент достоверного завершения выборки информации во всех элементах памяти на син- хровход Синхро поступает второй импульс - начинается второй такт. Поскольку в блоке 5 из двух выходных элементов И открытым к этому моменту является элемент И 11, то синхроим- пульс, проходя через него, поступает на вход ВК блока памяти 1.Выходы блока памяти 1 включаются в рабочее состояние и выдают вторую микрокоманду. Одновременно с этим выходы регистра 3 отключаются в третье состояние и начинается.запись информации в этот регистр. Состояние регистра А в течение высокого уровня на входе Синхро не изменяется.С на- чалом второго такта на адресные входы А блоков памяти 1 и 2 поступает адрес следующей микрокоманды - начинается выборка информации по этому адресу.

Пусть для примера переход от второй микрокоманды является условным, т.е. к одной из двух возможных микрокоманд. В поле управления перехо- дом кодируется номер i-ro признака, по которому принимается решение о переходе. Код i появляется, как и вся вторая микрокоманда, в начале второго такта. Запись кода i в регистр 4 должна быть задержана до тех пор, пока не закончится запись в регистр 3 (как в предыдущем такте) . После окончания записи в регистр 3 по заднему фронту синхроимпульса код i заносится в регистр 4 и с его выходов поступает на входы дешифратора 7. После дешифрации i-й выход дешифратора 7 переходит в состояние логической 1, которая поступает на второй вход (8-i)-ro элемента И. (8-1)-й элемент И оказывается открытым для прохождения сигнала с его второго входа, который соединен с i-м входом Признак.

164

Если на i-M входе Признак будет состояние логического О, то на выходе элемента ИЛИ 9 тоже будет состояние логического О, что приведет к открытию элемента И 12. Если на i-M входе. Признак будет состояние логической 1 то окажется открытым элемент И 11. .В первом случае после прихода синхроимпульса разрешающий сигнал поступит на бло памяти 2 (сплошные линии на временных диаграммах в третьем такте - см. фиг. 2), во втором - на блок памяти 1 (пунктирные линии на временных диаграммах в третьем такте - см. фиг. 2), т.е. в зависимости от i-ro признака будет выдана на выходные шины микрокоманда или из первого или из второго блоков памяти (по единичному состоянию на выходе признака - из блока памяти 1, по нулевому - из блока памяти 2) Достоверный сигнал i-ro признака должен быть сформирован внешними устройствами (например, арифметико- логическим устройством) к началу третьего такта и сохраняться в течение высокого уровня на входе Син- хро.

Если, например,i-й признак формируется арифметико-логическим устройством по результатам выполнения второй микрокоманды, то время на эту процедуру отводится максимально возможное - время целого такта. (Реальное это время будет несколько меньше на величину задержки прсхож- дения сигнала i-ro признака через дешифратор 7 и элементы И 8-i,ИЛИ 9, НЕ 10, И 12). Таким образом, адрес А обеих микрокоманд, следующих за условным переходом, один и тот же. Поэтому при размещении программы в памяти вначале следует разместит пары микрокоманд, следующих за условными переходами (в произвольном порядке, за исключением нулевых адре сов обоих блоков памяти и так как в нулевой ячейке первого блока памяти должна располагаться первая микрокоманда программы). Затем, также в произвольном порядке, можно заполнить оставшимися микрокомандами все без исключения свободные ячейки обоих блоков памяти. Длительность такта устройства не зависит от типа перехода (условный или безусловный), так как она определяется только временем выборки информации из памяти

по адресу А, а от типа перехода адрес А не зависит.

В четвертом такте временной диаграммы приведен пример растянутого по длительности такта. Для этого дос таточно задержать приход следующего (в данном случае пятого) синхроимпульса. Растягивать такт можно как при состоянии логического О на входе Синхро (как на фиг. 2), так и при :остоянии логической 1. Это обстоятельство снимает жесткие ограничения по синхронизации момента

замораживания внутри такта.Частый случай рассматриваемого такта - по ная остановка устройства. Ее момент также не требуется жестко синхронизировать внутри такта. Это упрощае схему внешнего синхронизатора для рассматриваемого устройства. Формула изобретени

1. Устройство микропрограммного управления, содержащее первьгй и второй блоки памяти микрокоманд,блок проверки условий и регистр микрокоманд, причем входы логических условий устройства соединены с первой группой информационных входов блока проверки условий, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены регистр кода логического условия и элемент задержки, причем выходы кода адреса первого и второго блоков памяти микрокоманд, выход кода адреса первого регистра соединены с адресными входами первого и второго блоков памяти микрокоманд и первым информационным входом регистра микрокоманд, выходы кода микроопераций первого и второго блоков памяти микрокоманд, а также выход кода микроопераций регистра микрокоманд соединены с вторым (Информационным входом регистра мик- рокоманд и выходом кода микроопераций устройства, выходы кода условий первого и второго блоков памяти мик

рокоманд соединены с информационным входом регистра кода логического условия, выходы кода условия которого соединены с второй группой информационны} : входов блока проверки условий, первый и второй выходы которого

соединены соответственно с входами управления состоянием вькодов первого и второго блоков памяти микрокоманд, вход начальной установки устройства соединен с входами сброса регистра микрокоманд регистра кода логического условия, микровход устройства соединен с синхровходом блока проверки условий, с синхровходом регистра кода логического условия, а также входом элемента задержки, выход которого соединен с входом управления записью и входом управления состоянием выходов регистра микрокоманд.

2. Устройство по п. 1, отличающееся тем, что блок проверки условий содержит дешифратор, группу элементов И, первый и второй элементы И,.элемент ИЛИ и элемент НЕ, причем первая группа информационных t входов блока соединена с первыми входами элементов И группы, выходы которых, а также первый выход дешифратора соединены с входами элемента ИЛИ, которого соединен с входом элемента НЕ и первым входом первого элемента И, выход которого является первым выходом блока,первый вход второго элемента И соединен с вькодом элемента НЕ,выход второго элб;мента И является вторым выходом блока, вторая группа информа- ционных входов блока соединена с входами дешифратора, с 2-го по (п + + 1)-й выходы дешифратора соединены с вторыми входами элементов И группы (где п-число проверяемых логичес- ких условий), синхровход блока соединен с вторым входом первого элемента И и вторым входом второго элемента И.

Признак 1-1 л6жо9

1т9кт

бездслсбнш HcaoStnui Везусмвгяю беадсаобяьЛ переход переход переход nepexeS

Фи&2

.f. , Ч п

vut. ( Признаки

( Начаао

( Стоп )

MtfteimuKu Пале ПолеПол кова

вяам naMeffiai авресо Huxpoiintfauuu /lateiecnex ycjaauS

dflOK памяти I

Микрокоманйо

Мрес ячейки , Поле ПолеПоле кода/югаf/iOKu памвти авреса ниироопераиий vecKia ycjietuii

Блок памяти Z

X-npouiSoanHoe состомив

ФиеЛ

Редактор М.Бандура

Составитель В.Криворучко

Техред А.Кравчук Корректор Е.Сирохман

Заказ 7903/47 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

Никрдконанва

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Микропроцессор | 1985 |

|

SU1336023A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1399738A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1295392A1 |

| Микропроцессор | 1986 |

|

SU1361572A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168939A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системах с микропрограммным управлением. Целью изобретения является увеличение быстродействия устройства. Устройство микропрограммного управления содержит два блока памяти микрокоманд, регистр микрокоманд, регистр кода логического условия,блок проверки условий и элемент задержки. Цель изобретения достигается за счет совмещения процесса обработки логических условий и процесса выборки адреса очередной микрокоманды в устройстве. 1 з.п. ф-лы, 4 ил. (Л :о а

| Балашов Е.П., Пузанов Д.В | |||

| Микропроцессоры и микропроцессорные системьт | |||

| И.: Радио и связь, 1981, с | |||

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964640A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1984-11-28—Подача