Изобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом контроле логических блоков.

Цель изобретения - увеличение быстродействия.

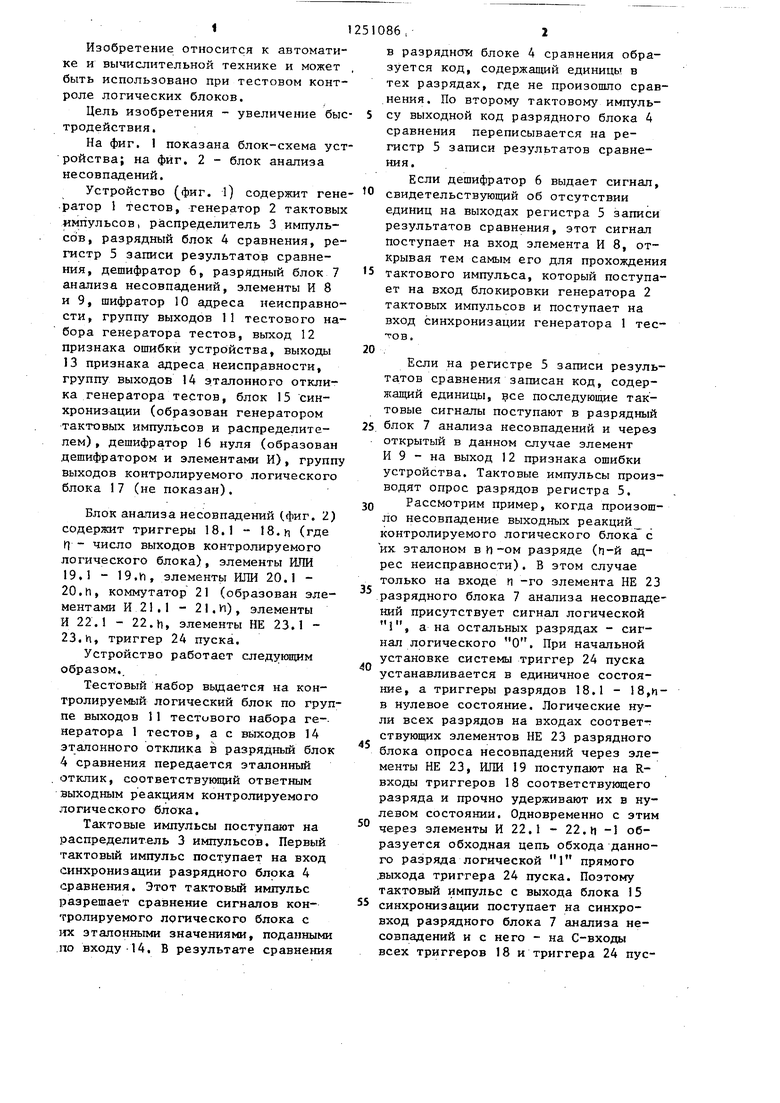

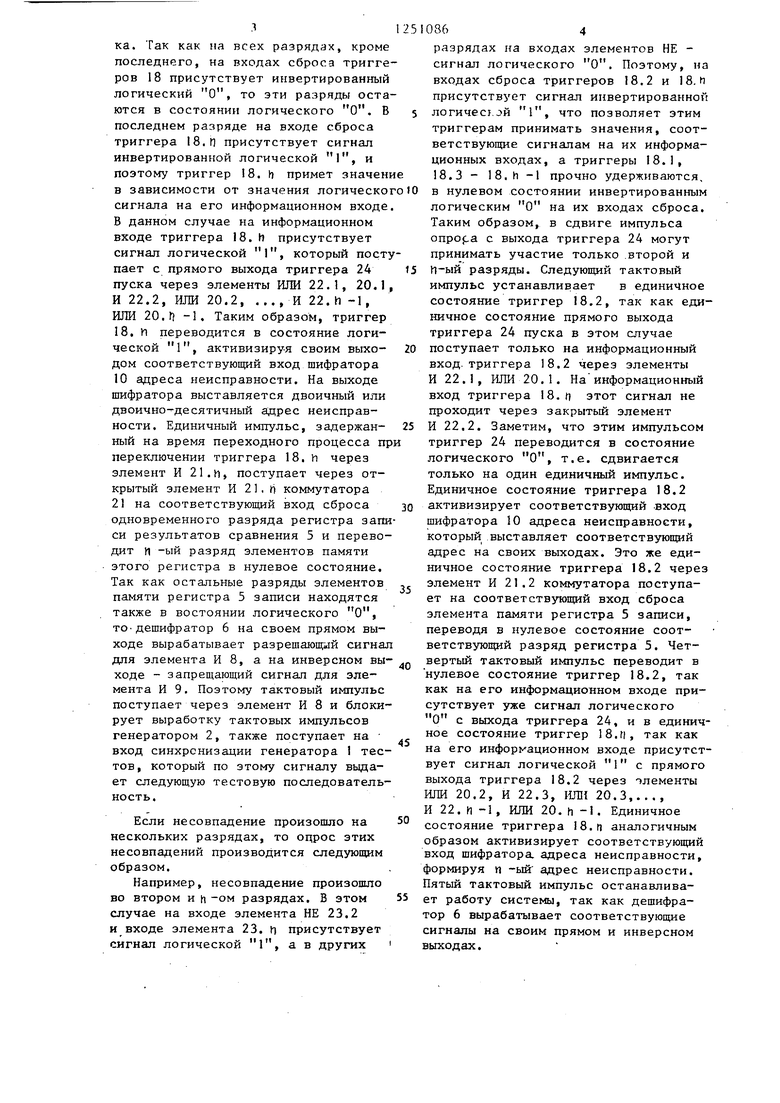

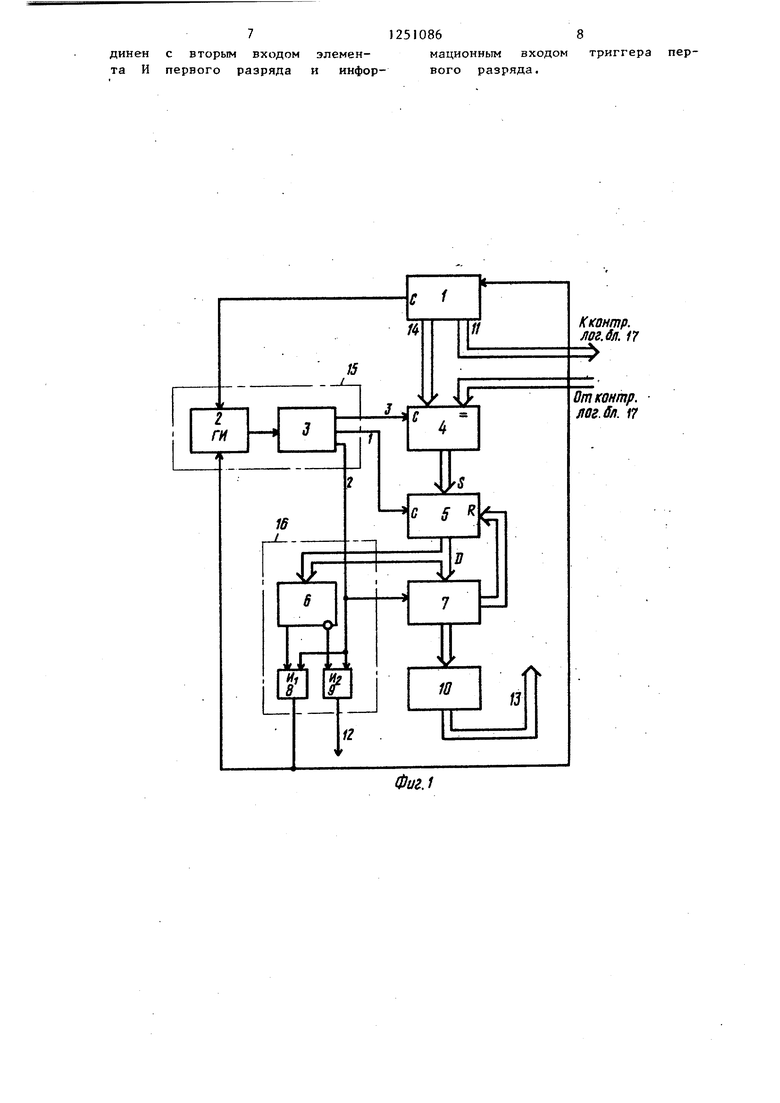

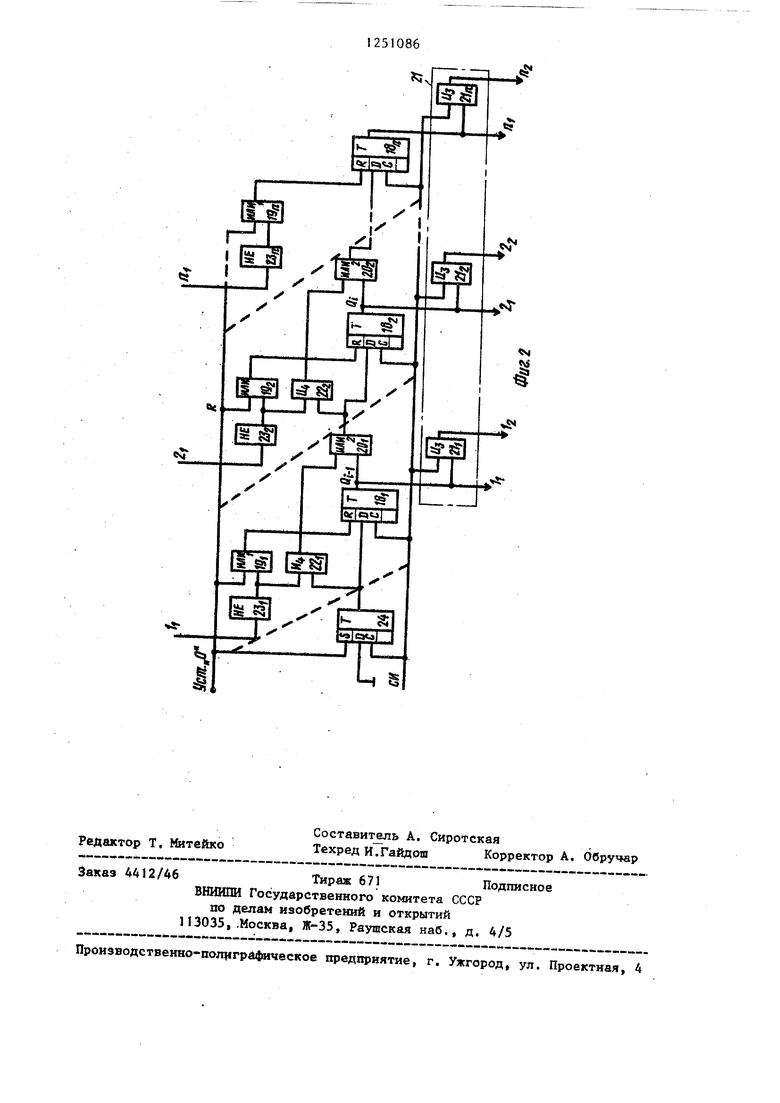

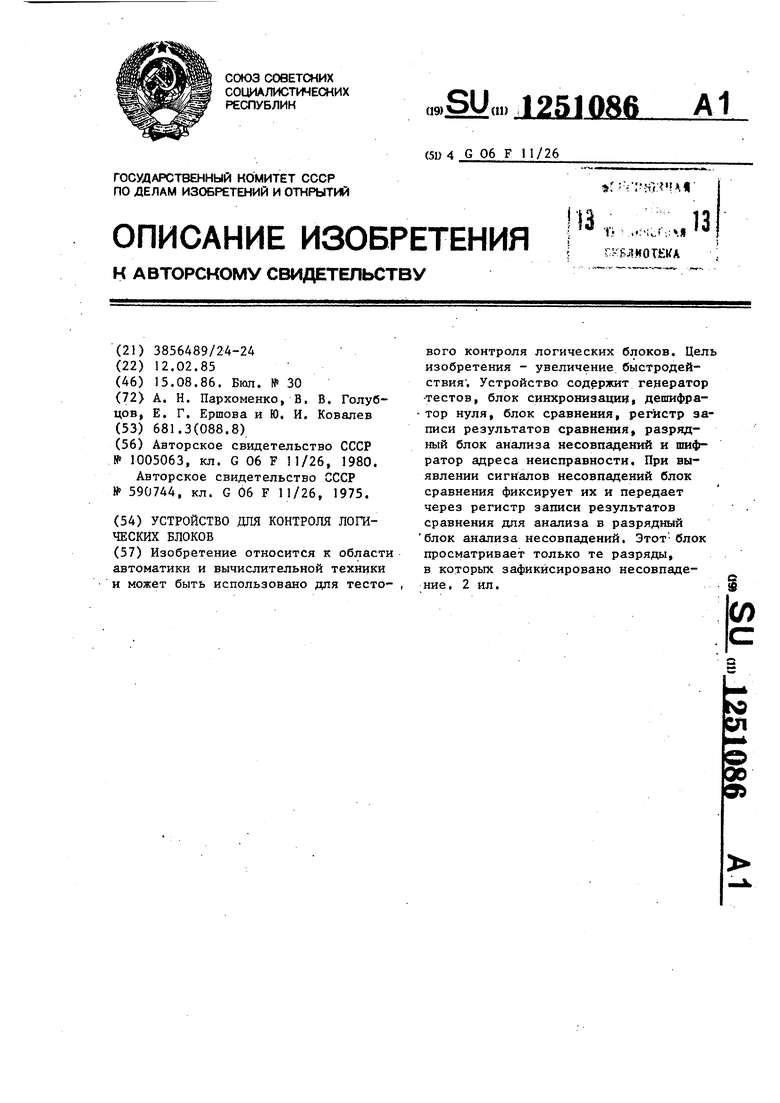

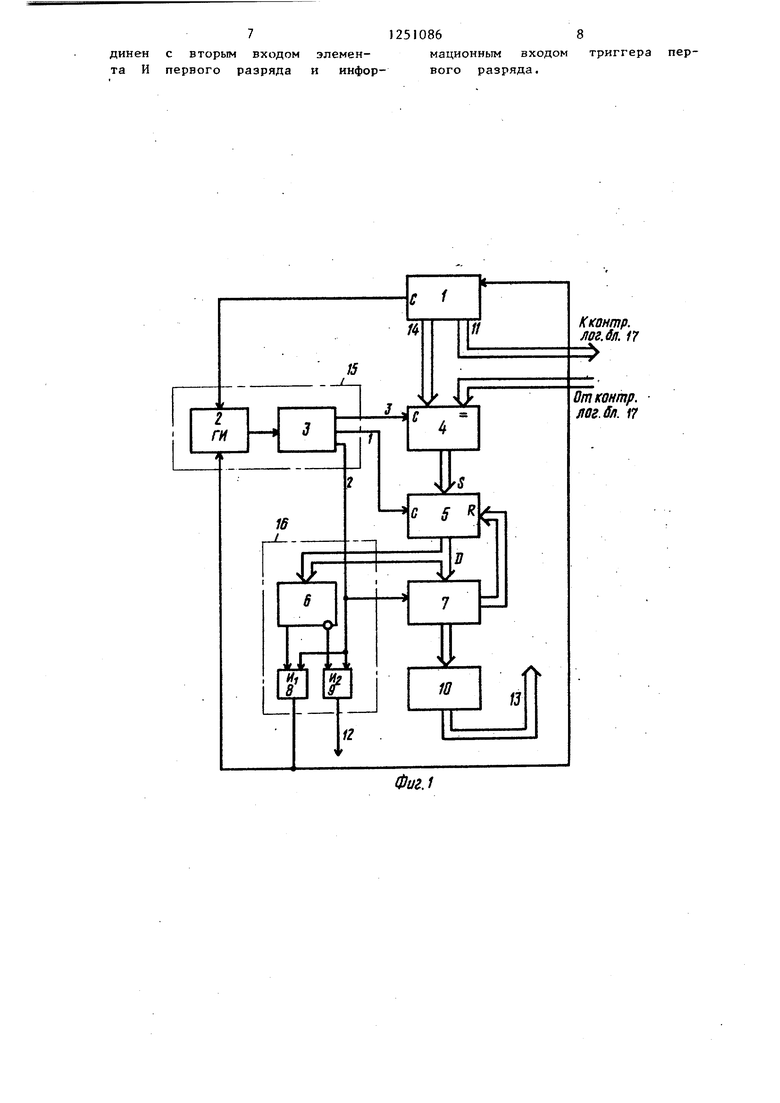

На фиг, 1 показана блок-схема устройства; на фиг, 2 - блок анализа несовпадений.

Устройство (фиг. 1) содержит генератор 1 тестов, генератор 2 тактовых импульсов, распределитель 3 импульсов, разрядный блок 4 сравнения, регистр 5 записи результатов сравнения, дешифратор 6, разрядный блок 7 анализа несовпадений, элементы И 8 и 9, шифратор 10 адреса неисправности, группу выходов 11 тестового набора генератора тестов, выход 12 признака ошибки устройства, выходы 13 признака адреса неисправности, группу выходов 14 эталонного отклика генератора тестов, блок 15 синхронизации (образован генератором тактовых импульсов и распределителем) , дешифратор 16 нуля (образован дешифратором и элементами И), группу выходов контролируемого логического блока 17 (не показан),

Блок анализа несовпадений (фиг. 2) содержит триггеры 18,1 - 18.н (где Y - число выходов контролируемого логического блока), элементы ИЛИ 19,1 - 19,И, элементы ИЛИ 20.1 - 20,и, коммутатор 21 (образован элементами И 21.1 - 2I.И), элементы И 22,1 - 22.h, элементы НЕ 23,1 - 23,п, триггер 24 пуска.

Устройство работает следующим образом.

Тестовый набор вьщается на контролируемый логический блок по группе выходов 11 тестового набора ге-. нератора 1 тестов, а с вьгходов 14 эталонного отклика в разрядный блок 4 сравнения передается эталонный отклик, соответствукйций ответным выходным реакциям контролируемого логического блока.

Тактовые импульсы поступают на распределитель 3 импульсов. Первый тактовый импульс поступает на вход синхронизации разрядного блока 4 сравнения. Этот тактовый импульс разрешает сравнение сигналов контролируемого лргического блока с их эталонными значениями, поданными по входу 14, В результате сравнения

51086,2

в разряднотй блоке 4 сравнения образуется код, содержащий единицы в тех разрядах, где не произошло сравнения. По второму тактовому импуль5 су выходной код разрядного блока 4 сравнения переписывается на регистр 5 записи результатов сравнения.

Если дешифратор 6 выдает сигнал,

О свидетельствующий об отсутствии

единиц на выходах регистра 5 записи результатов сравнения, этот сигнал поступает на вход элемента И 8, открывая тем самым его для прохождения

5 тактового импульса, который поступает на вход блокировки генератора 2 тактовых импульсов и поступает на вход синхронизации генератора 1 тес- гов,

20

Если на регистре 5 записи результатов сравнения записан код, содержащий единицы, 9се последующие тактовые сигналы поступают в разрядный

25, блок 7 анализа несовпадений и через открытый в данном случае элемент И 9 - на выход 12 признака ошибки устройства. Тактовые импульсы производят опрос разрядов регистра 5.

3Q Рассмотрим пример, когда произошло несовпадение выходных реакций контролируемого логического блока с их эталоном в и-ом разряде (м-й адрес неисправности). В этом случае только на входе ц -го элемента НЕ 23 разрядного блока 7 анализа несовпадений присутствует сигнал логической , а на остальных разрядах - сигнал логического О. При начальной установке системы триггер 24 пуска устанавливается в единичное состояние, а триггеры разрядов 18,1 - 18,h- в нулевое состояние. Логические нули всех разрядов на входах соответ-: ствующих элементов НЕ 23 разрядного блока опроса несовпадений через элементы НЕ 23, ИЛИ 19 поступают на R- входы триггеров 18 соответствукнцего разряда и прочно удерживают их в нулевом состоянии. Одновременно с этим

° через элементы И 22.1 - 22,И -1 образуется обходная цепь обхода данного разряда логической 1 прямого .выхода триггера 24 пуска. Поэтому тактовый импульс с выхода блока 15

35

40

45

55

синхронизации поступает на синхро- вход разрядного блока 7 анализа несовпадений и с него - на С-входы всех триггеров 18 и триггера 24 пусл

ка. Так как на всех разрядах, кроме последнего, на входах сброса триггеров 18 присутствует инвертированный логический О, то эти разряды остаются в состоянии логического О. В последнем разряде на входе сброса триггера 18.П присутствует сигнал инвертированной логической 1, и поэтому триггер 18. h примет значени в зависимости от значения логическог сигнала на его информационном входе. В данном случае на информационном входе триггера 18. h присутствует сигнал логической 1, которьй поступает с прямого выхода триггера 24 пуска через элементы ИЛИ 22.1, 20,1,

И 22.2, ИЛИ 20.2И22.И-1,

ИЛИ 20, f) -1. Таким образом, триггер 18, И переводится в состояние логической 1, активизируя своим выхо- дом соответствующий вход шифратора 10 адреса неисправности. На выходе шифратора выставляется двоичный или двоично десятичный адрес неисправности. Единичный импульс, задержан- ный на время переходного процесса пр переключении триггера 18. h через элемент И 21.ii, поступает через открытый элемент И 2. h коммутатора 21 на соответствующий вход сброса одновременного разряда регистра записи результатов сравнения 5 и переводит м -ый разряд элементов памяти этого регистра в нулевое состояние. Так как остальные разряды элементов памяти регистра 5 записи находятся также в востоянии логического О, то-дешифратор 6 на своем прямом выходе вырабатывает разрешающий сигнал для элемента И 8, а на инверсном вы- ходе - запрещающий сигнал для элемента И 9. Поэтому тактовый импульс поступает через элемент И 8 и блокирует выработку тактовых импульсов генератором 2, также поступает на вход синхронизации генератора 1 тестов , который по этому сигналу выдает следующую тестовую последовательность.

Если несовпадение произошло на нескольких разрядах, то оцрос этих несовпадений производится следуюгцим образом.

Например, несовпадение произошло во втором и h ом разрядах. В этом случае на входе элемента НЕ 23.2 и входе элемента 23. li присутствует сигнал логической 1, а в других

864

разрядах на входах элементов НЕ - сигнал логического О. Поэтому, на входах сброса триггеров 18.2 и 18. м присутствует сигнал инвертированной логичесг.й 1, что позволяет этим триггерам принимать значения, соответствующие сигналам на их информационных входах, а триггеры 18.1, 18.3 - 18.h -1 прочно удерживаются, в нулевом состоянии инвертированным логическим О на их входах сброса. Таким образом, в сдвиге импульса onpoj a с выхода триггера 24 могут принимать участие только .второй и П-ый разряды, Следуюш 1Й тактовый импульс устанавливает в единичное состояние триггер 18.2, так как единичное состояние прямого выхода триггера 24 пуска в этом случае поступает только на информационный вход, триггера 18.2 через элементы И 22.1, ИЛИ 20.1. На информационный вход триггера 18.п этот сигнал не проходит через закрытый элемент И 22.2. Заметим, что этим импульсом триггер 24 переводится в состояние логического О, т.е. сдвигается только на один единичный импульс. Единичное состояние триггера 18,2 активизирует соответствующий -вход шифратора 10 адреса неисправности, который выставляет соответствующий адрес на своих выходах. Это же единичное состояние триггера 18.2 через элемент И 21.2 коммутатора поступает на соответствующий вход сброса элемента памяти регистра 5 записи, переводя в нулевое состояние соответствующий разряд регистра 5. Четвертый тактовый импульс переводит в нулевое состояние триггер 18.2, так как на его информационном входе присутствует уже сигнал логического О с выхода триггера 24, и в единичное состояние триггер 18.Г|, так как на его информационном входе присутствует сигнал логической 1 с прямого выхода триггера 18.2 через лeмeнты ИЛИ 20.2, И 22.3, ИЛИ 20.3,..., И 22. и -1, ИЛИ 20.h -1. Единичное состояние триггера 18.П аналогичным образом активизирует соответствующий вход шифратора адреса неисправности, формируя п -ый адрес неисправности. ПятЕзй тактовый импульс останавливает работу системы, так как дешифратор 6 вырабатывает соответствующие сигналы на своим прямом и инверсном выходах.

В системе исключения татратьз времени на просмотр разря; ов, на которых не произошло несравненияр так как разрядный 6.a(jK 7 анализе, несовпадений производит опрос только несрав- пившихся разрядов.

Формула изобретения

Устройство fjflfi контроля логичес- блоков, содержащее генератор тестов, регистр записи результатов сравнения, разрядный блок сравненияj разрядный блок анализа месовпаденийj шифратор адреса неисправности и блок синхронизации,- причем группа выходов этапонного отклика тренератора тестов соединена с первой группой информационных входов разряг ного бло ка сравнения 5, выходы Равно всех разрядов которого соединены с информационными входами разрядов разрядного блока, анализа несовпадений, выхды которого соединены с информацион- 1а1ми входами шифратора адреса неисправности, выходы которого являются выходат-ш признака адреса неисправно- c i H устройства, вход установки которого со эдинен с входом установки рапрядного блока анализа несовпаде- Н11Й и входом сброса регистра записи результатов сравнеаня, первый блока сянхрониза.ции соединен со входом синхрогд1затдии регистра записи реэульт;ятов сравненияj второй выход блока синхронизации соединен с вхо- док сиюсронизацик разрядного блока анализа несовпадений, выход признака тестового набора генератора тестов соединен с входом пуска блока синхро кизации при этом разрядный блок аиапиза несовпадений содержит.в кшад i--M разряде (., , . 1 1 число выходов 1«)нтролнруемого логического .блока), кроме п-го ра.зряда5 туу-тггер s элемент НЕ; первы й эле.;ент И.Т1Й и з.пемент И а h -и разркд содержит триггер,, э.демемт НЕ и элемент ШЖе дфичем вход установки разрядн от о б.лока анализа несовлгадений соединен с первыми входами первых э.;1е.ментоБ ЯШ разрядов с первого по (п--1)й и пйрзым я:кодом з.пенента ШШ П-го разряда разрядного блока анализа,, о т л и ч а ю щ е е с я тем, что с целью увели .;ения быстродействия ус1 ройство содержит дешифратор нуля, ризрядный блох аналяза.несовпа, ,ений со

0

5

5

0

S

0

коммутатор и ч ригг ер пуска, а разряды его с первого по (п-1)-й содержит вторые элементы ШШ, причем выходы регистра записи результатов сравнения соединены с информационными входами дешифратора нуля, вход син- хрО1 изации которого соединен со вто- рь(м выходом блока синхронизации, третий выход которого соединен с входом синхронизации разрядного блока сравнения,, пряной выход дешифратора нуля соединен с входом блокировки блока синхронизации и входом синхронизации генератора тестовj инверсный выход дешифратора нуля соединен с выходом .признака ошибки устройства, а в разрядном блоке анализа несовпа- дений единичный вход триггера пуска соединен с вхо,цом установки устройст- .sa информационный вход триггера пуска подключен к шине нулевого по- тгнциала устройства, входы синхронизации триггера всех разрядов соединр.- нь с яходом синхронизаики разрядного б.ло;;й анализа несовпадений, с входом синхронизации триггера пуска и управляющим входом комкутатора, информационные входы которого соединены с выходами триггеров всех разрядов, с первыми входами вторых элементов .ИЖ разрядов с первого по ()1--1)-й и выходами разрядного блока анализа несовпадений5 элементов НЕ всех разрядов соединены с соответствую- ,ЩМ1Л информационными входами разрядного блока анализа несовпадений, выходы элементов НЕ всех разрядов, кроме h -гОр соединены со вторыми входами первых элементов ЖТИ и с первыми входами элементов И соответ- ствуюгоих разр.ядов5 выход элемента НЕ ,1-го разряди сое,динен со вторым входом элемента ПТИ разряда, вы- ..;од которого соединек с эходок сброса триггера S l-ro разряда БЫХОДЬ; первых э.псментов И.ПИ с йуядов с пер - ;аого по (h-- ). соединены со входами сброса тркг геров одноименных разряде 3j выходь; злементов И ;..is .р.чдов с первого по (п)-й соединены

со вторыми входа 4И вторых э.а8Мбнтов И1Й1 одноименных разрядов, выходы эторых :;лементон tUTH разря.цов с первого по ()й соедике Еь : икфсрма- циониыми входами триггеров г-Езркдов со второго по ,и со : -;ч;у: зхода- - & злекенто з К ра.зрядов со второго ко (( |--)-й Бьгкод тригг ера nycKS сое712510868

динен с вторым входом элемен- мационным входом триггера пер- та И первого разряда и инфор- вого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля параметров объекта | 1987 |

|

SU1461230A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Устройство для контроля хода программ | 1986 |

|

SU1343418A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для тестового контроля логических блоков. Цель изобретения - увеличение быстродействия; Устройство содержит генератор -тестов, блок синхронизации, дешифратор нуля, блок сравнения, регастр записи результатов сравнения, разрядный блок анализа несовпадений и шифратор адреса неисправности. При выявлении сигналов несовпадений блок сравнения фиксирует их и передает через регистр записи результатов сравнения для анализа в разрядный блок анализа несовпадений. Этот блок просматривает только те разряды, в которых зафикйсировано несовпадение t 2 ил.

Редактор Т, Митейко

Составитель А. Сиротская

Техред иТГаЙдош Корректор А. Обручар

Заказ 4412/46Тираж 671Подписное

ВНШШИ Государственного комитета СССР

по делам изобретений и открытий 113035, .Москва, Ж-35, Раушская наб,, д. 4/5

Проидводственно-полнграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Система для контроля электронных устройств | 1980 |

|

SU1005063A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для анализа состояний логических узлов | 1975 |

|

SU590744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-15—Публикация

1985-02-12—Подача