(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ

1

Изобретение относится к вычислительной технике и может быть использовано при проектировании запомингиощих устройств повышенной надежности.

Известны запоминающие устройства с обнаружением одиночных етиибок,которые содержат блок свертки по модулю два, подключенный к регистрам, блок сравнения, подключенный к выходам триггеров контрольных разрядов регистров и к выходам блока свертки по модулю два, и блок преобразования контрольных разрядов til

Недостатком этого устройства .является низкая его надежность за счет введения дополнительного оборудования в виде контрольных разрядов.

Наиболее близким по технической к изобретению является запом«наю(цее устройство с обнаружением ошибки, содержащее регистр адреса, входной регистр числа с контрольным разрядом на нечетность (четность), дешифратор адреса, накопитель, схему проверки на четность, выходной регистр числа, усилители считывания и блок управления С 2. .

Недостатком зтого устройства явля.ется низкая надежность за счет избыОДИНОЧНЫХ ОШИБОК

точного оборудования, необходимого для запоминания контрольных разрядов.

Цель изобретения - повышение надежности .

5 -Поставленная цель достигается

тем, что в запоминающее устройство сабнаружением одиночных ошибок, содержащее адресный регистр, первые выходы которого подключены ко входам

адресного дешифратора, первый накопитель, адресные входы которого подключены к выходам адресного дешифратора, а его информационные входы являются информационными входами

15 устройства, блок управления, первый выход которого подключён к первому управляющему входу первого накопителя, и блок контроля, дополнительно введены второй накопитель, адресные входы которого подключены к выходам адресного дешифратора, инфор. мационные входы - к информационным входам первого накопителя, а первый управляющий вход - к первому выходу

25 блока управления, формирователь

контрольного разряда, входы которого подключены к информационным входам первого накопителя, первый элемент И, первый вход которого подключен к

30 выходу формирователя контрольного

разряда, а второй вход - к первому выходу блока управления, второй элемент И, первый вход которого подключен ко второму выходу адресного регистра, а выход - к первому входу блока контроля, элемент ИЛИ, первый вход которого подключен к. выходу первого элемента И, а второй вход к выходу второго элемента И, а выход элемента ИЛИ подключен ко второму входу адресного дешифратора, группу элементов ИЛИ, первые входы которых подключены к выходам первого накопителя, а вторые входы - к выходам второго накопителя, выходы групп элементов ИЛИ подключены ко вторым входам блока контроля и являются выходами устройства, второй выход блока управления подключен ко второму входу второго элемента И и ко вторым управляющим .входам первого и второго накопителей.

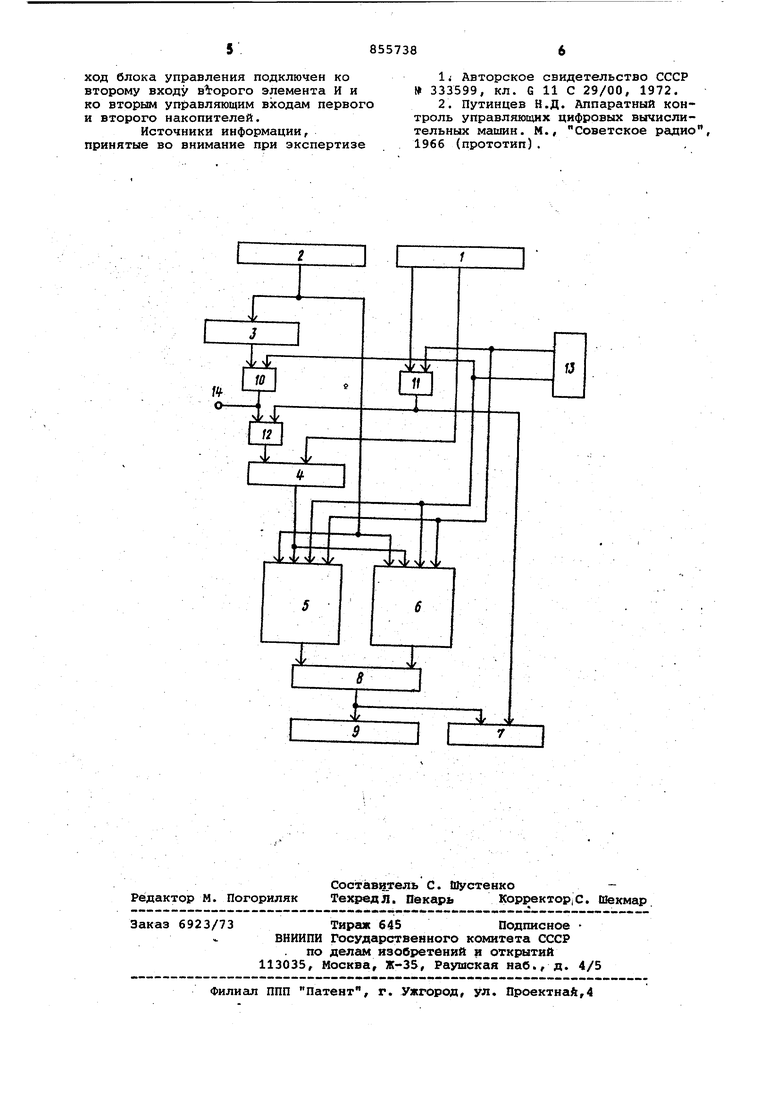

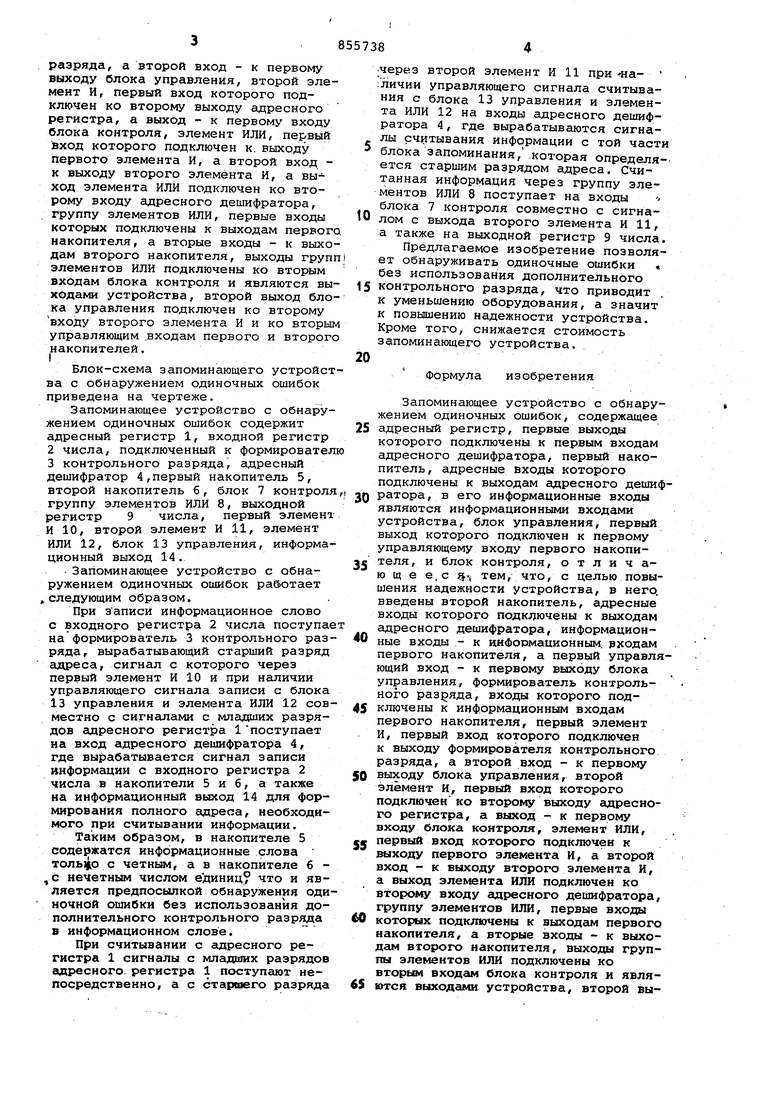

Блок-схема запоминающего устройства с обнаружением одиночных ошибок приведена на чертеже.

Запоминающее устройство с обнаружением одиночных ошибок содержит адресный регистр 1, входной регистр

2числа, подключенный к формировател

3контрольного разряда, адресный дешифратор 4,первый накопитель 5, второй накопитель б, блок 7 контроля группу элементов ИЛИ 8, выходной регистр 9 числа, первый элемент

И 10, второй элемент И 11, элемент ИЛИ 12, блок 13 управления, информационный выход 14.

Запоминающее устройство с обнаружением одиночных ошибок работает , следующим образом.

При записи информационное слово с входного регистра 2 числа поступае на формирователь 3 контрольного разряда, вырабатывающий старший разряд адреса, сигнал с которого через первый элемент И 10 и при наличии управляющего сигнала записи с блока 13 управления и элемента ИЛИ 12 совместно с сигналами с младших разрядов адресного регистра 1поступает на вход адресного дешифратора 4, где вырабатывается сигнал записи информации с входного регистра 2 числа в накопители 5 и 6, а также на информационный выход 14 для формирования полного адреса, необходимого при считывании информации.

Таким образом, в накопителе 5 содержатся информационные слова tonbij p с четным, а в накопителе б ,с нечетным числом единиц что и является предпосылкой обнаружения одиночной ошибки без использования дополнительного контрольного разряда в информационном слове.

При считывании с адресного регистра 1 сигналы с младших разрядов адресного регистра 1 поступают непосредственно, а с старшего разряда

через второй элемент И 11 при-на;личии управляющего сигнала считывания с блока 13 управления и элемента ИЛИ 12 на входы адресного дешифратора 4, где вырабатываются сигналы считывания информации с той части блока запоминания, которая определяется старшим разрядом адреса. Считанная информация через группу элементов ИЛИ 8 поступает на входы блока 7 контроля совместно с сигналом с выхода второго элемента И 11, а также на выходной регистр 9 числа. Предлагаемое изобретение позволяет обнаруживать одиночные ошибки « без использования дополнительного

5 контрольного разряда, что приводит к уменьшению оборудования, а значит к повышению надежности устройства. Кроме того, снижается стоимость запоминающего устройства.

Формула изобретения

Запоминающее устройство с обнаружением одиночных ошибок, содержащее

5 адресный регистр, первые выходы

которого подключены к первым входам адресного дешифратора, первый накопитель , адресные входы которого подключены к выходам адресного дешифQ ратора, в его информационные входы являются информационными входами устройства, блок управления, первый выход которого подключен к первому управляющему входу первого накопие теля, и блок контроля, о т л и ч аю щ е е.с fj«s тем, что, с целью повышения надежности устройства, в него, введены второй накопитель, адресные входы которого подключены к выходам адресного дешифратора, информационные входы - к информационным, входам первого накопителя, а первый управляющий вход - к первому выходу блока управления, формирователь контрольного разряда, входы которого подключены к информационным входам первого накопителя, первый элемент И, первый вход которого подключен к выходу формирователя контрольного разряда, а второй вход - к первому

0 выходу блока управления, второй элемент И, первый вход которого подключен ко второму выходу адресного регистра, а выход - к первому входу блока контроля, элемент ИЛИ,

е первый вход которого подключен к выходу первого элемента И, а второй вход - к выходу второго элемента И, а выход элемента ИЛИ подключен ко второму входу адресного дешифратора, группу элементов ИЛИ, первые входы

0 которых подключены к выходам первого накопителя, а вторые входы - к выходам второго накопителя, выходы группы элементов ИЛИ подключены ко вторьш входам блока контроля и являются выходами устройства, второй выход блока управления подключен ко второму входу второго элемента И и ко вторым управляющим входам первого и второго накопителей.

Источники информации, принятые во внимание при экспертизе

li Авторское свидетельство СССР ( 333599, кл. G 11 С 29/00, 1972.

2. Путинцев В.Д. Аппаратный контроль управляющих цифровых вычислительных машин. М., Советское радио 1966 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправ-лЕНиЕМ ОшибОК | 1979 |

|

SU841059A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство с контролем и коррекцией информации | 1983 |

|

SU1109809A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1522293A1 |

Авторы

Даты

1981-08-15—Публикация

1979-08-30—Подача