(54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| Источник калиброванных напряжений | 1979 |

|

SU860025A2 |

| Источник калиброванных напряжений | 1981 |

|

SU1029155A2 |

| Источник калиброванных напряжений | 1980 |

|

SU877500A1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Адаптивный временных дискретизатор | 1974 |

|

SU660239A1 |

| Цифро-аналоговый регулятор для интегрирующего электропривода | 1980 |

|

SU954928A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

I

Устройство относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. № 758О95 известен источник калиброванных напряжений, содержащий бпок опорного напряжения, последовательно включенные коммутатор и два блока интегрирования, преобразователь кода во временной интервал, регистр памяти, блок управления, преобразователь код-напряжение и аналоговый сумматор, в котором первый и второй входы коммутатора соответст венно связаны с выходом блока опорного напряжения и входом аналогового сумматора, а входы управления коммутатора через блок управления связаны с выходом преобразователя кода во временной интервал, первый и второй входы аналогового сумматора соответственно подключены к выходу преобразователя код-напряжение и выходу второго блока интегрирования, а выход. сумматора связан с выходом устройства, вход регистра памяти связан с входной клеммой устройства, соответствующие выходы регистра подключены к входам преобразователей код-напряжение и кода во временной интервал, а вход синхронизации регистра памяти, вход сброса, первого блока интегрирования и вход управления второго блока интегрирования соединены с .соответствующими выходами второго блока интегрирования.

10

Недостатком известного устройства является его низкое быстродействие.

Цель изобретения - увеличение быстродействия.

Поставленная цель достигается тем,

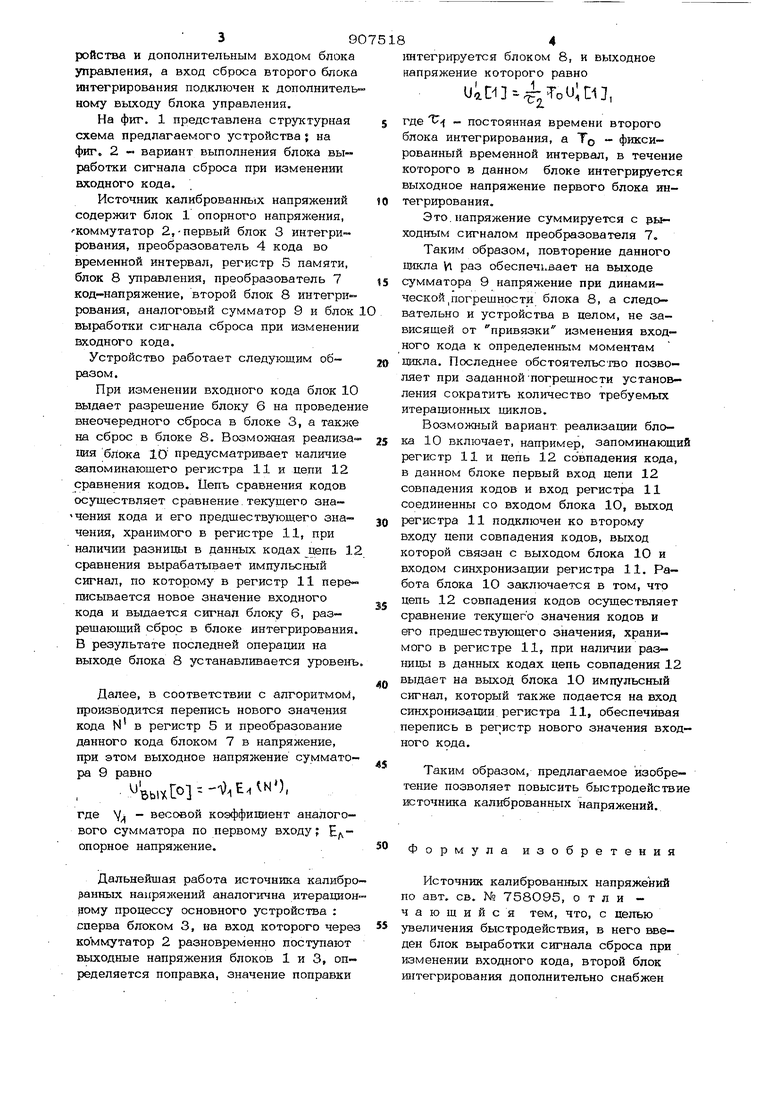

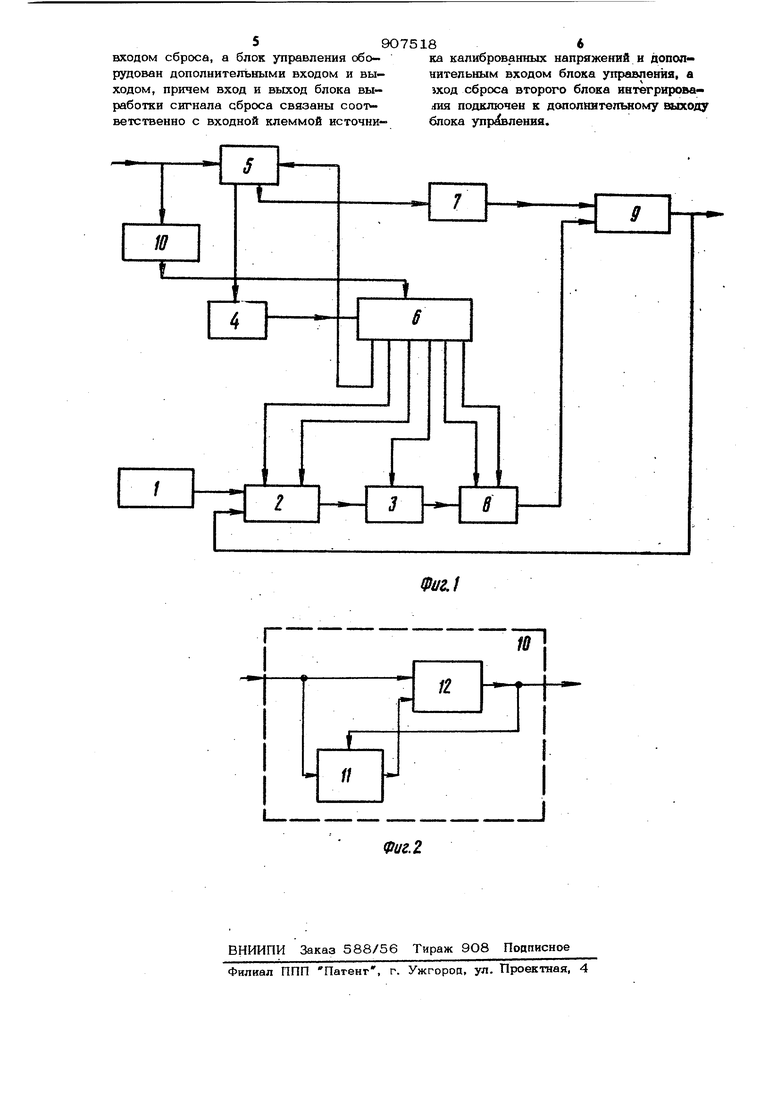

15 что р источник калиброванных напряжений введен блок выработки сигнала сброса при изменении входного кода, второй блок интегрирования дополнительно снабжен входом сброса, а блок уп:оравления оборудован Дополнительными входом и выходом, причем вход и выход блока выработки сигнала сброса связаны соответственно с входной клеммой уст- ройства и дополнительным входом блока управления, а вход сброса второго бгюка интегрирования подключен к допопнитель ному выходу блока управления. На фиг. 1 представлена структурная схема предлагаемого устройства ; на фиг. 2 вариант выполнения блока вы работки сигнала сброса при изменении входного кода. Источник калиброваннь1Х напряжений содержит блок 1 опорного напряжения, Коммутатор 2,-первый блок 3 интегрирования, преобразователь 4 кода ео временной интервал, регистр 5 памяти, блок 8 управления, преобразователь 7 код-напряжение, второй блок 8 интегрирования, аналоговый сумматор 9 и блок выработки сигнала сброса при изменении входного кода. Устройство работает следующим обПри изменении входного кода блок 10 выдает разрешение блоку 6 на проведени внеочередного сброса в блоке 3, а также на сброс в блоке 8. Возможная реализация блока 10 предусматривает наличие запоминающего регистра 11 и цепи 12 сравнения кодов. Цепъ сравнения кодов осуществляет сравнение текущего зна- чения кода и его предшествующего значения, хранимого в регистре 11, при наличии разнипы в данных кодах цепь 12 сравнения вырабатывает импульсный сигнал, по которому в регистр 11 переписывается новое значение входного кода и выдается сигнал блоку 6, разрешающий сброс в блоке интегрирования В результате последней операции на выходе блока 8 устанавливается уровень Далее, в соответствии с алгоритмом, производится перепись нового значения кода N в регистр 5 и преобразование данного кода блоком 7 в напрянсение, при этом выходное напряжение сумматора 9 равно -),E,IN), где VH весовой коэффициент аналогового сумматора по первому входу; Едопорное напряжение. Дальнейщая работа источника калибро Эанных напряжений аналопгчна итерацион ному процессу основного устройства : сперва блоком 3, на вход которого чере коммутатор 2 разновременно поступают выходные напряжения блоков 1 и 3, определяется поправка, значение поправки 1П1тегрируется блоком 8, и выходное напряжение которого равно u;D3--4-2 ou;nij, где C-t - постоянная времени второго блока интегрирования, а TQ - фиксированный временной интервал, в течение которого в данном блоке интегрируется выходное напряжение первого блока интегрирования. Это. напряжение суммируется с рыходным сигналом преобразователя 7. Таким образом, повторение данного цикла VI раз обеспечивает на выходе сумматора 9 напряжение при динамической погрешности блока 8, а следовательно и устройства в целом, не зависящей от привязки изменения входного кода к определенным моментам цикла. Последнее обстоятельство позволяет при заданнойпогрещности установления сократить количество требуемых итерационных циклов. Возможный вариант реализации блока 10 включает, например, запоминающий регистр 11 и цепь 12 совпадения кода, в данном блоке первый вход цепи 12 совпадения кодов и вход регистра 11 соединенны со входом блока 1О, выход регистра 11 подключен ко второму входу цепи совпадения кодов, выход которой связан с выходом блока 10 и входом синхронизации регистра 11. Работа блока 10 заключается в том, что цепь 12 совпадения кодов осуществляет сравнение текущего значения кодов и его предшествующего значения, хранимого в регистре 11, при наличии разницы в данных кодах цепь совпадения 12 выдает на выход блока 10 импульсный сигнал, который также подается на вход синхронизации регистра 11, обеспечивая перепись в регистр нового значения входного кода. Таким образом, предлагаемое изобретение позволяет повысить быстродействие источника калиброванных напряжений. Формула из р е т е н и я Источник калиброванных напряжений по авт. св. № 758095, отличающийся тем, что, с целью увеличения быстродействия, в него i eдбн блок выработки сигнала сброса при изменении входного кода, второй блок интегрирования дополнительно снабжен

входом сброса, а блок управления оборудован дополнительными входом и выходом, причем вход и выход блока выработки сигнала сброса связаны соо- ветственно с входной клеммой источника калиброванных напряжений и допол нительным входом блока управления, а 1ход сброса второго блока интегрирова ЛИЯ подключен к дополнвтелыюму выходу блока упр ления.

Авторы

Даты

1982-02-23—Публикация

1980-04-29—Подача