i - . Изобретение относится к электротехнике, в частности к источникам калиброванных напряжений, и преднаэ- начено для использования в электротехнических установках различного назначения.

Известен источник калиброванных напряжений, представляющий собой итерационный широтно-импульсный преобразователь опорного напряжен;ия Ij. Недостатком данного устройства являются пульсгщии выходного напряжения, обусловленные саморазрядом накопительного элемента в аналоговом запоминающем устройстве на выходеитерационного преобразователя.

Наиболее близким к предлагаемому по технической сущности является источник калиброванных напряжений, содержащий регистр памяти, первый выход которого через преобразователь код-напряжение подключен к первому входу аналогового сумматора, второй, выход регистра памяти соединен со входом преобразователя кода во временной интервал, последовательно соединенные первый и второй блоки интегрирования, причем вход синхронизации регистра памяти, вход сброса первого блока интегрирования и вход

управления второго блока интегрирования подключены к соответствующим , выходам блока управления, а выход второго блока интегрирования соединен со вторым входом аналогового сумматора, и опорный элемент 121 .

Недостатком этого устройства является невысокая линейность выходной характеристики источника калиброванных напряжений.

Цель изобретения - повышение линейности шлходной характеристики источника ка шброванных напряжений.

Поставленная цель достигается тем, что в источник калиброванных напряжений введены преобразователь напряжения в ток, два ключевых элемента, а опорный элемент выполнен в виде источника опорного тока, причем вход преобразователя напряжения в ток. соединен с выходной клеммой, а выход этого преобразователя и выход источника опорного ioKa через соответствующие первый и второй ключевой элемент подключены ко входу первого блока интегрирования, при этом ynpaisляюадий вход второго ключевого элемента соединен с выходом преобразо- ателя кода во временной интервал, а управляющий вход первого ключевого

элемента подключен к дополнительному выходу блока управления.

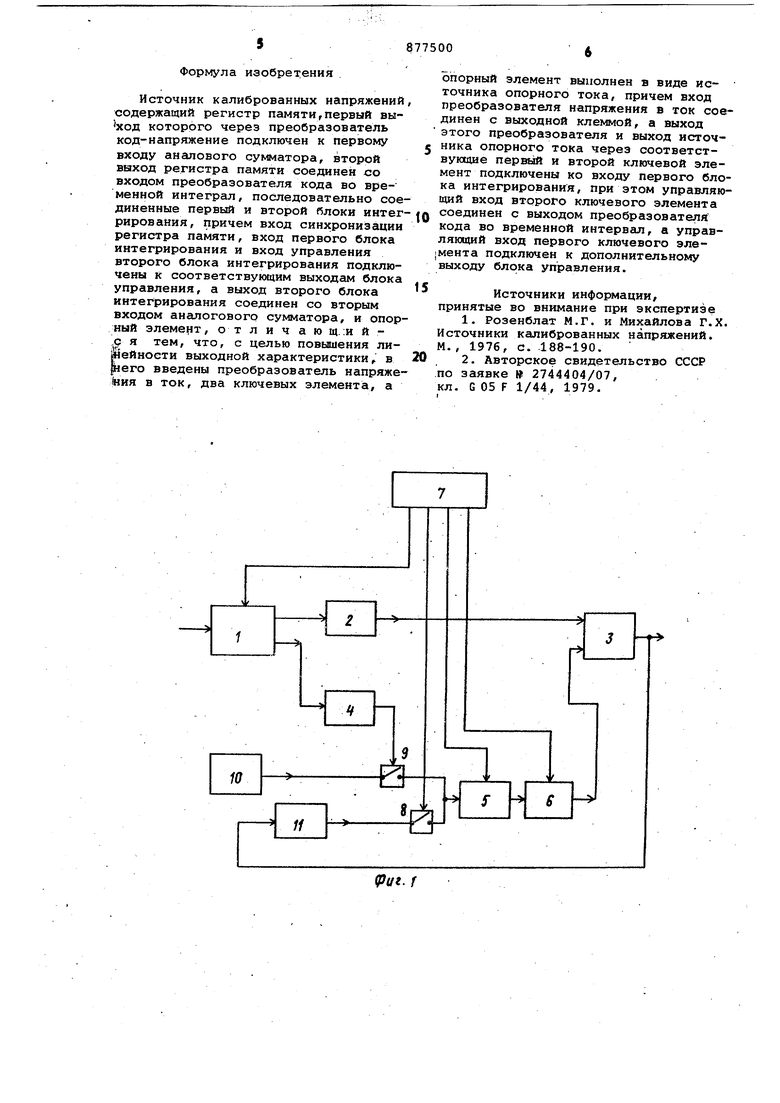

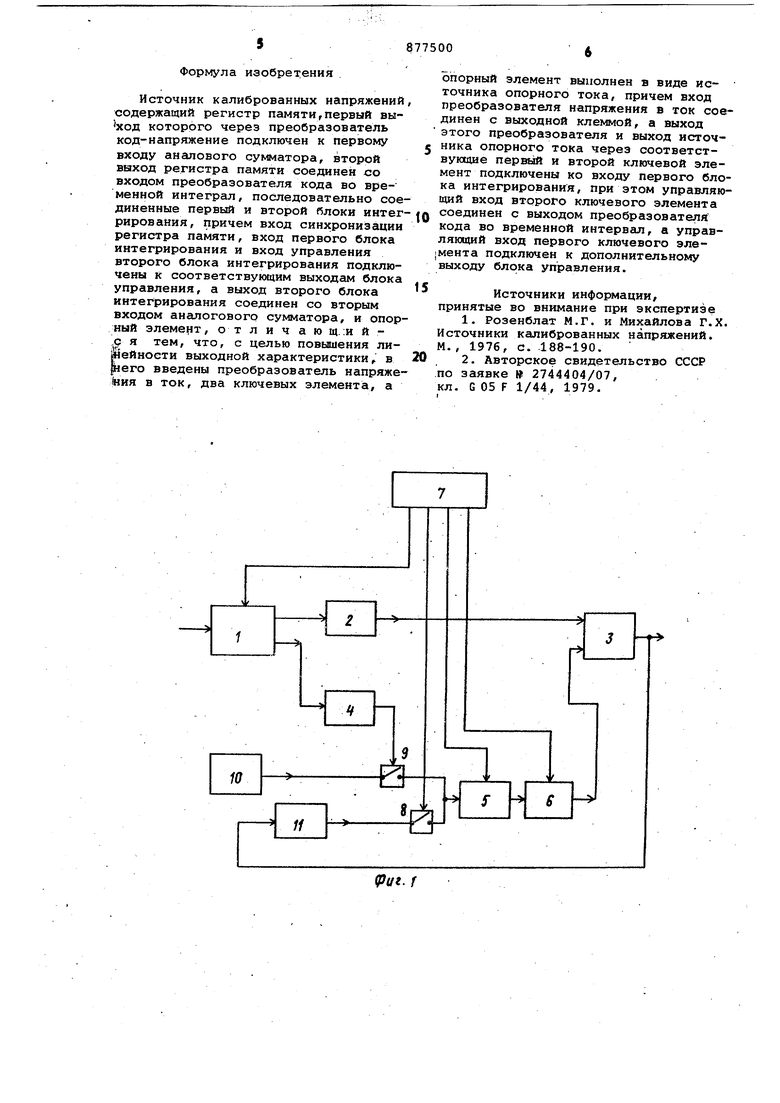

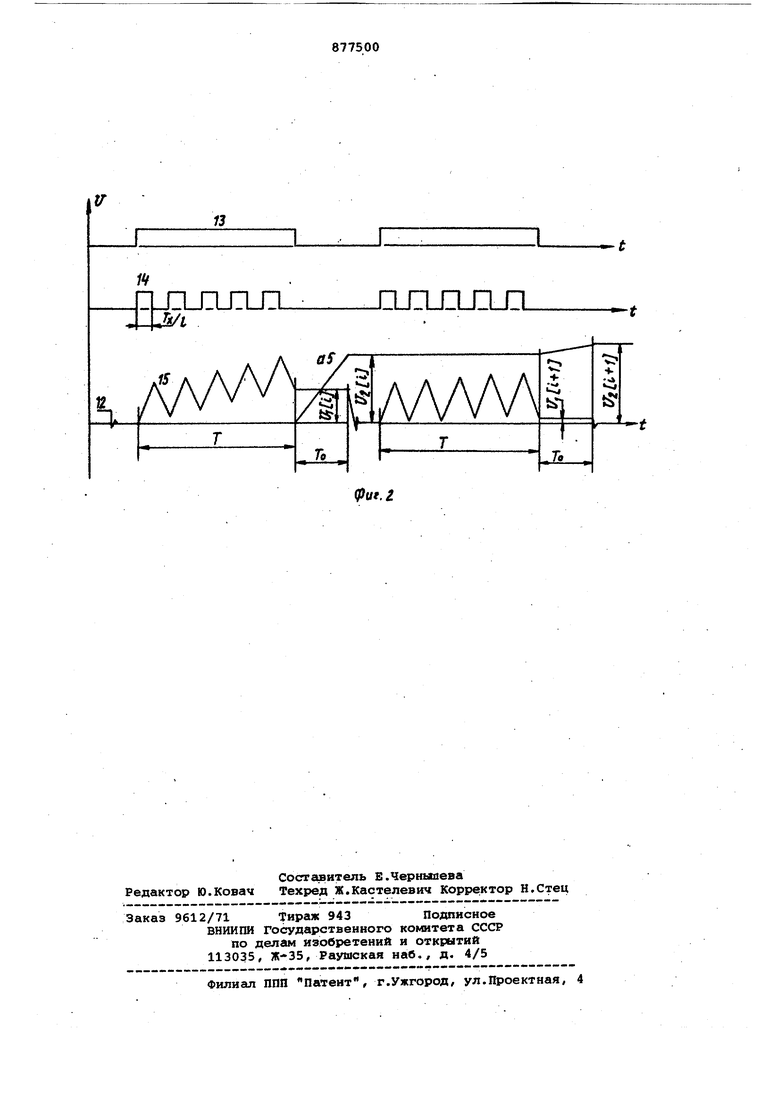

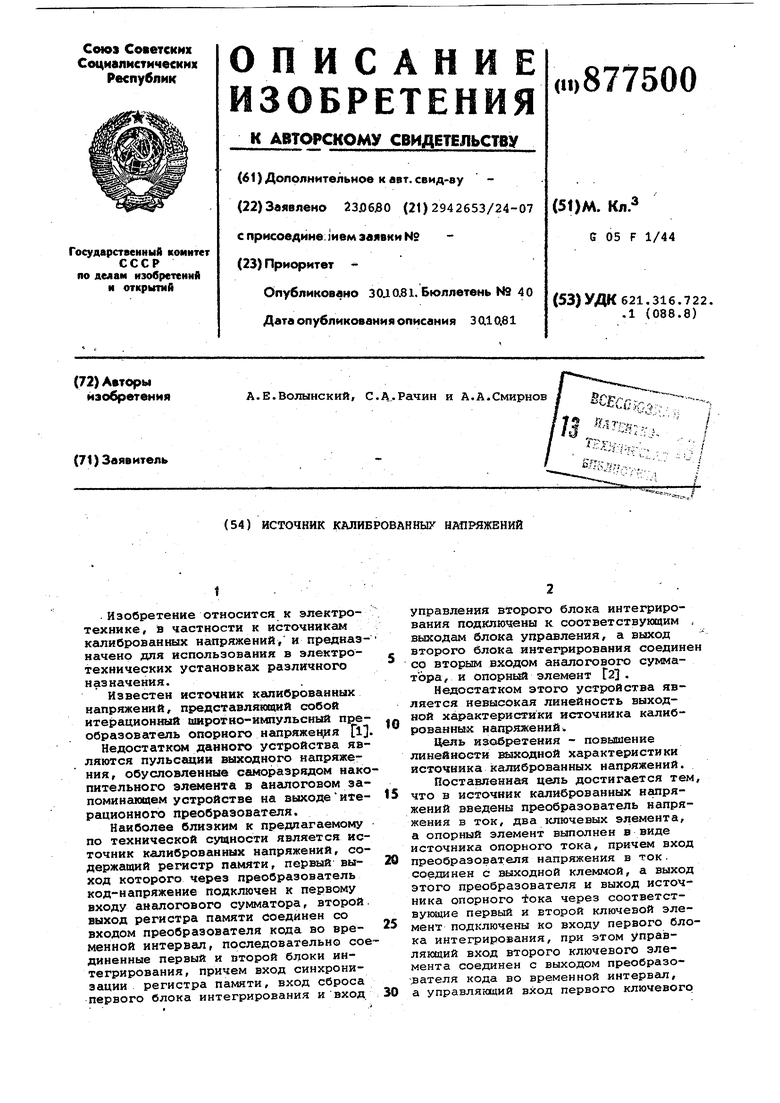

На фиг. 1 приведена структурная схема источника калиброванных напряжений; на фиг. 2 - временные диаграммы, поясняющие его работу.

Источник калиброванных напряжений содергшт регистр 1 памяти, преобразователь 2 код-напряжение, аналоговый сумматор 3, преобразователь 4 кода во временной интервал, первый 5 и второй б блоки интегрирования, блок 7 управления, первый 8 и второй 9 ключевые элементы, источник 10 опорного тока и преобразователь 11 напряжения в ток.

Устройство работает следующим образом.

По команде блока 7 входной код переписывается в регистр 1, при этом на выходе преобразователя 2 устанавливается пропорциональное данному коду напряжение Е..

Выходное напряжение сумматора 3 в произвольный момент времени определяется выражением

U6bix(t)V,)aU2(t) ,

где Un(t)- напряжение на выходе блока 6 ;

tf и коэффициенты передачи сумматора 3 по соответствующим входам.

Процесс установления выходного напряжения устройства носит итерационный характер и осуществляется в течение п циклов. В произвольном i-ом цикле (1-1,п)в начале производится сброс блока 5 (изменение выходного сигнала блока 5 показано на диаграмме кривой 12) и далее блоком 7 выдается непрерывный временной интервал длительности. Т, в течение которого замыкается, элемент 8 (замкнутое состояние ключевого элемента 8 условно показано кривой 13), в течение указанного интервала выходной ток преобразователя 11 пропорциональный выходному напряжению сумматора 3

) подается во входную цепь блока 5 и интегрируется. Одновременно с выдачей блоком 1 данного интервала преобразователем 4 формируется последовательность из равномерно расставленных временных, интервалов, длительность каждого из которых пропорциональна входному коду регистра 1 (на диаграмме последовательность интервалов, формируемая преоб разователем 4, условно показана им:пульсс1ми 14) . Эта последовательность подается,на вход управления ключево го элемента 9, обеспечивая периодическое поступление импульсов тока 7 источника 10 во входную цепь блока 5 где происходит их алгеб1эаическое су1Л 1ирование с выходным током преобразователя 11. В результате на вы(ХОде блока 5 формируется пилообразное напряжение с возрастающей амплитудой (на диаграмме обозначено 15), значение которого к концу данной части цикла равно

Ci3--sue,,,).;(o)j+3bt ;(:.;(f - :§LJJ,

где S - крутизна преобразователя 11, а символом h(t) обозначена переходная функция блока 5 относительно токового входного сигнала.

в оставшейся части цикла выходное напряжение блока 5 интегрируется блоком 6 в течение постоянного временного интервала длительностиТ (изменение выходного сигнала блока б

в этой части цикла обозначено на

диаграмме кривой а5). Результат данного интегрирования

,(T)(o). : (Т-Й1

где Гл - постоянная времени интегрирования блока б (служит как ив известном поправкой к выходному напряжению преобразователя 2).

На выходе сумматора 3 при этом формируется напряжение

. (Т)-Ь(0)х xs|o,)-i;(lf-f)JJ ,

Jebix 3 ifi % ato - исходное

значение сигнала на выходе сумматора 3.

При определенных условиях можно показать, что выходное напряжение устройства после нескольких циклов сходится к установившемуся значению

, ).

;tT)-h(o) VtT.

Таким образом, введение в состав устройства источника опорного тока,

преобразователя напряжения в ток, двух ключевых элементов и организация с из помощью параллельного интегрирования токов, соответствующих опорному и выходному сигналам, позволяет в отличие от известного поддерживать напряжение накопительного конденсатора блока 5 в течение цикла на сравнительно низком уровне (данное напряжение в известном достигает 10 В, тогда как в предлагаемом устройстве

эта величина на 1-2 порядка меньше). При этом соответственно уменьшается паразитный заряд, запасаемый в абсорбционной емкости и, следовательно, составляющая погрешности линейности, обусловленная данным фактором. Формула изобретения Источник калиброванных напряжений содержащий регистр памяти,первый выЫод которого через преобразователь код-напряжение подключен к первому входу аналового сумматора, второй выход регистра памяти соединен со входом преобразователя кода во временной интеграл, последовательно сое диненные первый и второй блоки интег рирования, причем вход синхронизации регистра памяти, вход первого блока интегрирования и вход управления второго блока интегрирования подключены к соответствующим выходам блока управления, а выход второго блока интегрирования соединен со вторым входом аналогового сумматора, и опор ный элемент, о т л и ч а ю щ.:и и р я тем, что, с целью повышения ли {ейности выходной характеристики, в pjero введены преобразователь напряже ия в ток, два ключевых элемента, а опорный элемент выполнен в виде источника опорного тока, причем вход преобразователя напряжения в ток соединен с выходной клеммой, а выход этого преобразователя и выход источника опорного тока через соответствующие первьй и второй ключевой элемент подключены ко входу первого блока интегрирования, при этом управляющий вход ВТОРОГО ключевого элемента соединен с выходом преобразователя кода во временной интервал, а управляющий вход первого ключевого элемента подключен к дополнительному выходу блока управления. Источники информации, принятые во внимание при экспертизе 1,Розенблат М.Г. и Михайлова Г.Х. Источники кгшиброванных напряжений. М. , 1976, с. .188-190. 2.Авторское свидетельство СССР по заявке 2744404/07, кл, G 05 F 1/44, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник калиброванных напряжений | 1981 |

|

SU1029155A2 |

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| Источник калиброванных напряжений | 1979 |

|

SU860025A2 |

| Источник калиброванных напряжений | 1980 |

|

SU907518A2 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Калибратор напряжения | 1984 |

|

SU1244646A1 |

QJX IILQJIl

Авторы

Даты

1981-10-30—Публикация

1980-06-23—Подача