(54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Источник калиброванных напряжений | 1981 |

|

SU1029155A2 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| Источник калиброванных напряжений | 1980 |

|

SU907518A2 |

| Источник калиброванных напряжений | 1980 |

|

SU877500A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Преобразователь активной мощности в цифровой код | 1986 |

|

SU1366960A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

I

Изобретение относится к электротехнике, в частности к источникам калиброванных напряжений.

По основному авт. св. № 758095 известен источник калиброванных напряжений, содержащий блок опорного напряжения, коммутатор, два блока интегрирования, преобразователь кода во временной интервал, регистр памяти, преобразователь код-напряжение, аналоговый сумматор и блок управления, причем первый и второй входы коммутатора соответственно связаны с выходами блока опорного напряжения и аналогового сумматора, выход коммутатора через последовательно включенные блоки интегрирования связан со вторым входом аналогового сумматора, а первый и второй входы управления коммутатора через блок управления связаны с выходом преобразователя кода во временной интервал, вход регистра памяти соединен со входной клеммой, а его соответствующие выходы подключены ко входам преобразователя кода во временной интервал и преобразователя «код-напряжение, выход преобразователя «коднапряжение соединен с первым входом

аналогового сумматора, выход последнего связан с выходной клеммой, а вход сброса первого блока интегрирования, вход управления второго блока ннтегрирования н вход синхронизации регистра памяти соединены с с соответствующими выходами блока управления 4.

Устройство работает следующим образом.

Текущее значение сигнала на выходе

аналогового сумматора Uebixlt) является

взвещенной суммой выходного сигнала преобразователя «код-напряжение EI и выходного напряжения второго блока интегрирования U2(t) и устанавливается за несколько циклов. В течение каждого i-ro цикла производится начальный сброс первого блока интегрирования и на его выходе фор мируется функция поправки в виде напряжения

Jln -: ETx+Ueb« i-l T + + MTx+l)},(1)

20

гдеТ1 - постоянная времени данного блока; е - напряжение смещения блока; Е - опорное напряжение;

Т и TX -постоянный и переменный временные интервалы, причем последний вырабатывается пропорционально коду «11 регистра памяти преобразователем кода во временной интервал.

Полученная таким путем функция поправки интегрируется далее в течение постоянного временного интервала TO вторым блоком интегрирования с постоянной времени Та, а результат интегрирования суммируется в данном устройстве с величиной Uali-1.

Ui(i -, (2)

Данное напряжение воздействует с весом )г на выходное напряжение устройства, которое при выполнении условия (1 ) 1 и при -е о быстро сходится к установившемуся значению

II- F Тх

(3)

.уст Е. ,

Однако с учетом напряжения смещения первого блока интегрирования ( е У 0) в последнее выражение вносится погрешность, относительная величина которой 5 -1(1 +

+ ) зависит от нестабильного параметра е

1х

и, следовательно, не может быть устранена одноразовой настройкой первого блока интегрирования.

Цель изобретения - повышение точности источника калиброванных напряжений.

Поставленная цель достигается тем, что в источник калиброванных напряжений введен второй коммутатор, первый блок интегрирования дополнительно снабжен инверсным входом, второй блок интегрирования дополнительно снабжен вторым входом управления, а блок управления - тремя дополнительными выходами, причем первый и второй входы второго коммутатора соединены с соответствующими входами первого коммутатора, выход второго коммутатора подключен к инверсному входу первого блока интегрирования, а три дополнительных выхода блока управления соответственно связаны с первым и вторым управляющими входами второго коммутатора и вторым входом управления второго блока интегрирования.

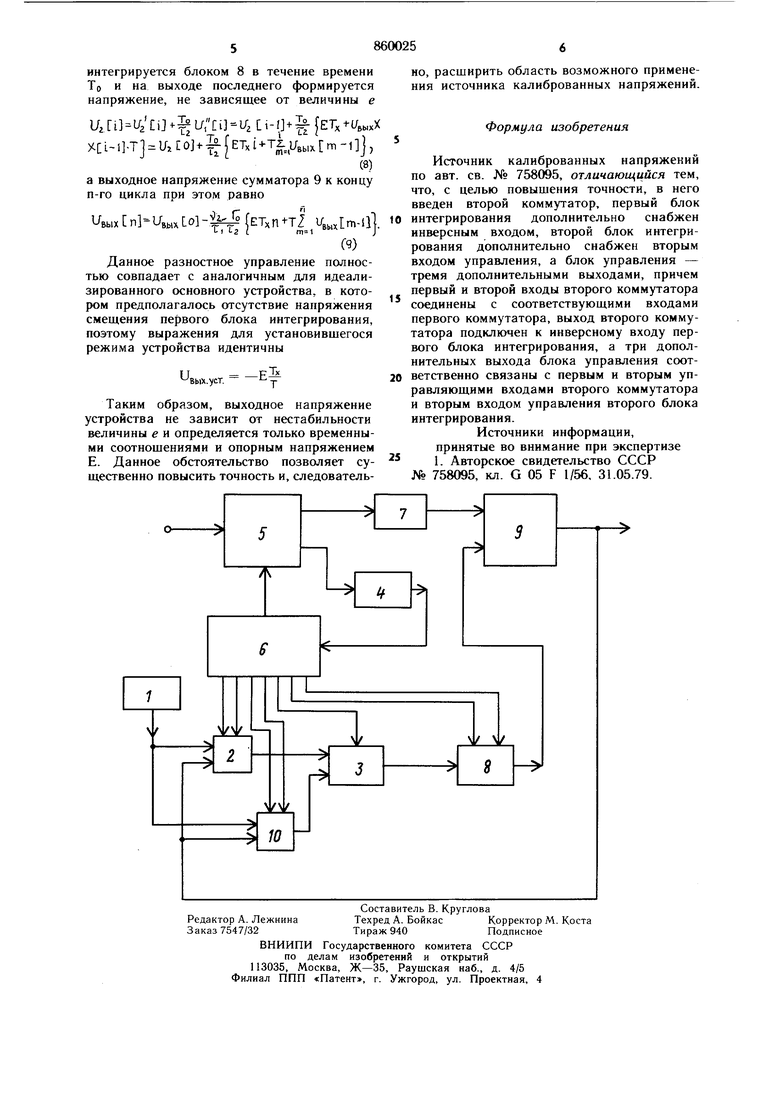

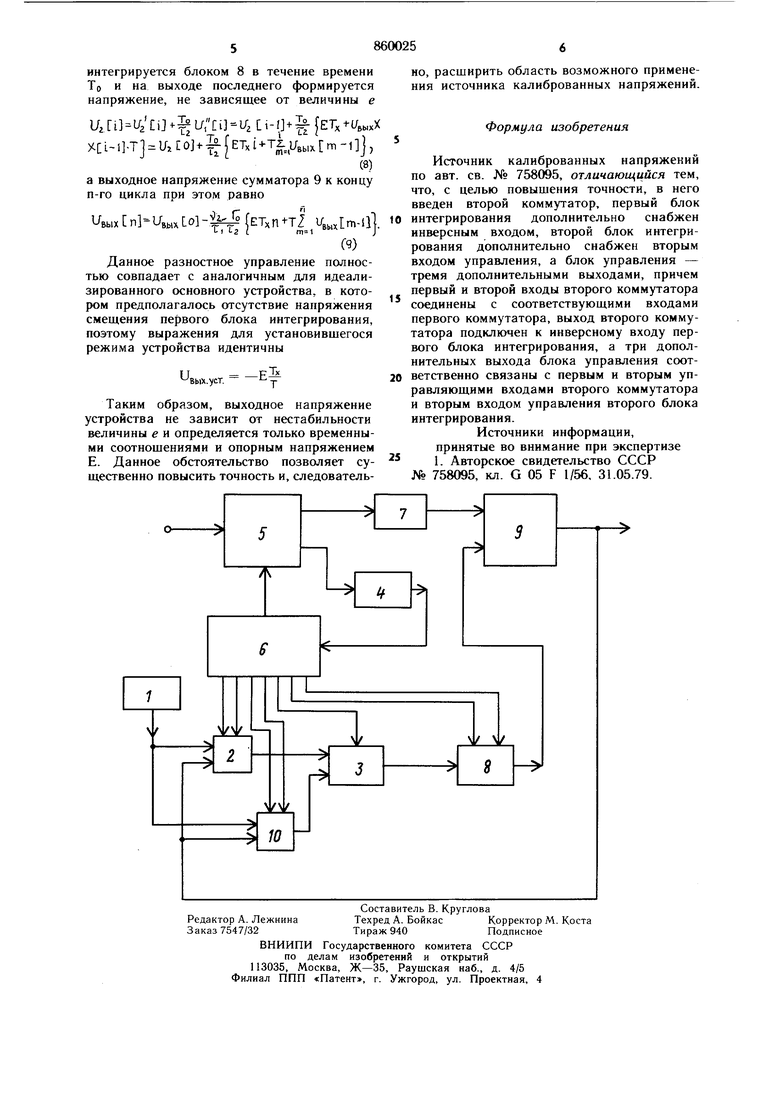

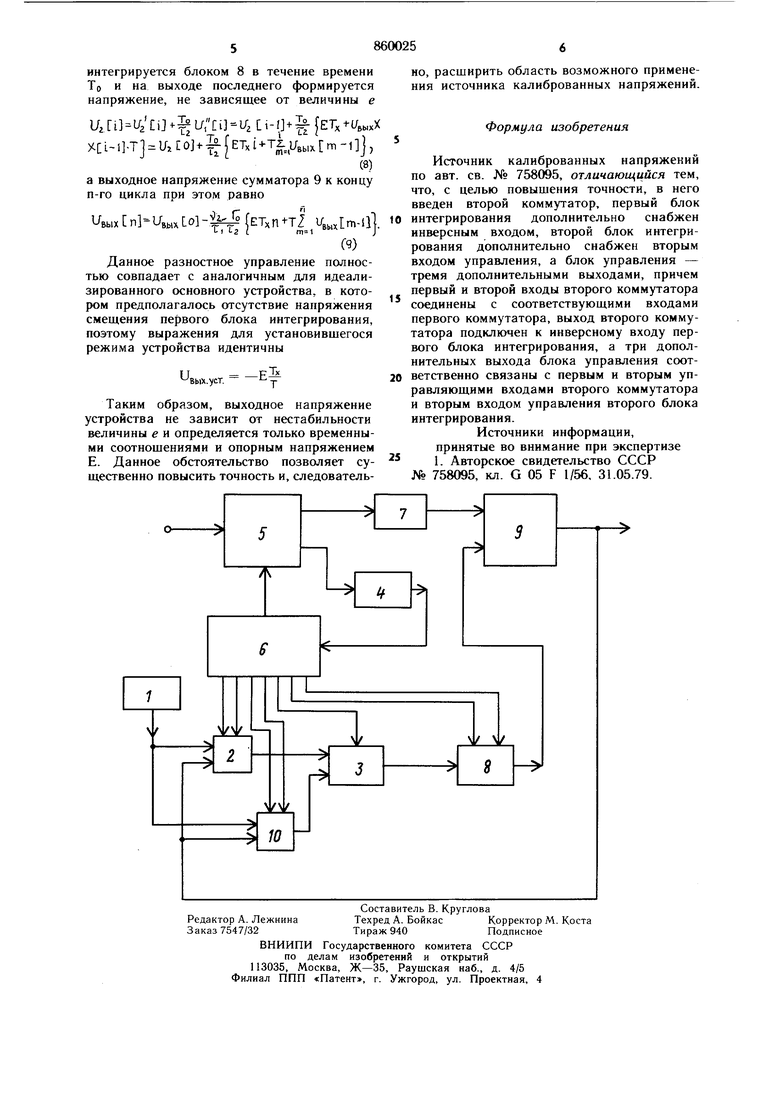

На чертеже приведена структурная схема предлагаемого устройства.

Источник калиброванных напряжений содержит блок 1 опорного напряжения, коммутатор 2, первый блок 3 интегрирования, преобразователь 4 кода во временной интегвал, регистр 5 памяти, блок 6 управления, преобразователь 7 «код-напряжение, второй блок 8 интегрирования, аналоговый сумматор 9, второй коммутатор 10.

Устройство работает следующим образо.ч.

По команде управления блока 6 входной код «11 переписывается в регистр 5 памяти, при этом на выходе преобразователя 7 «коднапряжение устанавливается пропорциональное данному коду напряжение Е(, а выходное напряжение сумматора 9 определяется выражением

UWt) ViE,-/zUa(t),(4)

где 1/2 (t) - напряжение на выходе блока 8; )| vj коэффициенты передачи сумматора 9 по соответствующим входам.

Итерационный процесс установления выходного напряжения подобно основному устройству осуществляется в течение п циклов, однако в каждом i-ом цикле процесс интегрирования соответствующих сигналов блоками 3 и 8 занимает два равных по длительности такта. В начале первого такта производится сброс первого блока 3 интегрирования, а по окончании сброса выход блока 1 опорного напряжения через коммутатор 2 подключается ко входу блока 3, и опорное напряжение Е интегрируется в течение интервала времени TX /2. Данный

интервал, пропорциональный коду N, вырабатывается как и в основном устройстве преобразователем 4 и подается на соответствующий управляющий вход коммутатора 2. По окончании данной части такта вход блока 3 через коммутатор 2 подключается к выходу сумматора 9 и производится интегрирование выходного напряжения последнего UgbK i - Ц в течение постоянного временного интервала Т/2. К концу данного интервала напряжение на выходе блока 3

имеет вид

ц - , . U... |.(Т, .Т),(5)

Данное напряжение поступает на вход блока 8 и интегрируется в течение времени То, на выходе последнего при этом формируется напряжение

-То , г г; 1fe)

(f,,

Далее начинается второй такт, в начале которого производится сброс блока 3, направление интегрирования блока 8 по сравненню с первым тактом меняется блоком 6 на противоположное и выход блока 1 через

второй коммутатор 10 в течение интервала Тх/2 подключается к инверсному входу блока 3, а в оставшейся части такта инверсный вход блока 3 через коммутатор 10 в течение интервала Т/2 подключается к выходу сумматора 9. Полученное в результате данных операций выходное напряжение блока 3

; ,.-l.J.(т..т)5дт)

интегрируется блоком 8 в течение времени TO и на выходе последнего формируется напряжение, не зависящее от величины е

UJt -l/2CiJ l/,Ci UzCi-U + S-fE:Tx t/,b.xX XCL-l -T -U..y,,,,m-l,

а выходное напряжение сумматора 9 к концу п-го цикла при этом равно

ъш п -ивых 01- (ЕТхП nZ 4jb.xlm-a.

L- 1 З 1J

С9)

Данное разностное управление полностью совпадает с аналогичным для идеализированного основного устройства, в котором предполагалось отсутствие напряжения смещения первого блока интегрирования, поэтому выражения для установивщегося режима устройства идентичны

I т рТх

вых.уст. у

Таким образом, выходное напряжение устройства не зависит от нестабильности величины е и определяется только временными соотнощениями и опорным напряжением Е. Данное обстоятельство позволяет существенно повысить точиость и, следовательно, расширить область возможного применения источника калиброванных напряжений.

Формула изобретения

Источник калиброванных напряжений по авт. св. № 758095, отличающийся тем, что, с целью повышения точности, в него введен второй коммутатор, первый блок

интегрирования дополнительно снабжен инверсным входом, второй блок интегрирования дополнительно снабжен вторым входом управления, а блок управления - тремя дополнительными выходами, причем первый и второй входы второго коммутатора соединены с соответствующими входами первого коммутатора, выход второго коммутатора подключен к инверсному входу первого блока интегрирования, а три дополнительных выхода блока управления соответственно связаны с первым и вторым управляющими входами второго коммутатора и вторым входом управления второго блока интегрирования.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 758095, кл. G 05 F 1/56, 31.05.79.

Авторы

Даты

1981-08-30—Публикация

1979-09-13—Подача