Изобретение относится к передаче данных и может использоваться в синх ронных системах передачи разного тип Известно устройство цикловой синхронизации, содержащее первый элемент И, регистр сдвига, выходы которого подключены ко входгил первого даиифратора, выход которого подключен к первому входу второго элемента И, второй вход которого объединен с первыми входами первого элемента И, элемента НЕТ и первым выход 1 распределителя импульсов, причем выход элемента НЕТ подключен к первому входу первого накопителя, к второму входу кЪторого подключен выход второго накопителя, а также блок вцдепения тактовой частоты и кодовый разделитель, первый вход которог го объединен со входами регистра сдвига и блока выделения тактовой ча стоты, выход которого подключен к первому входу распределителя импульсов, выходы которого подключены соответственно ко входам кодового разделителя (il Однако это устройство обладает ни кой помехоустойчивостью и низким быстродействием. Цель изобретения - повышение быстродействия и помехоустойчивости. Цель достигается тем, что в устройство цикловой синхронизации, содержёицее. первый элемент И, регистр сдвига, выходы которого подключены ко входам первого дешифратора, выход которого подключен к первому входу второго элемента И, второй вход . которого объединен с первыми входами первого элемента И, элемента НЕТ и первым выходом распределителя импульсов, причем выход элемента НЕТ подключен к первому входу первого накопителя, к второму входу которого подключен выход второго накопителя , а также блок выделения тактовой частоты и кодовый разделитель, первый вход которого объединен со входами регистра сдвига и блока выделения тактовой частоты, выход которого подключен к первому входу распределителя импульсов, выходы которого пйдключешл соответственно ко входам кодового разделителя, введены второй дешифратор, блок проверки чередования кодов и элемент ИЛИ, выход которого подключен к второму входу распределителя импульсов, при этом входы второго дешифратора объединены

соответственно со входами первого дешифратора, а выход второго дешифратора nojc. очен к второму входу первого элеме. .а И, выход которого подключен к первому входу блока проверки чередования кодов, к второму и третьему входам которого подключены соответственно выход второго элемента И и второй выход блока выделения тактовой частоты, а выход блока проверки чередования кодов подключен к первому входу элемента ИЛИ, третьему входу первого накопителя, второму входу элемента НЕТ, а также к первому входу второго накопителя, к второму и третьему входам которого подключены соответственно выход элемента НЕТ и первый выход первого накопителя, .второй выход которого подключен к второму входу элемента ИЛИ, причем второй выход первого накопителя и выход второго накопителя подключены к соответствугацим входам кодового разделителя.

Кроме того, блок проверки чередования кодов содержит элементИЛИ, а также две цепи, каждая из которых состоит из последовательно соединенных триггера, первого элемента И и второго элемента И, выходы каждого из которых подключены к первым входам триггеров соответствующей цепи, при этом выходы.первых элементов И каждой цепи подключены к первому и второму входам элемента ИЛИ, причем второй вход триггера первой цепи подключен к второму входу первого элемета И второй цепи и является первым входом блока проверки чередования кодов , а второй вход триггера второ цепи подключен ко второму входу первого элемента И первой цепи и.является вторым входом блока проверки чередования кодов, третьим входом которого являются объединенные вторы входы вторых элементов И каждой цепи

Причем в устройство цикловой синхронизации могут быть введены второй дешифратор, блок проверки чередования кодов и элемент ИЛИ, выход которого подключен к второму входу распределителя импульсов, при этом входы второго дешифратора объединены соответственно со входами первого дешифратора, а выход второго дешифратора подключен к второму входу первого элемента И, выход которого подключен к первому входу блока проверки чередования кодов, к второму входу которого подключен выход второго элемента И, а выход блока проверки чередования кодов подключен к первому входу элемента ИЛИ, третьему входу первого накопителя, второму входу элемента НЕТ, а также к первому входу второго Накопителя, к второму и третьему входам которого подключены соответственно выход элемента НЕТ и первый выход первого накопителя, второй выход которого подключен к второму входу элемента ИЛИ, причем второй выход первого накопителя и выход второго накопителя подключены к-соответствующим входам кодового разделителя.

Кроме того, блок проверки чередовния кодов содержит элемент ИЛИ и две цепи, каждая из которых состоит из последовательно соединенных триггера |И элемента И, выходы каждого из которых подключены к первому входу триггера соответствующей цепи и первому и второму входам элемента ИЛИ, при этом второй вход триггера первой цепи подключен к второму входу элемента И второй цепи и является первым входом блока проверки чередования кодов, а второй вход триггера .второй цепи подключен к второму входу элемента И первой цепи и является вторы входом блока проверки чередования . кодов.

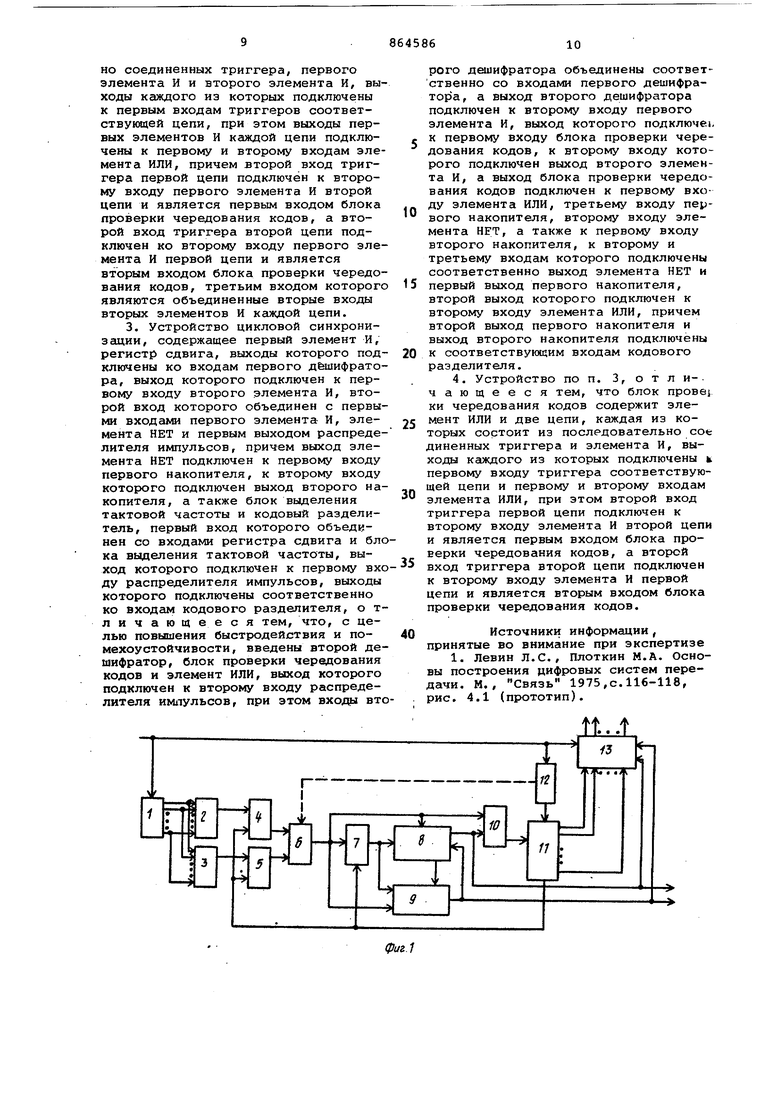

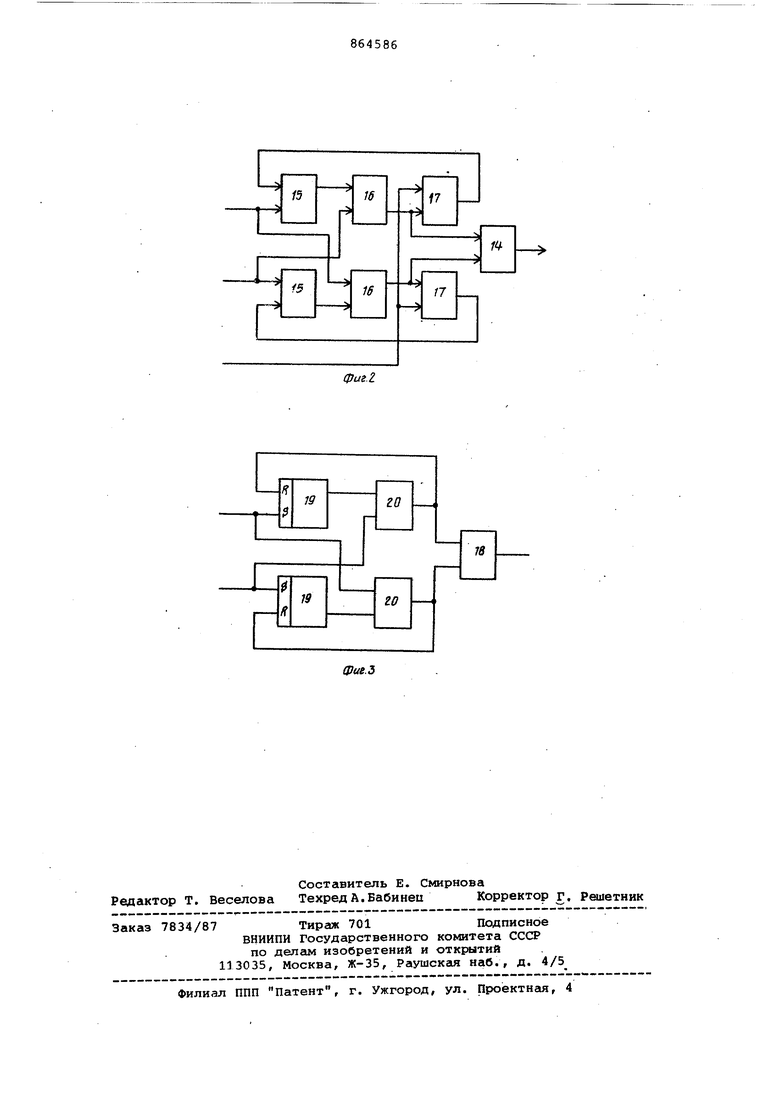

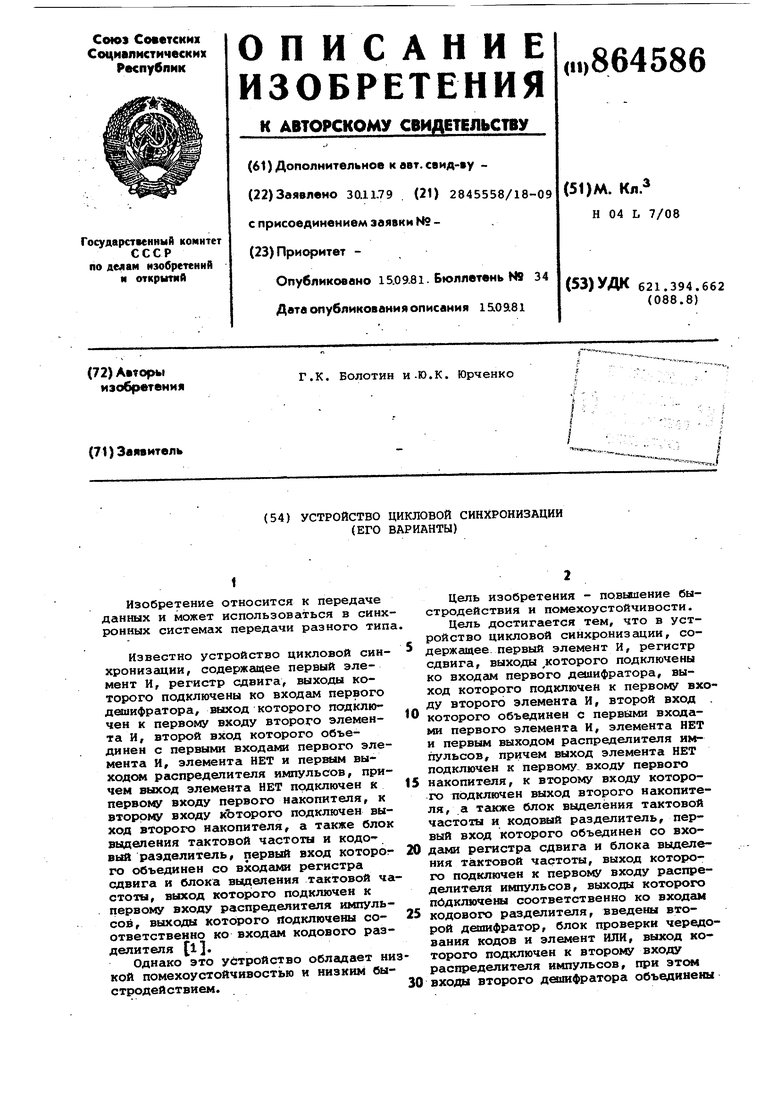

На фиг. 1 приведена структурная электрическая схема устройства цикловой синхронизации, где пунктирной линией показана связь, наличие или отсутствие которой соответствует первому или второму варианту устройства на фиг.2 и 3 варианты структурной электрической схемы блока проверки чередования колов.

Устройство цикловой синхронизации (фиг. 1) содержит регистр сдвига 1, первый и второй дешифраторы 2 и 3, первый и второй элемент И 4 и 5, блок 6 проверки чередования кодов, элемент НЕТ 7, первый и второй накопители 8 и 9, элемент ИЛИ 10, распределитель импульсов 11, блок 12 выделения тактовой частоты и кодовый разделитель 13. Блок 6 проверки чередования кодов (фиг. 2) содержит элемент ИЛИ 14, а также две цепи, каждая .из которых содержит триггер 15, первый элемент И 16, второй элемент И 17. БЛОК б проверки чередования кодов (фиг. 3) содержит элемент ИЛИ 18 и две цепи, каждая из которых содержит триггер 19 и элемент И 20.

Устройство работает следующим об разом. ,

Групповой.цифровой сигнал(непрерывная последовательность бинарных единиц и нулей) поступает на регистр

I,кодовый разделитель 13 и блок 12 выделения тактовой частоты, который осуществляет выделение из группового сигнала тактовой частоты (частота телеграфирования), которая необходима для работы распределителя импульсов

II.Поступакашй групповой сигнал продвигается по разрядам регистра 1. С выхода регистра 1 комбинации принимаемых элементов сообщения(посылок

в параллельном коде поступают на входы дешифраторов 2 и Д. Каждая комбинация симоволов на входах дешифраторов 2 и 3, аналогичная одной из фазирующих комбинаций, вызывает формирование сигнала на выходе соответствуидего дешифратора 2 или 3.

Если устройство находится в состоянии синхронизма, то отдельные сигналы с выходов дешифраторов 2 и 3 совпадают по времени с тактовым сигналом распределителя импульсов 11, поступающим один раз за цикл. При этом на выходах соответствующих элементов И 4 и 5 попеременно (через один цикл) появляются сигналы, соответствующие по времени моменту опоз|Нания фазирующих комбинаций. Блок 6 осуществляет проверку чередования . поступающих на его входы сигналов. Сигнал на выходе схемы появляется только при чередовании сигналов на ее входе.

При наличии сигналов в каждом цикле на выходе блока 6 сигналы на выходе элемента НЕТ отсутству зт. Поэтому накопитель 8 не заряжен и сигнал на выходе накопителя 8 отсутствует. Так как в случае синфазной работы сигналы на входе элемента НЕТ 7 присутствуют в каждом цикле, а сигналы на выходе элемента НЕТ 7 отсутствуют, то накопитель 9 заряжается и на его выходе появляется сигнал синфазной работы. Этот сигнал разрешает декодирование информации, поступающей в кодовый разделитель 13 и ее выдачуна выход разделителя 13, разрешает работу накопителя 8 (переводит его в режим готовности к поддержанию синфазной работы, т.е. разрежает заряд накопителя 8)и вьвдается наружу, т.е. на другие устройства приемной части аппаратуры, например индикацию.

Кроме того,сигналы с выхода блока б поступают на элемент ИЛИ 10. Выходные сигналы с выхода элемента ИЛИ 10 осуществляют запуск распределителя импульсов 11, который управляет записью и декодированием информации в кодовом разделителе 13. Таким образом, запуск распределителя ,импульсов 11 осуществляется один раз в начсше цикла принимаемого ГРУППОВОГО сигнсша в одни и те же моменты времени, т.е. устройство находится в состоянии синфазной работы.

Ложные синхрогруппы, аналогичные фазирующим комб инациям и вьщеленные дешифраторами 2 и 3 из группового сигнала вследствие случайного сочетания нулей и единиц информации в групповом сигнале, не совпадают по времени с сигналом на входе элементов И 4 и 5, формируемым один раз за цикл и, следовательно, не проходят через элементы И 4 и 5 и не участвуют в процессе работы блока б, накопителей 8 и 9 и разделителя импульсов 11.

При кратковременных искажениях фазирукяцих комбинаций (.например, из-за

воздействия помех или при сбоях синхронизации в системах более высокого порядка) сигнал на выходе блока 6 временно отсутствует. В этом случае элемент НЕТ 7 оказывается открытым и сигнал с выхода распределителя импульсов 11, формируемой в конце цикла работы распределителя импульсов 11 (фактически при его остановке) , поступает через элемент НЕТ 7 на накопители 8 и 9. Этот сигнал срабаты10вает счетную схему накопителя 9 в .нулевое-состояние, но уровень сигнала синфазной работы на выходе накопителя 9 остается,так как его сброс осуществляется лишь при поступлении сигнала сброса на выход накопителя 8.

15

Так как на выходе накопителя 9 присутствует сигнал, разрешающий работу накопителя 8, то сигнал с выхода элемента НЕТ 7 проходит через накопитель 8 на вход разделителя 13,

0 одновременно заряжая накопитель 8 на одну единицу. Этот сигнал, проходя через элемент ИЛИ 10, запускает распределитель импульсов 11 на следующий цикл работы. Таким обра5зом, запуск распределителя импульсов 11 проходит . тот же момент времени, что и при наличии фазирующих комбинаций, поэтому нарушения синхронизма не происходит и устройство

D продолжает работу уже в состоянии поддержания синхронизма.

Кроме того, сигнал автозапуска поступает на вход кодового разделителя 13 и выдается наружу, т.е. на

5 другие устройства приемной части аппаратуры, например индикацию. В ;зависимости от режима работы кодового разделителя 13 сигнал автозапуска- либо не оказывает влияния на его работу, либо (режим повышенной до0стоверности) запрещает декодирование и выдачу информации на выход разделителя 13. ,

В случае отсутствия фазирующих комбинаций в следующих циклах работа

5 продолжается аналогичным образом до тех пор, пока накопитель 8 не окажется заряженным. Появление до этого момента времени сигнала на выходе блока б (т.е. обнаружение комбинаций

0 на прежних временных позициях) приводит к сбросу ранее заряженного накопителя 8 в нулевое состояние. Этот же сигнал через элемент ИЛИ 10 объединения проходит на распределитель

5 импульсов 11, запуская его. Таким образом, устройство вновь переходит в режим синфазной работы.

Если теперь вновь происходит кратковременное пропадение фазирующих

0 комбинаций, то работа устройства ничем не отличается от описанной, т.е.устройство вновь переходит в peжи поддержания синфазной работы.

При отсутствии сигналов на выходе блока 6 в 01 подряд следукиих

5

циклах (гдеТо - коэффициент накопления накопителя В),т.е. при зарядке накопителя 8 на его выходе формируется импульс сброса, который переводит накопитель 9 в нулевое состояние В результате на его выходе появляется нулевой уровень и, следовательно, кодовый разделитель 13 прекращает декодирование информации и ее выдачу на выход. Кроме того, отсутствие сигнала на выходе накопителя 9 закрывает вход накопителя 8, т.е. выводит его из состояния готовности к поддержанию синфазной работы. Таким образом, состояние синфазной работы устройства нарушается и оно переходит в режим поиска синхронизма. При этом фазирующие комбинации, содержащиеся в групповом сигнале, выделяются даиифраторами и поступают через элементы И 4 и 5 на блок 6.

В случае чередования выделившихся комбинадий сигнал с выхода блока 6 поступает на вход накопителя 9, заряжая его, и через элемент ИЛИ 10 на вход распределителя импульсов 11, осуществляя его запуск.

Если обнаруженные комбинации, аналогичные фазирующим, сформируются на одних и тех же временных позициях в циклах принимаемого группового сигнаша меньше, чем Сд раз а подряд (гдеТог коэффициент накопления накопителя 9), то накопитель 9 продолжает оставаться разряженным и сигнал синфазной работы на его выходе отсутствует. Поэтому накопитель 8 не готов к поддержанию .синфазной работы В этом случае при отсутствии сигнала на выходе блока б элемент НЕТ 7 оказывается открытым и тактовый сигнал распределителя импульсов 11 с-его выхода проходит на вход накопителя 8 и сбрасывает счетную накопителя 9 в нулевое состояние. Однако из-за неготовности к работе накопителя 8 сигналы с выхода элемента НЕТ 7 не проходят через накопитель 8 на элемент ИЛИ 10 и, следовательно, запуск распределителя импульсов 11 на прежних временных позициях не производится , т.е. устройство продолжает находиться в режиме поиска синхронизма, и поиск фазирующих комбинаций осуществляется на отличных от предьш х временных позициях цикла.

Если на выходе блока б сигналы формируются на одних и тех же позициях цикла TOZ а подряд, то накопитель 9 заряжается и на его выходе формируется уровень сигнала синфазной работы. Таким образом, устройство переходит в (ежям синфазной работы. Теперь в случае искажения фазирующих комбингидий нгисопитель 8 вновъ пропускает сигналы с выхода элемента НЕТ 7 на элемент ИЛИ 10, т.е. осуществляется запуск распределителя импульсов 11, а устройство

работает в режиме поддержания синхронизма.

Предложенное устройство обеспечивает повышение помехоустойчивости путем уменьшения.вероятностей ложного фазирования приемника и слиибочного декодирования информации.

Формула изобретения

1. Устройство цикловой синхронизации, содержащее первый элемент И; регистр сдвига, выходы которого подключены ко входам первого дешифратор выход которого подключен к первому входу второго элемента И, второй вхо которого объединен с первыми входг1ми первого элемента И, элемента НЕТ и первым выходом распределителя импульсов, причем выход элемента НЕТ подключен к первому входу первого накопителя, к второму входу которого подключен выход второго накопителя, а также блок выделения тактовой частот и кодовый разделитель, первый вход которого объединен со входами регистра сдвига и блока выделения тактовой частоты, выход которого подключе к первому входу распределителя импульсов, выходы которого подключены соответственно ко входам кодового разделителя, отличающеесЯ тем,что, с целью повышения быстродействия и помехоустойчивости, введены второй дешифратор, блок проверки чередования кодов и элемент ИЛИ, выход которого подключен к второму входу распределителя импульсов, при этом входы второго дааифратора объединены соответственно со входами дешифратора, а второго дешифратора подключен к второму входу первого элемента И, выход которого подключен к первому входу блока проверки чередования кодов, к второму и третьему входам которого подключены соответственно выход второго элемента И и второй выход блока выделения тактовой частоты, а выход блока проверки чередования кодов подключен к первому входу элемента ИЛИ, третьему входу первого накопителя, второму входу элемента НЕТ, а также к первому входу второго накопителя, к второму и третьему входам которого подключены соответственно выход элемента НЕТ и первый выход первого накопителя, второй выход которого подключен ,к второму входу элемента ИЛИ, причем второй выход первого накопителя и выход второго накопителя подключены к соответствующим входам кодоврго разделителя.

2. Устройство по п. 1, отличающееся тем, что блок проверки чередования кодов содержит элемент ИЛИ, а также две цепи, каждая из которых состоит из последовательно соединенных триггера, первого элемента И и второго элемента И, выходы каждого из которых подключены к первым входам триггеров соответствуняцей цепи, при этом выходы первых элементов И каждой цепи подключены к первому и второму входам элемента ИЛИ, причем второй вход триггера первой цепи подключён к второму входу первого элемента И второй цепи и является первым входом блока проверки чередования кодов, а второй вход триггера второй цепи подключен ко второму входу первого элемента И первой цепи и является вторым входом блока проверки чередования кодов, третьим входом которого являются объединенные вторые входы вторых элементов И Кс1ждой цепи. 3. Устройство цикловой синхронизации, содержащее первый элемент И, регистр сдвига, выходы которого подключены ко входам первого дешифратора, выход которого подключен к первому входу второго элемента И, второй вход которого объединен с первыми входами первого элемента И, элемента НЕТ и первым выходом распределителя импульсов, причем выход элемента НЕТ подключен к первому входу первого накопителя, к второму входу которого подключен выход второго на копителя, а также блок выделения тактовой частоты и кодовый разделитель, первый вход которого объединен со входами регистра сдвига и бл ка выделения тактовой частоты, выход которого подключен к первому вх ду распределителя импульсов, выходы которого подключены соответственно ко входам кодового разделителя, о т личающееся тем, что, с целью повышения быстродействия и помехоустойчивости, введены второй де шифратор, блок проверки чередования колов и элемент ИЛИ, выход которого подключен к второму входу распределителя ИМ11УЛЬСОВ, при этом входы ВТ рого дешифратора объединены соответственно со входами первого дешифратора, а выход второго дешифратора подключен к второму входу первого элемента И, выход которого подключен к первому входу блока проверки чередования кодов, к второму входу которого подключен выход второго элемента И, а выход блока проверки чередования кодов подключен к первому входу элемента ИЛИ, третьему входу первого накопителя, второму входу элемента HFT, а также к первому входу второго накопителя, к второму и третьему входам которого подключены соответственно выход элемента НЕТ и первый выход первого накопителя, второй выход которого подключен к второму входу элемента ИЛИ, причем второй выход первого накопителя и выход второго накопителя подключены к соответствующим входам кодового разделителя. 4. Устройство по п. 3, о т л и-. чающееся тем, что блок npoBSj ки чередования кодов содержит элемент ИЛИ и две цепи, каждая из которых состоит из последовательно cofe диненных триггера и элемента И, выходы каждого из которых подключены ь. первому входу триггера соответствующей цепи и первому и второму входам элемента ИЛИ, при этом второй вход триггера первой цепи подключен к второму входу элемента И второй цепи и является первым входом блока проверки чередования кодов, а второй вход триггера второй цепи подключен к второму входу элемента И первой цепи и является вторым входом блока проверки чередования кодов. Источники информации , принятые во внимание при экспертизе 1, Левин Л.С., Плоткин М.А. Основы построения цифровых систем передачи. М. , Связь 1975,с.116-118, рис. 4.1 (прототип). tt. .t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU1341727A2 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Авторы

Даты

1981-09-15—Публикация

1979-11-30—Подача