Изобретение относится к передгше даннык и может быть использовано для обеспечения циклового фазирования синхронных систем связи.

Цель изобретения - сокращение времени установления циклового фазирования.

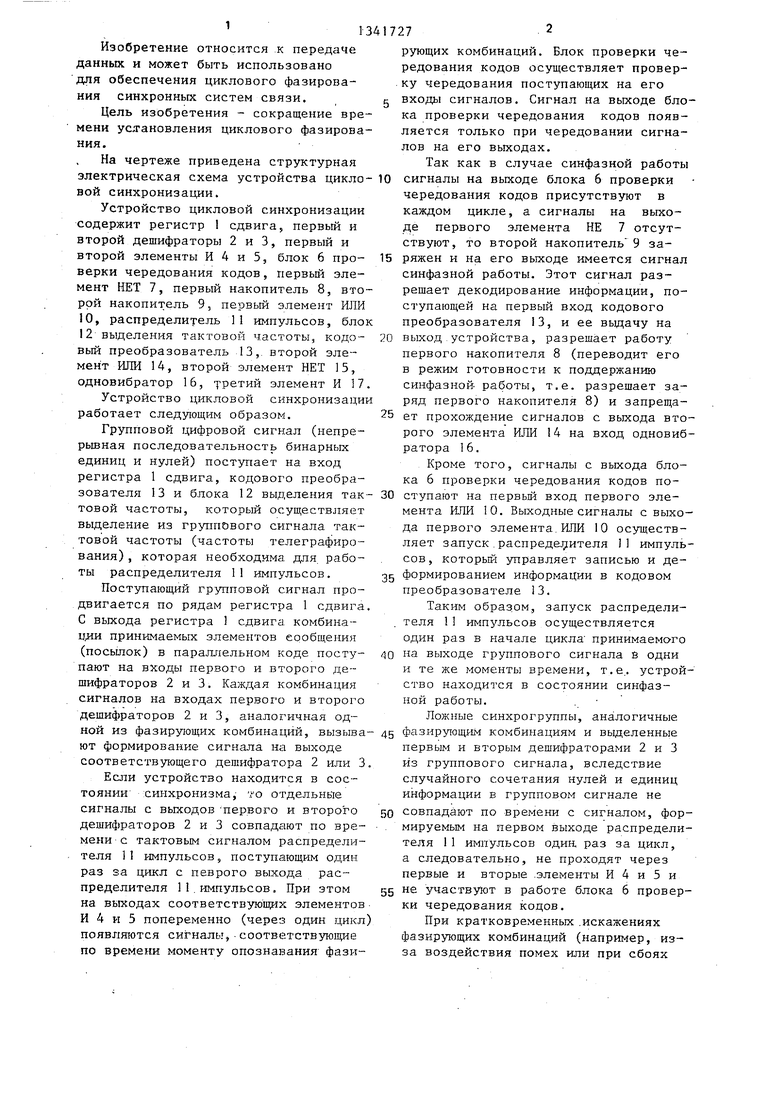

На чертеже приведена структурная

электрическая схема устройства цикло- 10 сигналы на выходе блока 6 проверки

вой синхронизации.

Устройство цикловой синхронизации содержит регистр 1 сдвига, первьй и второй дешифраторы 2 и 3, первый и второй элементы И 4 и 5, блок 6 про- верки чередования кодов, первый элемент НЕТ 7, первый накопитель 8, второй накопитель 9, первый элемент ИЛИ 10, распределитель 11 импульсов, блок 12 выделения тактовой частоты, коде- вый преобразователь 13,. второй элемент ИЛИ 14, второй элемент НЕТ 15, одновибратор 16, третий элемент И 17.

Устройство цикловой синхронизации работает следующим образом.

Групповой цифровой сигнал (непре- рьшная последовательность бинарных единиц и нулей) поступает на вход регистра 1 сдвига, кодового преобразователя 13 и блока 12 выделения так- 30 ступают на первьй вход первого элетовой частоты, который осуа ествляет выделение из группового сигнала тактовой частоты (частоты телеграфирования) , которая необходима для работы распределителя 11 импульсов.

Поступающий групповой сигнал продвигается по рядам регистра 1 сдвига С выхода регистра 1 сдвига комбина- ид1и принимаемых элементов сообщения (посьшок) в параллельном коде поступают на входы первого и второго дешифраторов 2 и 3. Каждая комбинация сигналов на входах первого и второго дешифраторов 2 и 3, аналогичная одной из фазирующих комбинаций, вызывают формирование сигнала на выходе соответствующего дешифратора 2 или 3

Если устройство находится в состоянии :синхронизма, отдельные сигналы с выходов первого и второго дешифраторов 2 и 3 совпадают по времени с тактовым сигналом распределителя 11 импульсов, поступающим один раз за цикл с певрого выхода распределителя 11.импульсов. При этом на выходах соответствующих элементов И 4 и 5 попеременно (через один цикл появляются сигналы,соответствуюище по времени моменту опознавания фазирующих комбинаций. Блок проверки чередования кодов осуществляет провер- ку чередования поступающих на его входы сигналов. Сигнал на выходе блока проверки чередования кодов появляется только при чередовании сигналов на его выходах.

Так как в случае синфазной работы

чередования кодов присутствуют в каждом цикле, а сигналы на выходе первого элемента НЕ 7 отсутствуют, то второй накопитель 9 заряжен и на его выходе имеется сигнал синфазной работы. Этот сигнал разрешает декодирование информации, поступающей на первый вход кодового преобразователя 13, и ее выдачу на выход.устройства, разрешает работу первого накопителя 8 (переводит его в режим готовности к поддержанию синфазной- работы, т.е. разрешает заряд первого накопителя 8) и запрещает прохождение сигналов с выхода второго элемента ИЛИ 14 на вход одновиб- ратора 16.

Кроме того, сигналы с выхода блока 6 проверки чередования кодов помента ИЛИ 10. Выходные сигналы с выхода первого элемента.ИЛИ 10 осуществляет запуск . pacпpeдeJ итeля 11 импульсов, которью управляет записью и деg формированием информации в кодовом преобразователе 13.

Таким образом, запуск распределителя 11 импульсов осуществляется один раз в начале цикла принимаемого

0 на выходе группового сигнала в одни и те же моменты времени, т.е.. устройство находится в состоянии синфазное работы.

Ложные синхрогруппы, аналогичные

5 фазирующим комбинациям и выделенные первым н вторым дешифраторами 2 и 3 из группового сигнала, вследствие случайного сочетания нулей и единиц информации в групповом сигнале не совпадают по времени с сигналом, формируемым на первом выходе распределителя 11 импульсов один, раз за цикл, а следовательно, не проходят через первые и вторые .элементы И 4 и 5 и не участв Лот в работе блока 6 проверки чередования кодов.

При кратковременных .искажениях фазирующих комбинаций (например, из- за воздействия помех или при сбоях

0

5

3

синхронизации в системах более высокого порядка) сигнал на выходе блока 6 проверки чередования кодов временно отсутствует. В этом первый элемент НЕТ 7 оказывается открытым и сигнал с первого выхода распределителя II импульсов, формируемый в конце цикла работы распределителя I импульсов (фактически при его ос- тановке), поступает через первый элемент НЕТ 7 на вторые выходы первого и второго накопителей 8 и 9, Этот сигнал сбрасывает счетную схему второго накопителя 9 в нулевое состоя- ние. Уровень сигнала синфазной работы на его выходе остается, так как его сброс осуществляется лишь при поступлении сигнала сброса с первого выхода первого накопителя 8,

Так как на выходе второго накопителя 9 присутствует сигнал, разрешающий работу первого накопителя 8, то сигнал с выхода первего элемента НЕТ 7 проходит через первый накопи- таль В на автозапуск, одновременно заряжая первьш накопитель 8 не одну единицу. Этот сигнал, проходя через первый элемент ИЛИ 10,запускает распределитель 1 1 импульсов на следую- щий цикл работы.

Таким образом, запуск распределителя 11 импульсов происходит в тот же момент времени, что и при наличии фазирующих комбинаций. Поэтому нарушение синхронизма не происходит и устройство продолжает работу в состоянии поддержания синхронизма. Кроме того, сигнал автозапуска с второго выхода первого накопителя поступа ет на третий вход кодового преобразователя 13.

В зависимости от режима работы кодового преобразователя 13 сигнал автозапуска либо не оказывает влияни на его работу, либо (режим повьшен- ной достоверности) запрещает детектирование и выдачу информации на выход устройства.

В случае отсутствия фазирующих комбинаций в следующих циклах работа продолжается аналогичным образом до тех пор, пока первый накопитель 8 не окажется заряженным. Появление до этого момента времени сигнала на выходе блока 6 проверки чередования кодов (т.е. обнаружение фазирующих комбинаций на прежних време.нных позициях) приводит к сбросу ранее за

5 0

5 о

д

g

5

727

ряженного первого накопителя 8 в нулевое состояние. Этот же сигнал через первьш элемент ИЛИ 10 проходит на первый вход распределителя 11 импульсов, запуская его. Таким образом, устройство вновь переходит в режим синфазной работы.

При отсутствии сигналов на выходе блока 6 проверки чередования кодов в I подряд следующих циклах (где I - коэффициент накопления первого накопителя 8), т.е. при заряде первого накопителя 8, на его первом выходе формируется импульс сброса, которьм переводит второй накопитель 9 в нулевое состояние. В результате на выходе второго накопителя 9 появляется нулевой уровень, а следовательно, кодовый преобразователь 13 прекращает декодирование информации и ее выдачу на выход устройства. Кроме того, отсутствие сигнала на выходе второго накопителя 9 выводит первый накопитель 8 из состояния готовности к поддержанию синфазной работы и разрешает прохождение сигналов через второй элемент НЕТ 15.

В режиме поиска синхронизма работа устройства осуществляется следующим образом.

Вследствие остановки распредели- , теля 11 импульсов на его первом выходе присутствует уровень напряжения, разрешающий прохождение сигналов через первый и второй элементы И 4 и 5. Поэтому при вьщелении первым или вторым дешифратором 2 или 3 из состава принимаемых элементов сообщения одной из комбинаций, аналогичных фази- . рующим, на выходе второго элемента ИЛИ 14 формируется сигнал, поступающий на первьш вход второго элемента НЕТ 15.

Вследствие отсутствия сигнала синфазной работы на выходе второго накопителя 9, второй элемент НЕТ 15 оказывается открытым и сигнал с его выхода поступает на второй вход третьего элемента И 17 и на вход одно- вибратора 16. Так как одновибратор 16, формирующий при его запуске сигнал напряжения логического нуля, срабатывает с некоторой задержкой, сигнал с выхода второго элемента НЕТ 13 проходит через третий элемент И 17 на его выход и поступает на третий вход первого элемента ИЛИ 10. Вследствие этого происходит пробный

запуск распределителя 11 импульсов. Одновременно сигнал об обнаружении комбинации, аналогичной фазирующей, с выхода одного из элементов И 4 или 5 поступает на соответствующий вход блока 6 проверки чередования кодов. Пробньм запуск распределителя 1 i им-пульсов приводит к тому, что сигнал на его первом выходе сменяется нулевым уровнем, который сохраня- ,ется до момента времени, соответствующего остановке распределителя 11 импульсов (т.е. в течение одного цикла работы). Поэтому элементы И 4 и 5 оказьшаются закрытыми. Выделение дешифраторами 2 и 3 комбинаций, аналогичных фазирующим и расположенных во времени внутри цикла работы кодового преобразователя 13, не оказывает -влияния на работу блока проверки чередования кодов.

134J727

Процесс работы продолжается аналогично, вплоть до появления сигнала на выходе второго накопителя,

,- свидетельствующего о вхождении аппа- 5

ратуры в синхронизм и закрывающего

второй элемент НЕТ 15.

10

20

30

40

Пусть, например, пробный запуск распределителя 1 1 импульсов проводит- , ся сигналом с выхода второго дешифратора 3 через второй элемент И 5, второй элемент ИЛИ 14, третий элемент И 17, первый элемент ИЛИ 10. Спустя время, равное длительности цикла принимаемых элементов сообщения, распределитель 11 импульсов возвращается в.исходное состояние и на его первом выходе появляется уровень напряжения, разрешающий прохождение сигналов через первый и второй элементы И 4 и 5.

Если в этот момент времени комбинация, аналогичная фазирующей, выделяется первым дешифратором 2 (т.е. происходит смена фазирующей комбинации) , срабатывает блок б проверки чередования кодов, вследствие чего на его выходе формируется сигнал, запускающий распределитель 11 импульсов для работы на прежних временных позициях и записьшающий единицу во второй накопитель 9. В следующем цикле работы в момент формирования разрушающего сигнала на выходе распределителя 11 импульсов формируется 50 сигнал на выходе второго дешифратора 3 (т.е. вновь происходит смена фазирующей комбинации). Вновь срабатывает блок 6 проверки чередования кодов, вследствие чего запуск рас- 55 пределителя 11 импульсов осуществляется на прежних временных позициях, а во второй накопитель 9 записьшает- ся вторая единица.

В случае, если пробный запуск распределителя 11 импульсов осуществлен случайно комбинацией, аналогичной фазирующей, в следующем цикле принимаемых элементов сообщения на прежних временных позициях располо- 15 жена другая комбинация, отличная от фазирующей, вследствие чего вторичный пробный запуск распределителя 11 импульсов через второй элемент ИЛИ 14, второй элемент НЕТ 15, третий элемент ИЛИ 10 на прежних временных позициях не происходит и устройство продолжает находится в состоянии по- . иска комбинации, аналогичной фазирующей .

В случае многократного циклического повторения одной и той же информации в нескольких циклах подряд и при первоначальном пробном запуске распределителя от случайной комбинации, аналогичной фазирующей, эта же комбинация вновь выделяется тем же дешифратором (например, вторым) на прежних временных позициях спустя цикл работы распределителя 11 импуль- 35 сов. Однако вторичный пробньш. запуск распределителя 11 импульсов на прежних временных позициях в этом случае не происходит, так как сигнал с выхода одн овибратора 16 запрещает прохождение сигналов пробного запуска через третий элемент И 17 по его первому входу (длительность запрещающего сигнала на выходе одновибратора 16 равна сумме длительности принимаемого цикла сообш;ений и длительности одного элемента сообщения).

&:

Формула изобретения

Устройство цикловой синхронизации по авТ. св. № 1259504, о т л и ч а ю- ы; е е с я тем, что, с целью сокращения времени установления циклового фазирования, введены последовательно соединённые второй элемент ИЛИ, второй элемент НЕТ, одновибратор и третий элемент И, выход которого подключен к третьему входу первого элемента ИЛИ, а к второму входу третьеФормула изобретения

Устройство цикловой синхронизации по авТ. св. № 1259504, о т л и ч а ю- ы; е е с я тем, что, с целью сокращения времени установления циклового фазирования, введены последовательно соединённые второй элемент ИЛИ, второй элемент НЕТ, одновибратор и третий элемент И, выход которого подключен к третьему входу первого элемента ИЛИ, а к второму входу третье71341727

го элемента И подключен выход второго теля, при этом выходы первого и вто- элемента НЕТ, к второму входу кото- рого элементов И подключены к входам рого подключен выход второго накопи- второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Приемник синхросигнала | 1981 |

|

SU1092745A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

Изобретение относится к передаче данных и сокращает время установления 1:щклово го фазирования. Устройство содержит регистр 1 сдвига, дешифраторы 2 и 3, элементы И 4,, блок 6 проверки чередования кодов, элементы НЕТ 7 и 15, накопители 8 и 9, элементы ИЛИ 10 и 14, распределитель 11 импульсов, блок 12 выделения тактовой частоты, кодовый преобразователь 13, -одновйбратор 16. 1 ил. S (О to 14)

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-30—Публикация

1980-11-12—Подача