Изобретение относится к импульсной технике и может найти применение при построении интегральных схем на в:}аимодополняю1цих МДП-транзисторах.

Цель изобретения - снижение потребляемой мощности за счет ограничения величины напряжения, до которого осуществляется предварительный заряд емкости внутренних узлов логического элемента без уменьшения перепада уровней выходного сигнала.

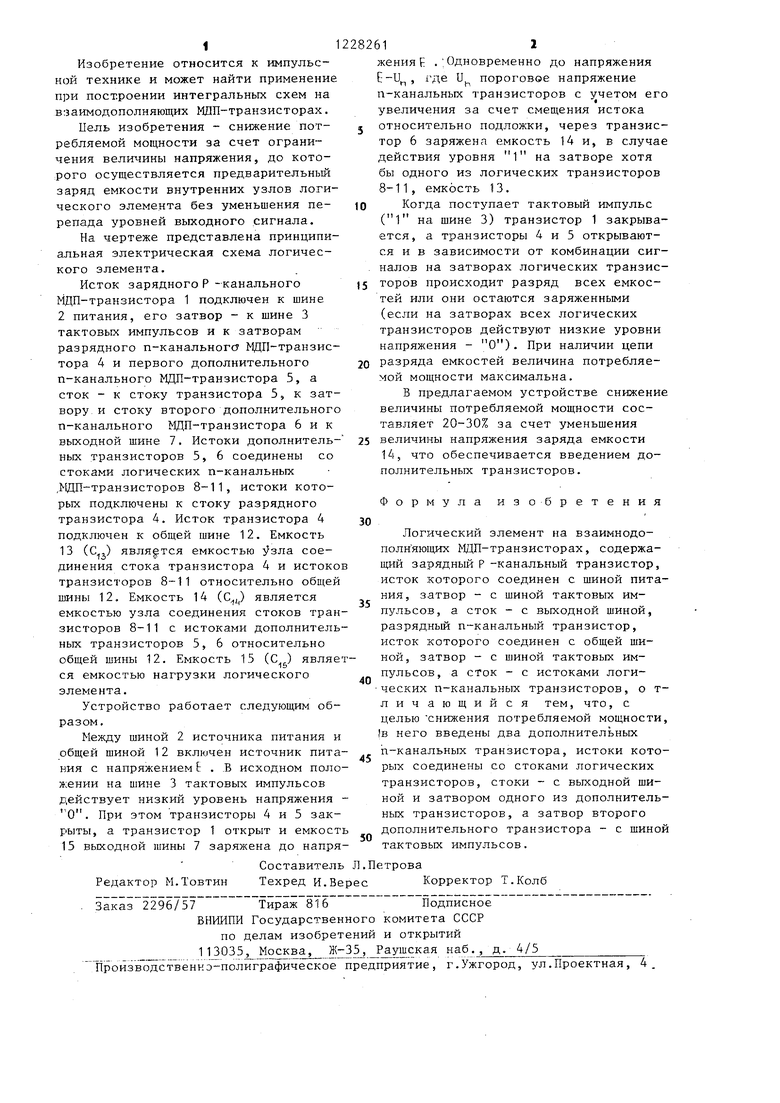

На чертеже представлена принципиальная электрическая схема логического элемента.

Исток зарядного Р -канального МДП-транзистора 1 подключен к шине 2 питания, его затвор - к шине 3 тактовых импульсов и к затворам разрядного п-канальногс ЩГ1-транзис- тора 4 и первого дополнительного п-канального МДП-транзистора 5, а сток - к стоку транзистора 5, к затвору, и стоку второго дополнительного п-канального ВДП-транзистора 6 и к выходной шине 7. Истоки дополнительных транзисторов 5, 6 соединены со стоками логических п-канальньгх ЩП-транзисторов 8-11, истоки которых подключены к стоку разрядного транзистора 4. Исток транзистора 4 подключен к общей шине 12. Емкость 13 () является емкостью узла соединения стока транзистора 4 и истоко транзисторов 8-11 относительно общей шины 12. Емкость 14 () является емкостью узла соединения стоков транзисторов 8-11 с истоками дополнительных транзисторов 5, 6 относительно общей шины 12. Емкость 15 (С являеся емкостью нагрузки логического элемента.

Устройство работает следующим образом.

Между шиной 2 источника питания и общей шиной 12 включен источник питания с напряжением t . .В исходном положении на шине 3 тактовых импульсов действует низкий уровень напряжения О. При этом транзисторы 4 и 5 закрыты, а транзистор 1 открыт и емкост

50

выходной шины 7 заряжена до напряСоставитель Л.Петрова Редактор М.Товтин Техред И.Верес Корректор

Логический э полн яющих ВДП-т щий зарядный Р исток которого ния, затвор - с пульсов, а сток разрядный п-кан исток которого ной, затвор - с пульсов, а сток ческих п-каналь личающий целью снижения IB него введены п-канальных тра рых соединены с транзисторов 5 с ной и затвором ных транзисторо дополнительного тактовых импуль

Заказ 2296/57 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035 Москва , PJlyшcкaя наб. , д. 4/5

Пройзв одственнэ-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

5

0

5

0

5

0

5

0

женияf .;Одновременно до напряжения Е-и, 1 де и пороговое напряжение п-канальных транзисторов с учетом его увеличения за счет смещения истока относительно подложки, через транзистор 6 заряжена емкость 14 и, в случае действия уровня 1 на затворе хотя бы одного из логических транзисторов 8-11, емкость 13.

Когда поступает тактовый импульс (1 на шине 3) транзистор 1 закрывается, а транзисторы 4 и 5 открываются и в зависимости от комбинации сигналов на затворах логических транзисторов происходит разряд всех емкостей или они остаются заряженными (если на затворах всех логических транзисторов действуют низкие уровни напряжения - О). При наличии цепи разряда емкостей величина потребляемой мощности максимальна.

В предлагаемом устройстве снижение величины потребляемой мощности составляет 20-30% за счет уменьшения величины напряжения заряда емкости 14, что обеспечивается введением дополнительных транзисторов.

Формула изобретения

Логический элемент на взаимнодо- полн яющих ВДП-транзисторах, содержащий зарядный Р канальный транзистор, исток которого соединен с шиной питания, затвор - с шиной тактовых импульсов, а сток - с выходной шиной, разрядный п-канальный транзистор, исток которого соединен с общей шиной, затвор - с шиной тактовых импульсов, а сток - с истоками логических п-канальных транзисторов, о т- личающийся тем, что, с целью снижения потребляемой мощности, IB него введены два дополнительных п-канальных транзистора, истоки которых соединены со стоками логических транзисторов 5 стоки - с выходной шиной и затвором одного из дополнительных транзисторов, а затвор второго дополнительного транзистора - с шиной тактовых импульсов.

. Колб

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Устройство автоматического смещения | 1981 |

|

SU995673A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Тактируемый триггер на комплементарных МДП-транзисторах | 1985 |

|

SU1499435A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

Изобретение может быть использовано при построении.интегральных схем на взаимодополняющих МДП-тран- зисторах. Цель изобретения - снижение потребляемой мощности. В исходном положении на шине 3 тактовых импульсов низкий уровень напряжения - лог.О. Транзисторы (Т) 4 и 5 закрыты, а Т 1 открыт и емкость 15 шины 7 заряжена до напряжения Е . Емкость 14 заряжена до напряженияЕ-U , где и„- пороговое напряжение. При лог.1 на затворе хотя бы одного из Т 8-11 емкость 13 имеет заряд, равный заряду емкости 14. При поступлении тактового импульса Т 1 закрывается, а Т 4 и 5 открываются. Происходит либо разряд всех емкостей, либо они остаются заряженными. Введение Т 5 и 6 позволит уменьшить величину заряда емкости 14, что снизит потребляемую мощность на 20-30%. 1 ил. (Л ю Од

| The Electronic Engineer, 1970, V.29, № 5, p.54, Fig.7 CJEEE Journal of Solid - State circuits, 1982, VSC-17, №3, p.615, Fig.3 |

Авторы

Даты

1986-04-30—Публикация

1984-01-13—Подача